搶答器在各類競賽中的必備設備,有單路輸入的,也有組輸入方式,本設計以FPGA 為基礎設計了有三組輸入(每組三人),具有搶答計時控制,能夠對各搶答小組成績進行相應加減操作的通用型搶答器;現行的搶答器中主要有兩種:小規模數字邏輯晶元解碼器和觸發器來做,另外一種用單片機來做;小規模數字邏輯電路比較複雜,用單片機來做隨著搶答組數的增加有時候存在I/O 口不足的情況;本設計採用FPGA 來做增強了時序控制的靈活性,同時由於FPGA 的I/O 埠資源豐富,可以在本設計基礎上稍加修改可以設計具有多組輸入的搶答器。

功能描述

本文設計了一個通用型電子搶答器:三個參賽隊,每個隊有三個成員,各自可手動按按鈕申請搶答權;回到正確加1 分,回答錯誤減1 分,違規搶答減1分,不搶答不加分不扣分;用4 位LED 的左邊2 位顯示搶答組號及搶答計時時間,右邊2 位顯示相應組的成績。

搶答器具體功能如下:

1、可同時進行三組每個小組三人的搶答, 用9 個按鈕Group1_1,Group1_2,Group1_3,Group2_1,Group2_2,Group2_3,Group3_1,Group3_2,Group3_3 表示;

2、設置一個搶答控制開關Start,該開關由主持人控制;只有當主持人按下開始鍵才能搶答;在按開始按鈕前搶答屬於違規;

3、搶答器具有定時搶答功能,且一次搶答的時間設定為30 秒。當主持人啟動"開始"鍵后,用4 位LED 數碼管左邊兩位顯示30s 的倒計時;同時紅色LED燈亮,表明可以搶答。

4、搶答器具有鎖存與顯示功能。即選手按動按鈕,鎖存相應的組號,並在4 位LED 數碼管的左邊兩位顯示,同時用一個綠色LED 指示是否有選手搶答,如果是違規搶答還能用選手蜂鳴器報警提示。搶答實行優先鎖存,優先搶答選手的相應組號和成績一直保持到下一輪搶答開始。

5、參賽選手在設定的時間內進行搶答,搶答有效,數碼管左邊兩位顯示 ”FX”,如果搶答違規則顯示 ”XF”(其中X 表示組號1~3),並保持到下一輪搶答。如果搶答延遲時間已到,無人搶答,本次搶答無效,系統回到主持人按開始前的等待狀態,數碼管上左邊兩位顯示“FF”。

6、當搶答有效后,主持人可以根據搶答選手回答問題正確與否對選手相應組數的成績進行加減分操作,搶答違規也能減分操作,用4 位LED 數碼管右邊兩位顯示相應組數的成績。(注各組初始成績為10 分)

設計架構

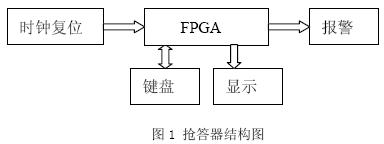

本文以FPGA 為基礎設計的電子搶答器,根據設計功能要求,改設計主要包括搶答輸入鍵盤,數碼管顯示,報警及FPGA 最小系統。搶答器結構簡圖如圖1所示。

1、FPGA 最小系統電路:FPGA 正常工作時的基本電路,由時鐘和複位電路組成。

2、鍵盤輸入電路:用3×3 矩陣鍵盤組成3 個組共9 個人的搶答按鈕。同時包括Start, Add, Sub 三個由主持人控制的單獨按鈕。

3、顯示模塊:用移位寄存器74HC164 驅動4 位共陰數碼管顯示;數碼管要顯示的數據通過74HC164 串列數據埠輸入。

4、報警及相關信息顯示:蜂鳴器電路和LED 燈顯示相關狀態信息指示電路。

各模塊詳細描述

1、FPGA 與各個模塊的介面

本文以XC3S400 為基礎設計的電子搶答器,搶答器實際上是一個人機介面的一個智能設備,該設計中用到的FPGA 外部I/O 口及其與外部各個模塊連接的網路標識如圖2 所示。

圖2.FPGA 的IO 介面

2、按鍵模塊

由於按鍵是機械的動作,按鍵存在電平抖動,為了消除按鍵抖動引起的干擾,需要等按鍵值達到穩定狀態時才讀取按鍵的值,也就是說要當按鍵按下一段時間后,才讀取按鍵值;本設計中搶答開始鍵(Start)、搶答后各組成績的加(Add)和減(Sub)按鍵是以單鍵的形式輸入,按鍵延遲時間為20ms,對於搶答組的按鍵是用3×3 陣列鍵盤實現,row=3’b001 以周期為5.08ms 進行循環左移掃描,掃描完三行的周期為15.24ms,這個就是說只有當兩個按鍵之間的時間間隔在15.24ms 之內時才有可能存在一個按鈕在比另一個按鈕先按,而響應後者;實際操作中,兩人按鍵之間的間隔大於這個時間間隔,因此,不會出現錯誤響應。同時每個按鍵后的延遲等待125.76ms 后此按鍵值才有效;經過實際測試,鍵盤具有消抖功能,能夠正確檢測按鍵值。按鍵電路圖如圖3 所示。

圖3.按鍵電路

圖註: Group1_1,Group1_2,Group1_3 分別表示第一參賽小組的三個成員的按鈕, 依次類推Group2_1,Group2_2,Group2_3 和 Group1_1,Group1_2,Group1_3 分別代表第二和第三參賽小組的三個成員;Start、Add、Sub 分別代表搶答開始按鍵、對小組成績的加操作和減操作按鈕!

3、顯示模塊

顯示模塊由4 位的LED 數碼管顯示搶答組數、是否違規搶答信息、按下搶答鍵后的搶答時間、各組所得分數等信息;其中數碼管左邊2 位顯示搶答組號及搶答計時時間,右邊2 位顯示相應組的成績。數碼管的驅動電路(解碼電路)用兩片74164 控制;電路圖如圖4 所示。

顯示數據信息通過74164 的串列解碼傳送到數碼管對應段,對應位顯示;對於數碼管顯示的時序特別要注意:數碼管是採用動態掃描方式顯示,所有位掃描顯示一次的頻率一定要大於相應位數據改變的頻率;同時當數碼管對於數據改變的同時一定要把相應數據送到數碼管進行顯示,即數據改變和數據顯示要同步;此設計中4 位數碼管動態掃描頻率位190Hz,而數碼管要顯示的搶答組數、搶答組的成績等信息的變化頻率都是秒級,即幾秒鐘或者幾分鐘變化一次,滿足數碼管顯示要求。

圖4.顯示電路

註:數碼管為共陰數碼管,其中pin6,pin8,pin9,pin12 依次為位碼,其餘為段碼;

4、時鐘複位

此模塊用於生成FPGA 系統時鐘和複位電路,採用有源晶振和低電平複位。系統時鐘採用50MHz,能夠滿足電路設計要求,電路如圖5 所示。

圖5.時鐘複位電路

5、報警模塊

報警主要用於響應當沒有按開始鍵之前違規搶答信號;即當違規時蜂鳴器響;同時還增加了一個紅色用於顯示當按下開始鍵的信號;即當主持人按下開始按鍵時,紅色LED 燈亮;同時用一個綠色LED 燈指示有選手按搶答按鈕,選手按鍵搶答,綠色LED 閃爍一次。電路圖如圖6 所示。

圖6.報警和指示

軟體代碼描述

軟體設計主要採用verilog HDL 語言進行設計,採用狀態機對搶答器的各個過程進行控制,設計中採用了層次化和模塊化的思想,即頂層模塊只有一個控制搶答器的主狀態機和模塊例化,然後分別用子模塊實現數碼管顯示,成績多路選擇器,成績的處理模塊,按下搶答開始鍵后的延遲等待模塊,按鍵模塊等。程序流程圖如圖7 所示。

圖7.程序流程圖

圖注: 顯示“FF+成績”中FF 表示無效狀態,成績表示上一次搶答的那個小組的成績;顯示“FX+成績”表示搶答小組答題完並進行評分操作后的組號和成績;顯示“XF+成績”表示違規搶答的那個小組組號及減1分后的成績信息(X 表示1,2,3)。這裡“+”是為了區分組號和成績信息,數碼管並不顯示加號,下同。

用Verilog HDL 分別編寫各個模塊,然後在ISE 環境下運行程序,調試成功。最後生成的頂層模塊的方塊圖如圖8 所示。

圖8.頂層模塊圖

圖註:Line(2:0)和row(2:0)分別表示參賽小組按鍵的輸入陣列信號和輸出掃描陣列信號;start_key,add_key, sub_key,分別代表搶答開始命令,對各組成績的加、減操作命令;dp,error,push_key 分別表示開始鍵按下后的信號,違規搶答信號以及參賽組有人按鍵的響應信號;hc_cp,hc_si 表示顯示解碼晶元74HC164 的串列時鐘和數據信號。

問題與解決

1、狀態機問題

在整體調試的時候,當主持人按開始按鈕后,程序就死在那裡,不能接收搶答信息,由於搶答鍵盤已單獨調試成功,因此懷疑是控制搶答過程的狀態機除了問題,指示進入開始狀態的紅色LED燈一直亮著,說明程序的確死在開始狀態。再次綜合的過程中發現警告提示:狀態機的狀態量的賦值錯誤,把二進位標識“b”誤寫為“h”,這樣由於狀態機數據寬度小於時間數據數據長度,自動取較小位數據;如state_start = 4'b0010誤寫為state_start = 4'h0010,實際就是state_start = 4’b0000,這肯定與前面狀態衝突;同時調試過程中也遇到過複位時沒有把狀態機複位到初始狀態的情況。經過此次設計,體會認識到狀態機在實際控制中的重要性,以後設計中要學會看綜合布線過程中警告信息。

2、信號同步的問題

在搶答器按下開始鍵後有一個等待搶答30s 的延遲時間,當30s 完成後如果三個小組都沒有人按搶答鍵,那麼此次比賽搶答無效,系統自動回到主持人按開始前的系統等待狀態;當計時完成30s 後生成一個高電平的脈衝信號(pulse),由於此脈衝信號高電平持續時間是整個系統的系統時鐘(clk),這個時鐘周期小於狀態機的時鐘周期(clk_4),直接用狀態機的時鐘是檢測不到此脈衝信號,需要把此脈衝信號同步到與狀態機時鐘同步。

採用的方法是:首先用一個鎖存器(pulse_reg)鎖存此脈衝信號(鎖存器時鐘也為系統時鐘),通過鎖存器的輸出值和原脈衝信號寄存器值就可以檢測到脈衝由低電平0 到高電平1 的跳變沿,同樣用一個與系統時鐘同步的鎖存器(flag)鎖存這個跳變沿,當出現這個跳變沿時flag=1;而為了讓狀態機時鐘(clk_4)檢測到flag 信號,同時要在狀態機時鐘檢測到后要把flag 清零,為下一次檢測作準備,這時可以當狀態機時鐘(clk_4)檢測到flag=1’b1 后,同時生成一個flag的清零信號(flag_rst)flag_rst=1’b1;當flag_rst 為1 時把flag 清零。

調試信號同步的部分程序如下:

reg flag_rst; //生成flag_rst 信號

always @ (posedge clk_4 or negedge rst_n)

begin

if(!rst_n)

begin

flag_rst <= 1'b0;

end

else

begin

if(flag == 1'b0)

flag_rst <= 1'b0;

else

begin

flag_rst <= 1’b1;

end

end

end

always @ (posedge clk)

begin

pulse_reg <= pulse;

end

reg flag; //flag 用來檢測pulse 上升沿

always @ (posedge clk)

begin

if(!rst_n)

flag <= 1'b0;

else

begin

if((pulse_reg == 1'b0)&&(pulse == 1'b1))

flag <= 1'b1;

else if(flag_rst == 1'b1)

flag <= 1'b0;

end

end

reg flag_reg; //生成與clk_4 同步的用於檢測脈衝上升沿信號的flag 信號

always @ (posedge clk_4)

begin

flag_reg <= flag;

end

用modesim6.0 模擬波形如下:

圖9.信號的同步的模擬波形

從模擬波形中可以看出當pulse 高電平時的下一個時鐘flag = 1’b1;為了讓時鐘clk_4 能夠檢測到flag = 1’b1,就讓flag 一直保存到clk_4 上升沿出現,然後在clk_4 上升沿把flag 的複位信號flag_rst 置1;然後flag, flag_rst都清零。改變pulse 脈衝出現的時間或者clk_4 的頻率都能檢測到pulse 的高電平。經過信號同步后,狀態機能夠檢測搶答計時完30s 後生成的一個脈衝信號然後回到初狀態。

時序設計是數字電路電路的主要工作,在設計中一定要明白信號如何傳遞,在何時賦值,何時信號值需要改變等,這樣才能更好的設計。在需要改變寄存器值的時刻沒有對寄存器進行操作,會造成結果的錯誤。

設計結果

根據搶答器功能要求,規劃程序包括的子模塊,並編寫Verilog 代碼,在硬體電路上調試運行成功。

操作過程:開始時對,整個系統複位(默認每組成績為10 分),數碼管顯示“FF+10”。在主持人發出開始搶答的Start 之後,參賽隊員就可以按自己前面的搶答按鈕,同時用數碼管左邊兩位計時搶答時間30s,如果在30s 內各組都無人搶答,則此次搶答無效,系統自動回到開始前的初狀態(數碼管顯示“FF+成績”),等待下一次操作;主持人可根據回答爭取與否,以及是否違規搶答,決定加減分(Add 為加分控制,Sub 為減分控制),加減操作后系統又回到開始前的等待狀態。設計中,哪個組搶答,就顯示哪個組的信息。如果搶答沒有違規(按開始后搶答)則顯示器左邊兩位顯示“FX”;反之,則顯示“XF”,X 代表組號1,2,3。按照操作方法,以第1 組搶答為例在VX_SP306 開發平台上運行看看數碼管顯示及整個過程:

1、在系統複位后顯示“FF+10”;

2、等待主持人按開始狀態;

3、主持人按開始按鈕前第1 組搶答,顯示“1F+10”,減1 分操作后顯示“1F+09”;回到步驟2;

4、主持人按開始按鈕后,顯示“30+10”;30 每秒鐘減1 直到00;

5、在30s 內第1 組搶答,顯示“F1+10”,主持人根據回答情況進行加、減分操作,顯示“F1+分數”;然後回到步驟2;

6、如果在30s 內沒有人搶答,顯示“FF+10”,回到步驟2。

[admin via 研發互助社區 ] 基於FPGA的搶答器設計已經有3263次圍觀

http://cocdig.com/docs/show-post-43057.html