OrCAD10.3是OrCAD a Cadence product family 公司於2004年11月推出的電子設計自動化(EDA)軟體系統。其中包括三個主要部分:

- 鎖定元件信息系統的原理圖輸入器(Capture CIS);

- 模擬和混合信號模擬(PSpice A/D)和其高級分析(PSpice –AA);

- 印刷電路板設計(Layout Plus)形成Gerber文件可與Protel等PCB軟體連接;

並與FPGA 設計系統(FPGA Studio)有介面,形成了完整的輸入、分析、編輯和製造的全線EDA輔助設計工具Cadence studio系列化解決方案。OrCAD10.3結構圖如圖2-1所示。現分別介紹如下:

2.1 Capture CIS10.3

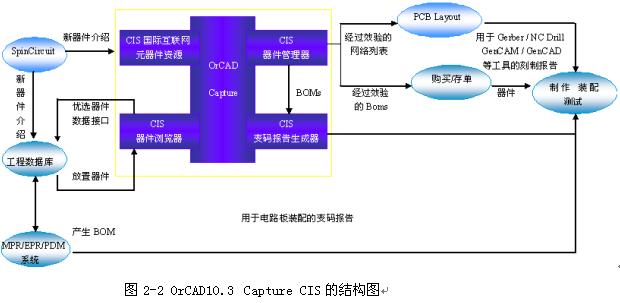

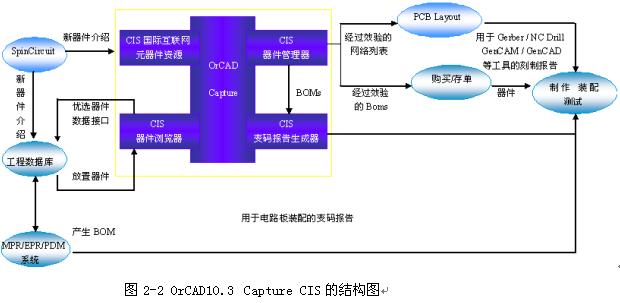

OrCAD Capture由於它能夠提供直觀界面和具有豐富的特點,從而使其成為原理圖設計輸入的工業標準。OrCAD Capture CIS(Component Information System)是內置的元件高級文檔管理系統, 不僅提供Capture的完整功能,更是提供了一個完美的Part Database的管理介面,它可以通過Microsoft Windows 的ODBC介面去連結不同Database,整合Part Database的所有信息。使用這個功能全面的設計輸入工具和管理環境,可以減少查找和手工輸入元器件資料的時間及人為的錯誤。OrCAD 10.3 Capture CIS的結構如圖2-2所示。

- Capture為Cadence studio系統總體輸入器。利用Capture來連結OrCAD Layout、Allegro PCB Layout或其它Layout的軟體,來完成PCB設計;也整合了PSpice與VHDL(NC Verilog)的環境---提供給使用者做模擬與數字(FPGA Design Flow)前端設計平台。另外也可以配合SpecctraQuest來解決高頻問題。

- 導出30種平板和分層格式(電路),可用於電路圖、PSpice、PCB和可編程器件設計,其中導出的PCB Layout軟體的網路表格式包含OrCAD Layout、Allegro、Pads P2K、Mentor Graphics BoardStation等等;

- 在http://www.orcad.com/上提供了72000個啟動資料庫,可以免費下載到Capture CIS中,更彈性的結合所選擇的資料庫,可以在ODBC支持的環境中工作,例如MRP、ERP、PDM等系統或是Microsoft Access or SQL Server 等資料庫。Capture CIS支持小型的設計群組更方便擴充的設定,例如Microsoft 產品(Access),如果在同一個區域的團體需要更高級的Client端Server資料庫管理系統技術可以選擇更複雜的資料庫(SQL);

- 也可以徑直從國際互聯網(www.SpinCircuir.com)搜索和選擇器件,直接拖拉放置到用戶的原理圖頁中而不用退出CaptureCIS。SpinCircuit.com包含了“激活”器件和一百萬個商用和軍用標準器件、製造商、PCB圖形封裝、價格和供貨日期等信息;

- 可以建立完整的組件數據減少以後出錯的風險,提供多重的PLD設計組件與方式,包含Xilinx、Altera、Actel、Lattice、Lucent與Atmel六種Vendor的組件。能更集中管理資料庫的組件避免多餘的組件數據存在;

- 更自動的輸入組件所需要的數據,讓電路圖產生更多有效的數據,更容易與快速的獲得組件數據,生成具有報價水平的元器件清單Netlist、介面等40多種文件,支持所有的公用程序,包括VHDL、Spice、EPIF、PADS和PCAD/Protel/Tango等。能自動打開或轉換SDT Release/V、PSpice和EDIF200、PDIF的設計。

OrCAD Capture CIS 10.3版本的新特色及加強的新功能:

- 產生可分離組件,應用到不同區段的圖表頁,提高圖表頁編輯速度;

- 設定信號屬性參數流程,提高高速電子的運行限制,確保輸出到Allegro PCB編輯設計器的屬性參數文件的正確性和有效性;

- 線路圖航行的新功能:在RMB菜單中運用當前頁(快捷鍵Shift + F10)和下一頁(快捷鍵F10)選項來轉換圖表編輯頁;

- 在替換隱藏對話框中保留參考文件選擇器;

- 新增選擇過濾器,在塊模式選擇操作時,可以運用該工具來控制圖表頁選擇的目標文件等;

- 支持最新的Xilinx及Altera檔案格式;

- 支持Crystal Version 10.0的格式輸出。

2.2 PSpice A/D和PSpice-AA

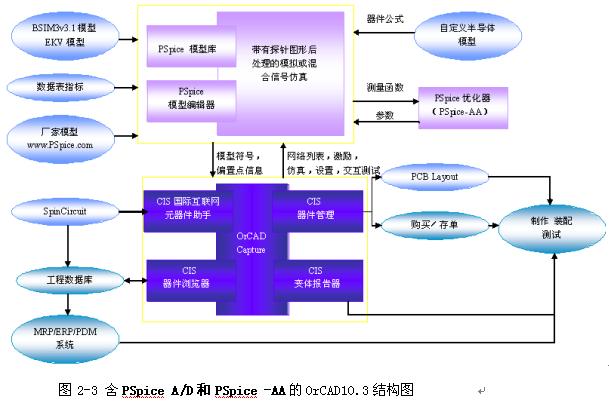

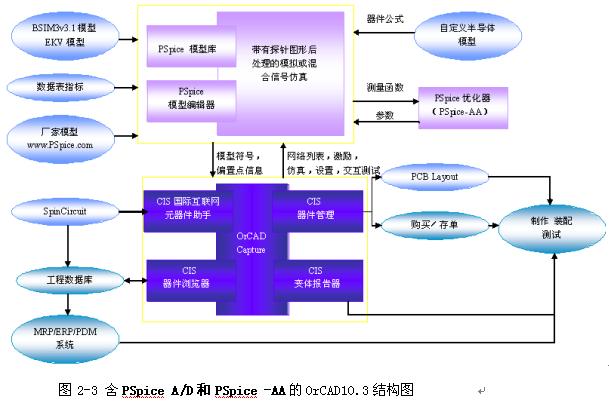

PSpice模擬器是一個全功能的模擬與混合信號模擬工具,它支持從高頻系統到低功耗IC設計的電路設計。自1985年問世以來,經過不斷革新,現已成為工業標準工具。PSpice不是一般意義的教學演示軟體,而是為嚴肅的模擬設計而特性化的模擬器。PSpice工具中提供了內建的Model,包含高頻系統到低功率IC的模擬設計。有方便的Model Editor功能,可自行建立新的組件或是更新,通過模擬完成電路設計。PSpice A/D是其擴展集。使用它可以模擬任何尺寸、包含從IGBTs和脈寬調製器到DACs和ADCs等模擬和數字器件在內的混合信號設計。

PSpice A/A 是新增加的一套高級分析特色工具,這些特色包含Sensitivity、Monte Carlo、Smoke(Stress)、Optimizer、Parametric Plotter Analysis;並在Optimizer的引擎里,新建立多種的演算法。運用Parametric Plotter測量並掃描參數的曲線軌跡。在PSpiceA/D分析完善的基礎上,再用PSpice-AA的五個特色工具進行分析,可以最大程度地提高設計電路的性能、可生產性以及可靠性。其結構圖如圖2-3所示。現簡介如下:

- 可以從16000個PSpice A/D模型庫器件中(其中包括精確傳輸線、磁芯、MOSFET、IGBT、CMOS、ECL、RAM、ROM、PAL、DAC、ADC、PWM以及符合工業標準的BSIM3v3.1和EKV MOSFET等模型)或者從OrCAD Capture CIS巨大的國際互聯網上的元器件庫一百萬個標準元器件中,選擇理想元器件建立通常的原理圖;

- 可以很方便地將PSpice A/D原理圖編輯器導入到OrCAD Capture-PSpice A/D設計、分析環境中;

- 可以創建各種激勵信號:包括模擬激勵(如直流源、交流源、瞬態的正弦源、指數源等)和數字激勵(如信號、時鐘和匯流排等);

- 可以進行各種電路模擬,如直流分析、交流分析、瞬態分析、參數分析、容差分析、溫度分析等,其精確程度主要依賴於器件模型精度的選擇;

- PSpice A/D自動識別A到D和D到A連接,並插入介面子電路和電源,如此處理后可以再現模擬和數字器件的物理連接;

- PSpice A/D包括了Xilinx的所有產品庫,其獨特的FPGA和數/模混合設計能力,能便捷的進行印刷電路板設計;

- 模擬模擬方法和事件驅動法的數字模擬綜合利用,從而提高了模擬的速度,而不會降低精度;

- PSpice優化器(PSpice Optimizer)在指定可變的參數和要優化的性能指標下進行優化,即PSpice-AA這是新版更新最多的一塊(對Parameter及Specifications的個數無限制)。

OrCAD PSpice 10.3版本的新特色及加強的新功能:

- 支持Monte Carlo歷史的數據輸出,可以方便快捷的編輯模型參數值;

- 在PSpice新增可以載入波形的功能,運用輸入波形對話框在.txt 或者.csv文件格式中輸入添加的曲線波形;

- 新增PSpice SLPS介面,PSpice SLPS 介面是在 MathWorks' MATLAB/ Simulink 系統模擬器和 OrCAD PSpice A/D 電路模擬器之間的一個介面工具,運用該介面能順利的完成兩者之間的模型電路轉換;

- 可查看版本的信息程序,在幫助菜單下可以查看所有OrCAD產品的信息和工作流程,利用信息程序可以檢查排除故障信息;

- 支持模擬模擬的電池模型(Battery Model),在Capture設計中新增了awblead_battery 和 awbflooded_battery模型;

- 進一步加強PSpice model,支持最新GaAsFET的TOM3模型和BSIM NLEV模型;

- 進一步加強Probe功能。

2.3 Layout Plus

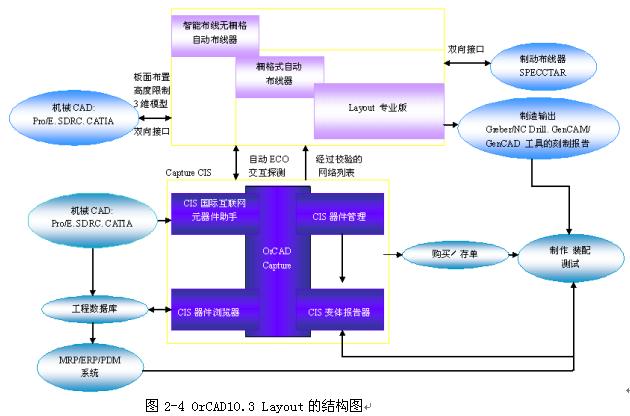

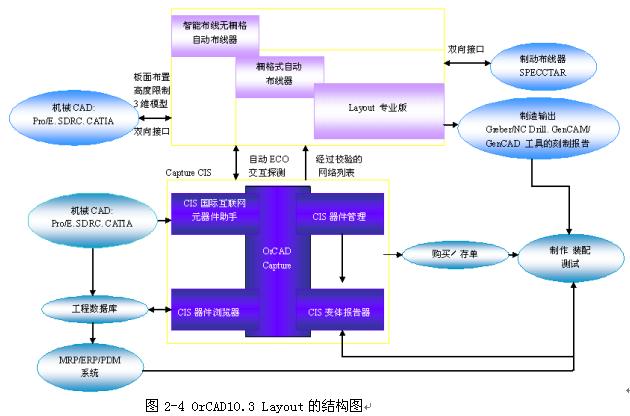

該產品包含了OrCAD Layout的所有特徵,並包括一個無柵格自動布線器。它適用於:設計複雜、高密度、混合間距、多層

電路板;設計具有大模擬容量的電路板;具有高產量的工程部門。OrCAD10.3 Layout的結構圖如圖2-4所示。現簡介如下:

- 用Capture CIS自動獲取元器件數據,當Capture變更其電路設計Layout可以透過AutoECO功能達到與Capture一起變更的目的,OrCAD Capture/Layout 提供了更強大的整合功能;

- 可以更容易的使用組件編輯器來製作出不同的組件符號, 利用區塊編輯的方式提供快速且容易評估的走線設計;

- 新增的組件精靈可以提供更方便的建立、識別組件文件,包括IPC-D-356/A、 Gerber、Drill、Mill、HPGL、DXF等格式文件均可查看、編輯、修改;

- 有與機械CAD系統介面,可以將如Pro/ENGINEER,SDRC,CATIA和 Solid Edge的數據導入到Layout中,並將電路板輪廓、高度等數據放進PCB資料庫中。待放置好元器件后,用戶可將設計返回機械系統進行3維建模;

- 與其它Cadence工具有介面,為實現高速的數字設計,可通過Layout 內含的Cadence SPECCTR自動布線器將數據轉到Cadence,完成FPGA、SPLD等設計和製造。

OrCAD Layout 10.3版本的新特色及加強的新功能:

- 改進Layout 到 SPECCTRA介面,運用自動布線器SPECCTR解決手工創建.DO文件的問題,生成的報告文件可以更全面的解決PCB設計過程的信息處理問題;

- 支持零件群組設定最多到265個零件群組。

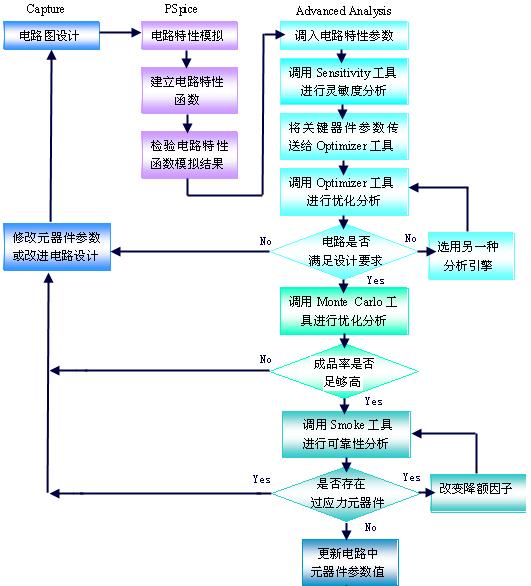

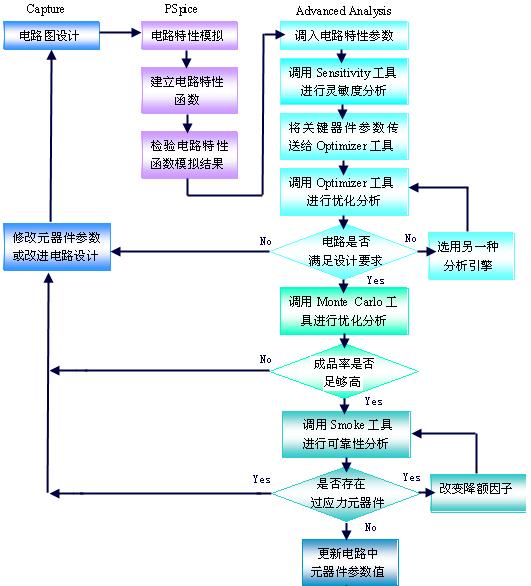

2.4 PSpice–AA的工作流程

PSpice –AA的特色工具原是包含在基於UNIX平台上工作的AWB中,現在提供給基於Windows平台上工作的PSpice 用戶使用。PSpice–AA的工作流程示意圖如圖2-4所示。

- 在完成經典PSpice分析后必須為相應元器件設置高級分析參數,然後才能進入PSpice–AA。

- 通常情況是先進行靈敏度(Sensitivity)分析:以便確定電路中對電路特性影響最大的關鍵元器件參數。

- 針對這幾個關鍵元器件參數,調用參數優化(Optimizer):進行優化設計,優化關鍵元件參數。

- 由於優化設計所得的優化元件參數還是一種標稱值設計,而實際採用的各個元器件不可能都是標稱值,具有一定的分散性。調用蒙特卡洛(Monte Carlo)分析:預測電路成品率,分析其可生產性。

- 滿足上述要求的條件下,還需要檢查電路中是否存在個別元件受到超出其安全工作條件的應力作用。如出現這種情況會降低電路的可靠性。因此,設計最後一關時,就需要調用熱電應力分析(Smoke冒煙報警):提高電路的可靠性。

用PSpice–AA通過這些環節設計出來的電路,才算是電路性能優越、具有較高成品率、適於批量生產的安全可靠電路。