這裡把模擬單獨編號

1) 新建工程

2) 生成原文件

手段CORE Generator Module

Language Templates

3) check syntax

① Behavioral simulate

我覺得從Synthesis and Simulation Design Guide 文件看,應該先RTL Simulation (that is, Behavioral simulate )。其實沒

有關係,綜合和RTL 模擬的順序無所謂,這兩個不一定要誰在前

己見:注意跑行為模擬前是不需要綜合的,僅是RTL 代碼模擬

參考:[In-Depth Tutorial] Chapter 4 P91

4) Synthesis

步驟:Entering Constraints (xcf 格式) -> Entering Synthesis Options -> Synthsizing

參考:[In-Depth Tutorial]P43-P50

我覺得這裡的constraints 是 synthesis constraints:

《cgd》p18

已見:

參《Xilinx ISE 9.X FPGA/CPLD 設計指南(人民郵電)》P31

綜合是把HDL 描述轉化為使用基本門電路以及廠家庫提供的基本單元進行描述的網表(Netlist)的過程。

綜合時需要附加一定的約束,指導綜合過程的進行,最常用的約束有管腳位置約束和附加時序約束

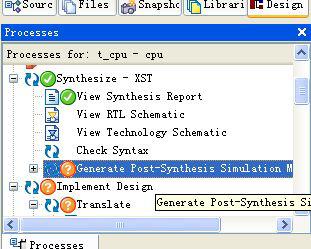

② Post- Synthesis Simulation

這裡以《夏宇聞》第17 章的設計為例,前面行為模擬時可以直接模擬cputop 模塊(專為模擬寫的,不可綜合),但在synthesize 時,必須把cpu 模塊Set as Top Module,因為cputop 模塊是不可綜合的,然後點擊Generate Post-Synthesis Simulation Model,可以注意到原文件夾下會生成netgen 文件夾,打開會發現有synthsis 文件夾,裡面有cpu_synthesis.v文件,這個文件是專門用來模擬的。

但是這裡好像無法直接在ISE 中做綜合后模擬,然後用MODELSIM,可以建工程,添加頂層測試文件cputop.v 等,然後注意僅需要添加cpu_synthesis.v 文件即可,不需要加cpu.v 及其子文件。

問題注意:

1 原測試文件中cputop.v 中諸如寫法“t_cpu.m_alu.opcode”寫法現要改成t_cpu.opcode,因為現在模塊層次關係被打散了,不再有原模塊間關係。

2 在vsim 時要同時選中你的top 層設計和glbl,一起模擬,否則模擬時會出現錯誤信息“Unresolved reference to 'glbl'”

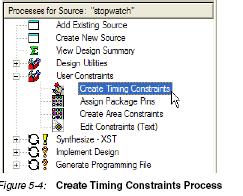

5) (生成分區)、時序約束

Using the Constraints Editor

參考:[In-Depth Tutorial]P116

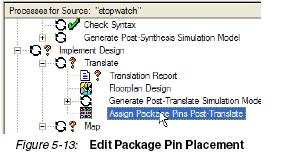

6) translate the design

輸入文件:

輸出文件:

作用:把所有的netlist 和design constraint 合併到一起,生成一個ngd 文件供map 工具使用

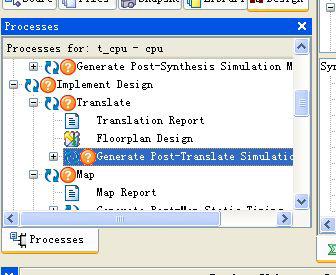

③ Post- Translate Simulation

不點擊Generate Post-Translate Simulation Model,則Sources for 中Post-Translate Simulation 是沒有內容的。

運行之後文件夾netgen 中會有文件夾translate,其中有文件cpu_translate.v,接下來類似cpu_synthesis.v 方法

7) 管腳分配

工具Floorplan Editor

參考:[In-Depth Tutorial]P120

[admin via 研發互助社區 ] ISE 詳細步驟、作用及其理解已經有4637次圍觀

http://cocdig.com/docs/show-post-42987.html