隨著信息技術技術的飛速發展,ARM技術方案架構作為一種具備低功耗、高性能、以及小體積等特性的32位嵌入式微處理器,得到了眾多的知識產權授權用戶,其中包括世界頂級的半導體和系統公司。目前已被廣泛的用於各類電子產品,汽車、消費娛樂、影像、工業控制、海量存儲、網路、安保和無線等領域。被業界人士認為,基於ARM的技術方案是最具市場前景和市場優勢的解決方案。

現場匯流排CAN是為解決現代汽車中眾多的電控模塊之間的數據交換而開發的一種串列通信協議。由於其具有多主站依據優先權進行匯流排訪問,採用非破壞性匯流排仲裁,可完成對通信數據的錯誤檢驗和優先順序判別,數據長度最多為8個位元組,傳輸時間短,受干擾的概率低,抗干擾能力較強,通信速率最高可達1Mbit/s 等特點,它被廣泛應用在汽車,工業,消費類電子等領域,而被公認為是最有前途的現場匯流排之一。

基於ARM在嵌入式系統方面優勢和CAN匯流排的廣泛應用,目前越來越多的ARM處理器內部都自帶了CAN控制器,極大的方便了開發人員對CAN匯流排的開發。但目前仍有些產品中的ARM處理器沒有內置CAN控制器,為了能夠適應節點間對數據傳輸所提出的實時性,可靠性的要求,同時又不改變原來的硬體結構,通過外擴CAN介面模塊來實現CAN通信成了一個較為合適的選擇。

本文基於ARM7TDMI-S處理器LPC2131,對內部沒有集成CAN控制器的處理器,設計了較為通用的CAN介面模塊的硬體電路,並對CAN匯流排進行了可靠性設計,而且對基於嵌入式實時操作系統uCOS-II實現CAN通信,進行了嵌入式軟體的設計,最終在實踐中對CAN匯流排通訊的可靠性和可行性進行了驗證。

LPC2131

Philips LPC2131 是基於ARM7TDMI-S 的高性能32 位RISC 微控制器,它一方面具有ARM處理器的所有優點:低功耗、高性能;同時又具有較為豐富的片上資源,非常適合嵌入式產品的開發。其特點如下:

·集成了Thumb 擴展指令集。

·32KB可在系統中編程(ISP)的片內Flash和可在應用中編程(IAP)的8KB RAM,具有向量中斷控制器。

·2個UART,2個I2C 串列介面,2 個SPI串列介面,2 個定時器(7 個捕獲/ 比較通道),PWM單元可提供多達6個PWM輸出,8通道10位ADC,實時時鐘RTC,看門狗定時器WDT,48 個通用I/O引腳。

·CPU時鐘高達60MHz,具有片內晶體振蕩器和片內PLL。

LPC2131內部沒有集成CAN控制器,而無法利用CAN 匯流排來進行通訊。為了使得LPC2131能夠利用CAN匯流排進行通訊,可以通過外部擴展來拓展其功能。

硬體電路設計

由於LPC2131 是由3. 3 V 供電的ARM7TDMI-S微處理器,其各個IO引腳是3.3V的TTL電平,而且可以承受5V的電壓。而獨立CAN控制器SJA1000是5V供電,其各個IO口的電平是5V的TTL電平,所以二者兼容,其IO可以直接相連。

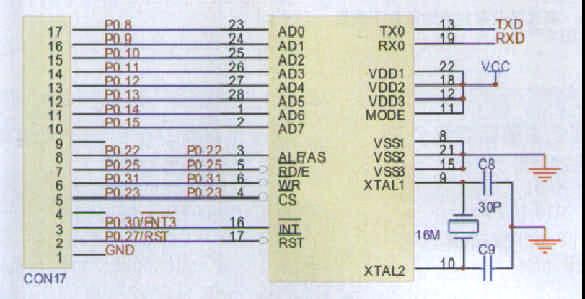

LPC2131 與CAN 控制器介面

LPC2131與CAN控制器介面如圖1所示,LPC2131的P0.8~P0.15與SJA1000的AD0~AD7直接相連實現數據交互,P0.22,P0.25,P0.31,P0.23 分別與SJA1000 的ALE/AS,RD/E,WR,CS 相連實現讀寫和片選,P0.30,P0.27分別與SJA1000 的INT,RST 相連實現中斷和複位。LPC2131 訪問SJA1000 時,可通過軟體模擬SJA1000中所規定的讀寫時序來進行,SJA1000的模式引腳MODE通過VCC而置為高電平,使得SJA1000 工作在Intel 的模式。

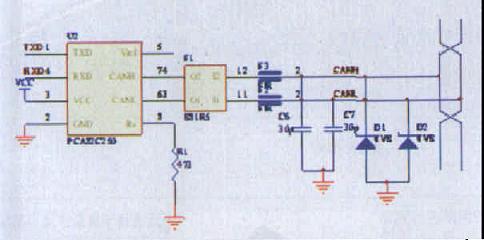

CAN 收發器與CAN 匯流排介面

CAN收發器與CAN匯流排的介面如圖2所示,其中SJA1000 的TX0,RX0 分別與CAN收發器的TXD,RXD相連,為提高CAN收發器82C250與CAN匯流排的介面部分的抗干擾能力,特在82C250 的CANH 和CANL 引腳串接一個共模扼流圈,以消除一定的共模干擾,而使得匯流排差分信號能夠順利通過。並且CANH和CANL分別通過一個磁珠與匯流排相連,以起到消除一定的高頻干擾。同時CANH 和CANL與地之間並聯了兩個30pf 的小電容,可以起到濾除匯流排上的高頻干擾和一定的防電磁輻射的能力。另外在兩根CAN匯流排接入端與地之間分別接了一個TVS,當CAN 匯流排有較高的電壓時通過TVS的擊穿而接地,可起到一定的過壓保護作用。82C250 的Rs 引腳上接有一個斜率電阻以降低CAN匯流排的向外輻射。對於其他無內置CAN控制器的能夠承受5V 的TTL 電平的處理器來說,只需改變與SJA1000的數據埠ALE/AS,RD/E,WR,CS,INT,RST相連接的引腳即可完成外擴CAN介面的硬體設計工作,否則在兩者之間加一個邏輯電平轉換的器件即可。

軟體設計

對SJA1000 的讀寫訪問

由於LPC2131的48個引腳全是IO,所以首先需要通過軟體模擬讀寫SJA1000的時序,來對SJA1000進行操作,進而完成CAN通訊功能。

依據SJA1000在Intel模式下的讀寫時序,可編寫LPC2131 通過CAN控制器SJA1000 發送數據的寫函數void WriteCan(uint8 Addr,uint8 Data)和接受CAN控制器所接受的數據的讀函數uint8 ReadCan(uint8 Addr), 其中Addr 為SJA1000相應的寄存器的地址,Data為LPC2131所發送的數據,讀函數ReadCan可返回所接受的數據。

CAN 通訊的實現

要實現一個CAN通訊需要實現3個功能模塊:對SJA1000的初始化模塊;數據發送模塊;數據接受模塊。

·對SJA1000 的初始化模塊

在開始通訊之前,首先要在SJA1000的各個功能寄存器進行設置,包括模式寄存器,波特率,時鐘分頻器,中斷使能寄存器,濾波寄存器,輸出控制寄存器。

uint8 IniSJA1000(uint8 BTR0,uint8 BTR1)

{

IO0CLR=CS; //片選SJA1000

WriteCan(0,0x09); //進入複位模式

WriteCan(31,0xe8); //設置時鐘分頻器

WriteCan(4,0xfd); //設置中斷使能寄存器

WriteCan(16,AcceptCode1);//設置驗收代碼1

WriteCan(17,AcceptCode2);//設置驗收代碼2

WriteCan(18,AcceptCode3);//設置驗收代碼3

WriteCan(19,AcceptCode4);//設置驗收代碼4

WriteCan(20,MaskCode1); //設置驗收屏蔽1

WriteCan(21,MaskCode2); //設置驗收屏蔽2

WriteCan(22,MaskCode3); //設置驗收屏蔽3

WriteCan(23,MaskCode4); //設置驗收屏蔽4

WriteCan(6,BTR0); //設置匯流排時序寄存器1

WriteCan(7,BTR1); //設置匯流排時序寄存器2

WriteCan(8,0xfa); //設置輸出控制積存器

WriteCan(0,0x08); //進入操作模式

OSCANMbox=OSMboxCreate(0);//建立CAN 通訊郵箱

if (OSCANMbox==NULL)

{

return FALSE;

}

return TRUE;

}

·數據發送模塊

假設要發送的數據的ID存儲在數組ID[4]中,數據存儲在數組SendData[8]中,其發送模塊程序如下所示,其中參數DLC為發送的位元組數,FF為幀類型,即0為數據幀,1為遠程幀。

void Tx(uint8 DLC,uint8 FF)

{

uint8 i;

OS_ENTER_CRITICAL();

If (FF==0x01)

{

WriteCan(16,DLC+0x80); //數據幀

}

else

{

WriteCan(16,DLC+0xd0); //遠程幀

}

WriteCan(17,ID[0]);

WriteCan(18,ID[1]);

WriteCan(19,ID[2]);

WriteCan(20,ID[3]); //TX標識碼

for (i=0;i<DLC;i++)

WriteCan(21+i,sentdata[i]); //TX數據

WriteCan(1,0x01);//設置發送寄存器發送

OS_EXIT_CRITICAL();

}

·數據接受模塊

根據電路圖1,採用中斷接受的方式來接受數據,LPC2131 的P0.30 設置為外部中斷3,整個數據接受模塊由數據接受函數void ReceiveData(uint8 *Rt)、中斷處理函數Can_Exception(void)構成。當SJA1000 接受到CAN匯流排數據,通過接收中斷使得LPC2131產生外部中斷3而使其進入中斷處理函數,進而對接受到的數據進行處理。其中數據接受函數和中斷處理函數如下:

void ReceiveData (void)

{

uint8 i, err,*Rt;

OS_ENTER_CRITICAL();

Rt=(uint8 *)OSMboxPend(OSCANMbox,0,&err);

//通過郵箱接受數據

for (i=0;i<13;i++)

ReceiveData[i]=*Rt++; //將接受到的數據存在全局變數中供後續處理

OS_EXIT_CRITICAL();

}

void Can_Exception(void)

{

uint8 temp[13],i;

OS_ENTER_CRITICAL();

for (i=0;i<13;i++)

temp[i]=ReadCan(16+i); //讀取CAN 數據

OSMboxPost(OSCANMbox,(void *)temp); //將CAN 數據以郵箱發送到接受函數

EXTINT=0x08; //清除ENT3

VICVectAddr=0; //中斷返回

OS_EXIT_CRITICAL();

}

結語

以ARM晶元作為主控制器,CAN匯流排作為數據傳輸方式來進行通訊的嵌入式系統得到了越來越廣泛的應用。同時CAN通訊的可靠性也成為影響系統性能的關鍵部分之一。本文以LPC2131為例,給出了一類微處理器與CAN控制器SJA1000 之間的較為通用的硬體連接方法,對CAN匯流排進行了可靠性設計,並基於嵌入式實時操作系統uCOS-II進行了CAN通訊軟體開發,該設計現已在工廠車間中的分散式監控系統中得到了應用,運行可靠、穩定。

[admin via 研發互助社區 ] 基於LPC2131 嵌入式系統的CAN 模塊設計與實現已經有2364次圍觀

http://cocdig.com/docs/show-post-42190.html