D觸發器CD4013組成的脈衝寬度檢測電路圖

D觸發器CD4013組成的脈衝寬度檢測電路圖 D觸發器的常規使用一般是用作二分頻器、計數器或移位寄存器。然而,只要對D觸發器的外圍電路加以改進,根據其基本邏輯功能。就可充分發揮其獨特的作用。數字裝置中常用的脈衝寬度檢測電路,對脈衝信號的寬度進行識別,例如,當輸入脈衝的寬度為一個特定值時。便產生一個響應,否則就不予響應。以下就用CMOS雙D觸發器CD4013組成的幾種脈衝寬度檢測電路作一介紹。

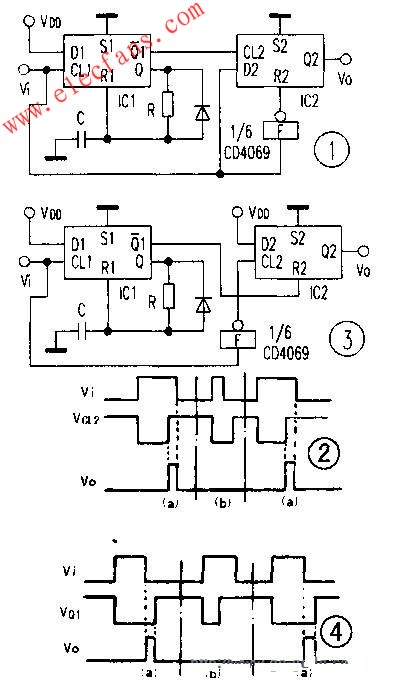

檢測線路之一如圖l所示。ICl、IC2為一片CD4013,其中ICl構成一單穩態觸發器,單穩態輸出端Q1作為D觸發器IC2的時鐘脈衝,Q2端作vo輸出端。由於ICl、IC2的置位S端接地,故穩態時ICl的Ql端恆為零,Ql端為高電平,VO輸出為低電平。當Vi輸入信號為高電平時,將Dl端的高電平送入ICl觸發器,Ql端跳變為高電平,Ql端為低電平,暫穩態開始,IC2觸發器不觸發,VO仍為低電平。當Vi下眺時,ICl單穩電路的暫穩態還未結束(見圖2b所示),IC2觸發器仍未觸發,VO為低電平。待ICl的暫穩態結束,ICI觸發器複位,Ql端為低電平,Ql端上眺為高電平。儘管IC2的CL2端上眺。但由於此時Vi輸入信號已為低電平,經反相器F反相使IC2的複位端R2為高電平,故VO端仍為低電平。

另一種情況是:當Vi為高電平,Ql端為低電平時,ICl暫穩態開始,VO為低電平。當ICl的暫穩態結束時,Vi仍為高電平(見圖2a所示),Ql端上跳,IC2觸發翻轉,R2端處於低電平,D2端的高電平送入IC2,VO端輸出高電平。當Vi下跳時,經F使IC2的R2端為高電平,迫使IC2複位。VO輸出為低電平。

由此可見,只有當Vi輸入信號脈衝寬度大幹ICl的單穩態輸出脈寬時。IC2觸發器才有輸出。

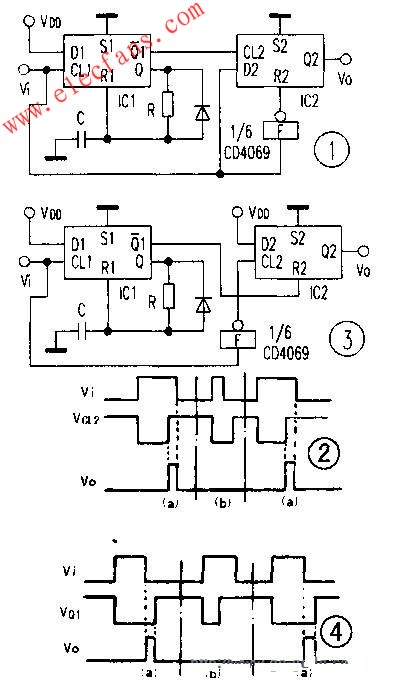

檢測線路之二如圖3所示。該線路和圖1相似,不同的是Vi輸入信號經反相器F反相後作為IC2的CL2時鐘脈衝。ICl仍為一單穩電路。穩態時,V0為低電平。當Vi為高電平時,Ql端為高電平,暫穩態開始,IC2未觸發,V0為低電平。當ICl單穩態結束時(見圖4b所示),Ql端回復到低電平,此時Vi仍為高電平,故VO為低電平。當Vi下跳時,經F反相使。IC2的LC2端上跳,但由於Ql端即ZC2的R2端為高電平,所以VO仍為低電平。