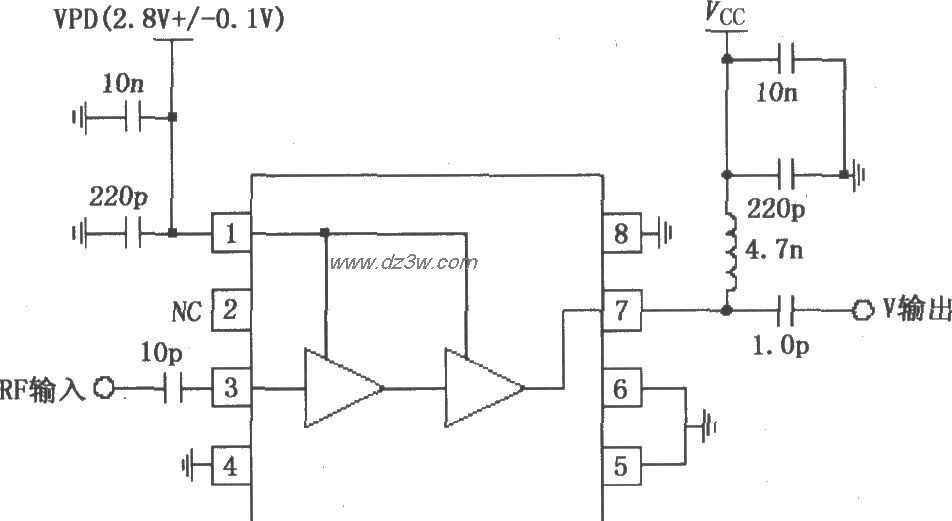

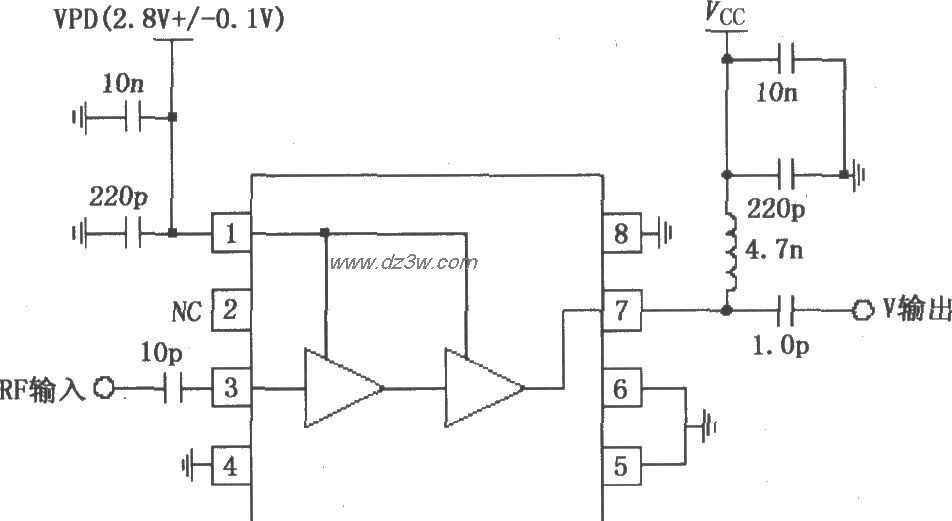

如圖所示為由RF2324構成的1880MHz內部集電極偏置放大器應用電路。射頻信號(RF)由3腳輸入,經過前置放大器、末級功率放大器放大後由7腳輸出。3腳與內部放大器直接耦合,因此外加一個10pF的隔直耦合電容,在1880MHz工作時匹配阻抗為50Ω。7腳為集電極開路的輸出端,可以通過扼流圈或匹配電感接到電源Vcc,該腳典型匹配阻抗為50Ω,外接輸出匹配網路使放大器輸出阻抗與之匹配,以獲得最大輸出功率和效率。1腳為功率降控制端。當VPD=2.8V±0.1V時(IPD典型值為8.5mA)電路工作;當VPD<0.9V時電路關閉。VPD要求外加RF旁路電路。