射頻(RF)電路的電路板布局應在理解電路板結構、電源布線和接地的基本原則的基礎上進行。本文探討了相關的基本原則,並提供了一些實用的、經過驗證的電源布線、電源旁路和接地技術,可有效提高RF設計的性能指標。考慮到實際設計中PLL雜散信號對於電源耦合、接地和濾波器元件的位置非常敏感,本文著重討論了有關PLL雜散信號抑制的方法。為便於說明問題,本文以MAX2827 802.11a/g收發器的PCB布局作為參考設計。

設計RF電路時,電源電路的設計和電路板布局常常被留到了高頻信號通路的設計完成之後。對於沒有經過認真考慮的設計,電路周圍的電源電壓很容易產生錯誤的輸出和雜訊,這會進一步影響到RF電路的性能。合理分配PCB的板層、採用星型拓撲的Vcc引線,並在Vcc引腳加上適當的去耦電容,將有助於改善系統的性能,獲得最佳指標。

電源布線和旁路的基本原則

明智的PCB板層分配便於簡化後續的布線處理,對於一個四層PCB板(WLAN中常用的電路板),在大多數應用中用電路板的頂層放置元器件和RF引線,第二層作為系統地,電源部分放置在第三層,任何信號線都可以分佈在第四層。第二層採用連續的地平面布局對於建立阻抗受控的RF信號通路非常必要,它還便於獲得儘可能短的地環路,為第一層和第三層提供高度的電氣隔離,使得兩層之間的耦合最小。當然,也可以採用其它板層定義的方式(特別是在電路板具有不同的層數時),但上述結構是經過驗證的一個成功範例。

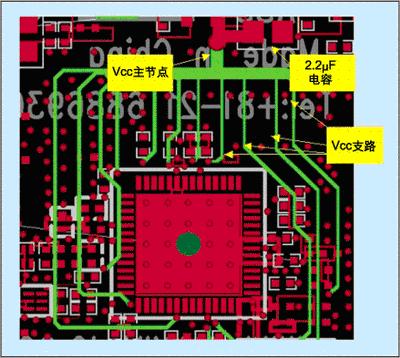

大面積的電源層能夠使Vcc布線變得輕鬆,但是,這種結構常常是引發系統性能惡化的導火索,在一個較大平面上把所有電源引線接在一起將無法避免引腳之間的雜訊傳輸。反之,如果使用星型拓撲則會減輕不同電源引腳之間的耦合。圖1給出了星型連接的Vcc布線方案,該圖取自MAX2826 IEEE 802.11a/g收發器的評估板。圖中建立了一個主Vcc節點,從該點引出不同分支的電源線,為RF IC的電源引腳供電。每個電源引腳使用獨立的引線在引腳之間提供了空間上的隔離,有利於減小它們之間的耦合。另外,每條引線還具有一定的寄生電感,這恰好是我們所希望的,它有助於濾除電源線上的高頻雜訊。

圖1:星型拓撲的Vcc布線。

使用星型拓撲Vcc引線時,還有必要採取適當的電源去耦,而去耦電容存在一定的寄生電感。事實上,電容等效為一個串聯的RLC電路,電容在低頻段起主導作用,但在自激振蕩頻率(SRF):

之後,電容的阻抗將呈現出電感性。由此可見,電容器只是在頻率接近或低於其SRF時才具有去耦作用,在這些頻點電容表現為低阻。圖2給出了不同容值下的典型S11參數,從這些曲線可以清楚地看到SRF,還可以看出電容越大,在較低頻率處所提供的去耦性能越好(所呈現的阻抗越低)。

圖2:不同頻率下的電容阻抗變化。

在Vcc星型拓撲的主節點處最好放置一個大容量的電容器,如2.2μF。該電容具有較低的SRF,對於消除低頻雜訊、建立穩定的直流電壓很有效。IC的每個電源引腳需要一個低容量的電容器(如10nF),用來濾除可能耦合到電源線上的高頻雜訊。對於那些為雜訊敏感電路供電的電源引腳,可能需要外接兩個旁路電容。例如:用一個10pF電容與一個10nF電容並聯提供旁路,可以提供更寬頻率範圍的去耦,盡量消除雜訊對電源電壓的影響。每個電源引腳都需要認真檢驗,以確定需要多大的去耦電容以及實際電路在哪些頻點容易受到雜訊的干擾。

良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。儘管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無雜訊”的電源是優化系統性能的基本要素。

接地和過孔設計

地層的布局和引線同樣是WLAN電路板設計的關鍵,它們會直接影響到電路板的寄生參數,存在降低系統性能的隱患。RF電路設計中沒有唯一的接地方案,設計中可以通過幾個途徑達到滿意的性能指標。可以將地平面或引線分為模擬信號地和數字信號地,還可以隔離大電流或功耗較大的電路。根據以往WLAN評估板的設計經驗,在四層板中使用單獨的接地層可以獲得較好的結果。憑藉這些經驗性的方法,用地層將RF部分與其它電路隔離開,可以避免信號間的交叉干擾。如上所述,電路板的第二層通常作為地平面,第一層用於放置元件和RF引線。

接地層確定后,將所有的信號地以最短的路徑連接到地層非常關鍵,通常用過孔將頂層的地線連接到地層,需要注意的是,過孔呈現為感性。圖3所示為過孔精確的電氣特性模型,其中Lvia為過孔電感,Cvia為過孔PCB焊盤的寄生電容。如果採用這裡所討論的地線布局技術,可以忽略寄生電容。一個1.6mm深、孔徑為0.2mm的過孔具有大約0.75nH的電感,在2.5GHz/5.0GHz WLAN波段的等效電抗大約為12Ω/24Ω。因此,一個接地過孔並不能夠為RF信號提供真正的接地,對於高品質的電路板設計,應該在RF電路部分提供儘可能多的接地過孔,特別是對於通用的IC封裝中的裸露接地焊盤。不良的接地還會在接收前端或功率放大器部分產生有害的輻射,降低增益和雜訊係數指標。還需注意的是,接地焊盤的不良焊接會引發同樣的問題。除此之外,功率放大器的功耗也需要多個連接地層的過孔。

圖3:過孔的電特性模型。

濾除其它級電路的雜訊、抑制本地產生的雜訊,從而消除級與級之間通過電源線的交叉干擾,這是Vcc去耦帶來的好處。如果去耦電容使用了同一接地過孔,由於過孔與地之間的電感效應,這些連接點的過孔將會承載來自兩個電源的全部RF干擾,不僅喪失了去耦電容的功能,而且還為系統中的級間雜訊耦合提供了另外一條通路。

在本文的後面部分將會看到,PLL的實現在系統設計中總是面臨巨大挑戰,要想獲得滿意的雜散特性必須有良好的地線布局。目前,IC設計中將所有的PLL和VCO都集成到了晶元內部,大多數PLL都利用數字電流電荷泵輸出通過一個環路濾波器控制VCO。通常,需要用二階或三階的RC環路濾波器濾除電荷泵的數字脈衝電流,得到模擬控制電壓。靠近電荷泵輸出的兩個電容必須直接與電荷泵電路的地連接。這樣,可以隔離地迴路的脈衝電流通路,盡量減小LO中相應的雜散頻率。第三個電容(對於三階濾波器)應該直接與VCO的地層連接,以避免控制電壓隨數字電流浮動。如果違背這些原則,將會導致相當大的雜散成分。

圖4所示為PCB布線的一個範例,在接地焊盤上有許多接地過孔,允許每個Vcc去耦電容有其獨立的接地過孔。方框內的電路是PLL環路濾波器,第一個電容直接與GND_CP相連,第二個電容(與一個R串聯)旋轉180度,返回到相同的GND_CP,第三個電容則與GND_VCO相連。這種接地方案可以獲得較高的系統性能。

圖4. 以MAX2827參考設計板為例的PLL濾波器元件布局。

通過適當的電源和接地抑制PLL雜散信號

滿足802.11a/b/g系統發送頻譜模板的要求是設計過程中的一個難點,必須對線性指標和功耗進行平衡,並留出一定裕量,確保在維持足夠的發射功率的前提下符合IEEE和FCC規範。IEEE 802.11g系統在天線端所要求的典型輸出功率為+15dBm,頻率偏差20MHz時為-28dBr。頻帶內相鄰通道的功率抑制比(ACPR)是器件線性特性的函數,這在一定前提下、對於特定的應用是正確的。在發送通道優化ACPR特性的大量工作是靠憑藉經驗對Tx IC和PA的偏置進行調節,並對PA的輸入級、輸出級和中間級的匹配網路進行調諧實現的。

然而,並非所有引發ACPR的問題都歸咎於器件的線性特性,一個很好的例證是:在經過一系列的調節、對功率放大器和PA驅動器(對ACPR起主要作用的兩個因素)進行優化后,WLAN發送器的鄰道特性還是無法達到預期的指標。這時,需要注意來自發送器鎖相環中本振(LO)的雜散信號同樣會使ACPR性能變差。LO的雜散信號會與被調製的基帶信號混頻,混頻后的成分將沿著預期的信號通道進行放大。這一混頻效應只有在PLL雜散成分高於一定門限時才會產生問題,低於一定門限時,ACPR將主要受PA非線性的制約。當Tx輸出功率和頻譜模板特性是“線性受限”時,我們需要對線性指標和輸出功率進行平衡;如果LO雜散特性成為制約ACPR性能的主要因素時,我們所面臨的將是“雜散受限”,需要在指定的POUT下將PA偏置在更高的工作點,減弱它對ACPR的影響,這將消耗更大的電流,限制設計的靈活性。

上述討論提出了另外一個問題,即如何有效地將PLL雜散成分限制在一定的範圍內,使其不對發射頻譜產生影響。一旦發現了雜散成分,首先想到的方案就是將PLL環路濾波器的帶寬變窄,以便衰減雜散信號的幅度。這種方法在極少數的情況下是有效的,但它存在一些潛在問題。

圖5給出了一種假設的情況,假設設計中採用了一個具有20MHz相對頻率的N分頻合成器,如果環路濾波器是二階的,截止頻率為200kHz,滾降速率通常為40dB/decade,在20MHz頻點可以獲得80dB的衰減。如果參考雜散成分為-40dBc(假設可以導致有害的調製分量的電平),產生雜散的機制可能超出環路濾波器的作用範圍(如果它是在濾波器之前產生的,其幅度可能非常大)。壓縮環路濾波器的帶寬將不會改善雜散特性,反而提高了PLL鎖相時間,對系統產生明顯的負面影響。

圖5:採用環路濾波器的效果。

經驗證明,抑制PLL雜散最有效的途徑應該是合理的接地、電源布局和去耦技術,本文討論的布線原則是減小PLL雜散分量的良好設計開端。考慮到電荷泵中存在較大的電流變化,採用星型拓撲非常必要。如果沒有足夠的隔離,電流脈衝產生的雜訊會耦合到VCO的電源,對VCO頻率進行調製,通常稱為“VCO牽引”。通過電源線間的物理間隔和每個Vcc引腳的去耦電容、合理放置接地過孔、引入一個串聯的鐵氧體元件(作為最後一個手段)等措施可以提高隔離度。上述措施並不需要全部用在每個設計中,適當採用每種方式都會有效降低雜散幅度。

圖6提供了一個由於不合理的VCO電源去耦方案所產生的結果,電源紋波表明正是電荷泵的開關效應導致電源線上的強幹擾。值得慶幸的是,這種強幹擾可以通過增加旁路電容得到有效抑制。另外,如果電源布線不合理,例如VCO的電源引線恰好位於電荷泵電源的下面,可以在VCO電源上觀察到同樣的雜訊,所產生的雜散信號足以影響到ACPR特性,即使加強去耦,測試結果也不會得到改善。這種情況下,需要考察一下PCB布線,重新布置VCO的電源引線,將有效改善雜散特性,達到規範所要求的指標。

圖6:不合理的VCC_VCO去耦測試結果。

[admin via 研發互助社區 ] 從WiFi收發器的PCB布局看射頻電路電源和接地的設計方法已經有5340次圍觀

http://cocdig.com/docs/show-post-44261.html