1. 引言

隨著電路規模越來越大,片上系統(SoC)已經成為IC設計的發展趨勢,相應地也有了更加靈活的片上可編程系統(SOPC)。Nios II CPU是一個基於流水線設計的通用RISC微處理器,擁有五級流水線和指令與數據內存分開的哈佛結構,具有可配置功能。用戶可以根據需求在SOPC Builder中增減IP核,從而實現資源優化。為了構建一個更簡潔高效的片上系統,用戶可以自行開發IP組件,作為用戶自定義邏輯添加到AVALON匯流排[1]。AVALON匯流排是一種結構相對簡單的匯流排,用於連接Nios II和其他外設。它規定了主從部件間的埠連接關係,以及部件間通信的時序關係。

AVALON匯流排擁有多種傳輸模式,以適應不同外設要求。基本傳輸模式是在主從外設之間進行單位元組,半字或字的傳輸。AVALON匯流排還支持一些高級傳輸模式,例如支持流操作,支持延時操作,支持多個主設備同時訪問。

2.用戶自定義邏輯模塊設計流程

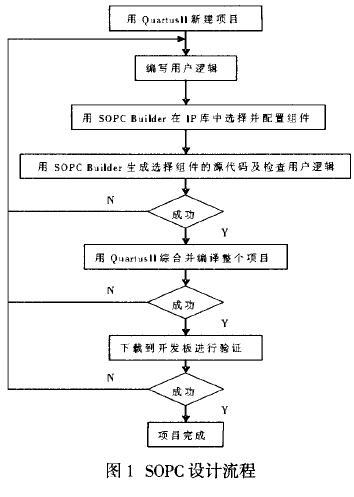

通常來說,EDA廠商及第三方提供的IP核都是通用的,但進行SOPC設計時,用戶可能有特殊需求,這時必須使用用戶自定義邏輯來實現所要的功能。SOPC Builder集成在Altera公司的EDA工具Quartus II中。用戶可以通過SOPC Builder提供的圖形用戶界面從Altera公司提供的IP庫中選取一些組件,如Nios II,DMA,SRAM,FLASH等等,根據實際需要設置這些IP的配置參數。用戶還可以自己編寫HDL代碼模塊作為用戶自定義邏輯方便地添加到SOPC Builder中,設計流程如圖1所示。

3.USB介面模塊的添加

這裡以常用的USB控制晶元SL811HS為例詳細介紹如何在Nios II中添加用戶自定義模塊。圖2是系統結構圖。

3.1 USB控制晶元介紹

SL811HS 是Cypress 公司的嵌入式USB host/slave 介面晶元,支持USB1.1 的全速和低速設備。提供USB 主機的硬體介面及匯流排管理機制,片內集成SIE、USB 收發器和根HUB,能夠完成嵌入式USB 主機所需的功能。

SL811HS的地址和數據均通過ad[7..0]分時傳輸,通過a0(數據/地址選擇線)電平的高低加以區分,當a0置為低電平時,ad[7..0]上傳輸的是SL811片內寄存器/緩衝區的地址;反之高電平則為數據。nwr、nrd、ncs、nrst分別為寫控制線、讀控制線、片選線和複位線,均是低電平有效,Nios II通過這幾根控制線完成對SL811HS片內緩衝區讀寫、片選和複位等操作。intrq是中斷請求信號線。當SL811HS檢測到外設插入、拔出或者數據發送錯誤、超時、數據溢出等異常情況時,通過將intrq置高電平通知Nios II。

3.2 USB介面模塊設計

AVALON匯流排為用戶提供了非常友好的介面,使得系統搭建時的一些細節問題得到屏蔽,大大減輕了系統搭建的工作量。在SL811HS與AVALON匯流排的介面轉換verilog代碼中,只需建立SL811HS埠與AVALON匯流排埠的映射關係即可。nios_intrq、nios_read_n、nios_write_n、nios_cs_n、nios_reset_n、nios_write_data[7..0]、nios_read_data[7..0]、nios_address分別對應NiosII中的中斷、讀、寫、片選、複位、寫數據、讀數據、地址信號。intrq、nrd、nwr、ncs、nrst、ad[7..0]、a0分別對應SL811HS的中斷、讀、寫、片選、複位、數據/地址線、數據/地址選擇信號。如圖3所示。

圖3 自定義USB介面模塊

在Quartus II中對模塊功能進行模擬,由於SL811HS是數據/地址復用埠, Nios II對其緩衝區寫的時候,先把地址通過nios_write_data[7..0]發送到ad[7..0],然後把數據通過nios_write_data[7..0]發送到ad[7..0]。從SL811HS緩衝區讀數據的時候,先把緩衝區地址通過nios_write_data[7..0]發送到ad[7..0],然後通過ad[7..0]讀數據到nios_read_data[7..0]中。如圖4所示。

圖4 介面轉換模塊模擬波形

3.3添加用戶自定義邏輯

在圖形用戶界面SOPC Builder中,左欄有一項是添加用戶邏輯。選擇后,在Bus Userface Type 選中Avlaon Register Slave,設置為靜態地址對齊方式。加入用戶編寫的源代碼文件,同時指定Verilog代碼中各個信號的類型。nios_clk指定為“clk”類型, nios_read_n等指定為“read_n ”類型,nios_write_data[7..0]指定為“writedata” 類型,nios_address指定為“address ”類型,與SL811HS直接相連信號線的都指定為“export”類型。點擊Instantiation選擇Simulate user logic。再點擊Timing,根據SL811HS的時序要求,Setup設置為2,Wait設置為65,Hold設置為5,Unit設置為ns。點擊Finish Editing之後,回到主界面,在System Generation中選擇SDK和HDL,最後點擊Generate。

當SOPC Builder生成一個Nios II處理器設計時,會完成以下工作:

生成Nios II處理器系統的硬體設計文件*.ptf,可以用這些文件來創建Nios II系統硬體。

3.4 SL811HS讀寫函數的實現

讀寫操作是Nios II與SL811HS最基本的通信方式,Nios II讀SL811HS緩衝區數據的時候,先用IOWR函數把所讀緩衝區的地址發送給SL811HS,然後調用IORD函數,得到的返回值就是緩衝區的數據。Nios II往SL811HS緩衝區寫數據的時候,先發地址,然後調用IOWR函數把數據發送到SL811HS緩衝區的指定地址。在用戶工程中的inc/excalibur.h可以找到USB模塊對應地址,根據這個地址來實現SL811HS寄存器的讀寫操作。Nios II每個寄存器佔32位,而地址按位元組分配,所以每個寄存器使用4個地址,USB模塊對應的地址寄存器地址為0x00900c00,數據寄存器地址為0x00900c04。

#define ADDR_REG 0x00900c00

#define DATA_REG 0x00900c04

sl811_read(u8 reg)

{IOWR(ADDR_REG,0,reg);

return IORD(DATA_REG,0);

}

sl811_write(u8 reg, u8 val)

{IOWR(ADDR_REG,0,reg);

IOWR(DATA_REG,0,val);

}

4.總結

本文作者創新點:用verilog編寫Nios II用戶自定義邏輯模塊,實現AVALON匯流排時序與USB控制器SL811HS的時序轉換。同時給出了該模塊的底層讀寫函數。本模塊已成功在FPGA上實現視頻傳輸功能。

SOPC技術利用庫,可以快速生成嵌入式系統。同時,可以方便地把用戶自定義的邏輯加入到系統中,體現了用設計嵌入式系統的靈活性。此外,還可以通過SOPC Builder向處理器中添加用戶自定義的指令,擴充了Nios II指令集。對於原型機的開發,是一種很好的開發方法,且能夠快速地生成最終產品,有效地縮短了開發周期。

[admin via 研發互助社區 ] Nios II的USB介面模塊設計已經有1967次圍觀

http://cocdig.com/docs/show-post-43127.html