1 引言

在Altera的Nios嵌入式處理器中。用戶可以在Nios指令系統中增加用戶自定製指令來滿足某種特定的應用需求。自定製指令可以訪問存儲器或Nios系統外的邏輯資源。增強系統的實時處理能力,特別適用於DSP、數據包處理及對計算密集型軟體進行優化。

Altera高性能快速傅立葉變換(FFT)處理器IP核FFT V2.2.0為實現高速FFT演算法提供了成功的解決方案,將FFT演算法定製為Nios嵌入式處理器的用戶指令,用已實現的高性能FFT演算法作為Nios嵌入式系統的一個加速模塊,使系統可以完成複雜的數據處理任務。

2 Nios自定製指令的軟硬體介面

使用用戶自定製指令,用戶能夠向Nios的ALU和指令系統增加用戶自定製功能,完整的用戶自定製指令包括用戶自定製邏輯和軟體宏兩部分。

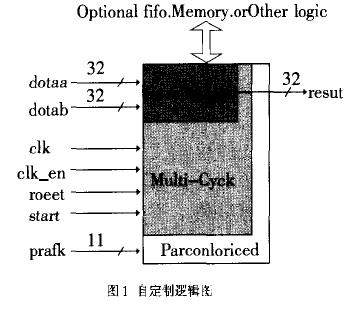

用戶自定製邏輯是完成用戶操作的硬體部分,Nios最多支持5個用戶自定製邏輯作為ALU的一部分。軟體宏提供軟體介面,Nios將創建相應C/C++和彙編的宏代碼,使得用戶能夠訪問用戶自定製邏輯。Nios自定製指令支持多種設計文件,主要有Verilog HDL、VHDL、EDIF netlist file、Quartus II Block Design File等。由於用戶自定製指令邏輯需要直接連到ALU上.所以Nios提供一套預先定義好名稱和功能的介面,如圖1所示。Nios配置嚮導會掃描用戶自定義邏輯,搜索需要的埠。並把這些埠連到ALU上,這就要求用戶自定製邏輯必須指定所需的埠類型,使用預先定義的埠名稱。保證自定製邏輯埠能正確地連到ALU。

當然,Nios也允許用戶自定製指令與Nios系統外部的功能模塊進行信息交流。如果配置嚮導沒能識別用戶邏輯模塊的某個埠。它將該埠引出到系統模塊的頂層.使得外部邏輯可以訪問這些信號,這些埠用export標記。當用戶自定製邏輯被集成到Nios處理器的ALU后.可以通過軟體訪問用戶自定製邏輯,Nios系統中包括5個用戶操作碼,如表1所示,用戶可以通過用C/C++或彙編寫的宏來調用這些操作碼,通過它們來訪問用戶自定製邏輯。

| 操作碼 | 類型 | 操作 |

| USR0 | RR | Ra<-Ra op Rb |

| USR1 | Rw | Ra<-Ra op %to |

| USR2 | Rw | Ra<-Ra op %to |

| USR3 | Rw | Ra<-Ra op %to |

| USR4 | Rw | Ra<-Ra op %to |

3 FFT演算法實現

FFT演算法由Altera的FFT IP核FFT V2.2.0實現,FFT V2.2.0是一個高性能、參數化快速傅立葉變換(FFT)處理器IP核,對Altera StratixII、Stratix GX、Stratix以及Cyclone系列器件進行了設計優化.可以完成變換長度為2m(6≤m≤14)的基-2/4按頻率抽取(DIF)的複數FFT演算法,IP核使用模塊浮點結構可在

數據處理過程中保持最大數據動態範圍,以獲得最大信噪比SNR與最少邏輯需求之間的平衡。

此處FFT V2.2.0相關參數設置為:變換長度(Transform Length)選擇1024點,數據精度選擇16位,旋轉因子精度選擇16位,I/O數據流選擇Streaming形式,複數乘法器結構(Structure)由3個乘法器、5個加法器完成。

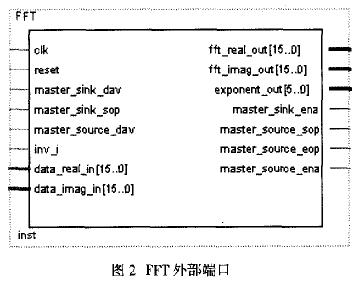

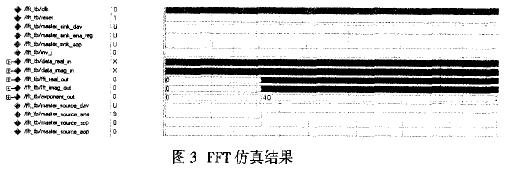

圖2給出了FFT演算法模塊的外部埠,I/O介面協議採用Atlantic介面,輸入介面為主設備匯端(Master Sink),輸出介面為主設備源端(Master Source),Atlantic介面相關內容可查閱文獻3,圖3為FFT在Modelsim環境下的模擬結果。

4 定製Nios核的FFT指令

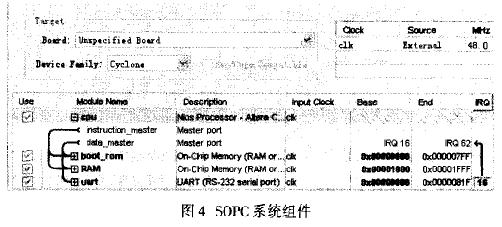

應用SOPC Builder系統開發工具建立一個嵌入Nios軟核的基本SOPC系統,系統組件如圖4所示。顯然,用戶可以根據實際應用的需要增加其它SOPC系統組件,這裡僅分析定製FFT演算法指令相關內容。

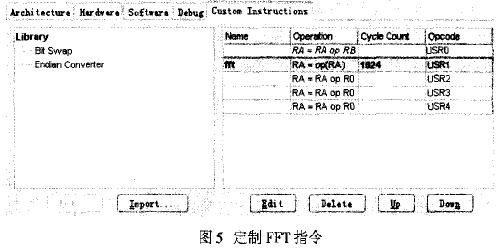

通過自定製指令“Custom Instruction”界面中Import按鈕導入設計好的FFT.vhd文件,定製用戶指令FFT,這裡使用USR1操作碼,如圖5所示。

在Nios系統中用戶自定製邏輯必須與指定的埠類型匹配,對於FFT來說,其輸入和輸出都是實部和虛部為16位的複數,正好可以用一個32位的值來表示 這樣FFT.vhd程序的埠(port)可以按如下方法設置:

PORT(

clk:IN STD_ LOGIC;

reset:IN STD_LOGIC;

dataa:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

result:OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

start:IN OUT STD_LOGIC:='0';

clk_en:IN STD LOGIC:='0'

……

);

即將程序中原有16位長的data_real_in,data_imag_in,fft_real_out,fft_imag_out埠換成兩個32的輸入輸出埠dataa和result,另外,還必須加上start和clk_en兩個輸入埠,雖然這兩個埠信號在程序中沒有作用。埠例化時再與原有埠對應,如下所示:

data_real_in => dataa(31 downto 16),

data_imag_in => dataa(15 downto 0),

fft_real_out => result(31 downto 16),

fit_imag_out => result(15 downto 0),

FFT其餘Atlantic介面信號用export標記,這些埠引出到系統模塊的頂層,外部邏輯可以訪問這些信號。

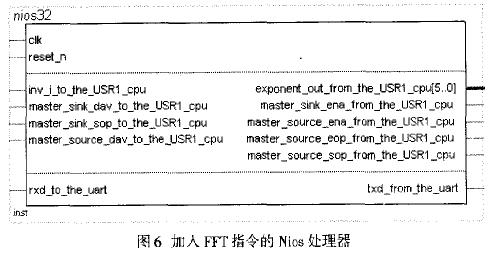

重新生成SOPC系統並更新后得到如圖6所示的加入自定製FFT演算法指令的Nios處理器,將其全程編譯並下載到相應FPGA后,結合Atlantic介面邏輯、FIFO存儲器電路,用戶即可在C或C++中調用nm_fft指令來完成1024點的高速FFT演算法。

5 結論

自定製Nios處理器的用戶指令方法,使設計者可以為某種特定的應用定製自己的指令,定製指令的方法在降低軟體複雜性的同時,明顯地提高了Nios處理器的性能.幫助系統完成複雜的數據處理。

本文作者創新點:基於IP核FFT V2.2.0實現了變換長度為1024點的高速複數FFT演算法,提出了一種新穎的在Nios嵌入式系統中定製用戶FFT演算法指令的方法,使系統可以完成複雜的數據處理任務,增強了系統的實時處理能力。

參考文獻:

[1]梁曦捷,肖璋.一種基於FPGA的順序迭代FFT設計 微計算機信息,2005,1-2

[2]Altera DataSheet FFT Compiler Megacore Function User Guide 2.2.0 rev1 2005.10

[3]Altera DataSheet Custom instructions for the Nios embedded Processor User Guide ve1.1.2 2002.9

[4]Altera DataSheet Altera Interface Functional Specificmion Ver.3.0 2002.6

[5]潘松 黃繼業 曾毓 SOPC技術實用教程[M]北京清華大學出版社2005年3月131-139

[admin via 研發互助社區 ] 自定製Nios處理器的FFT演算法指令已經有6945次圍觀

http://cocdig.com/docs/show-post-43093.html