用VHDL語言設計延時電路時一般用計數器或計數器的級聯來實現。

下面以一個實例來說明如何實現任意時間量的延時。

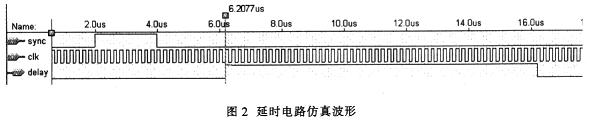

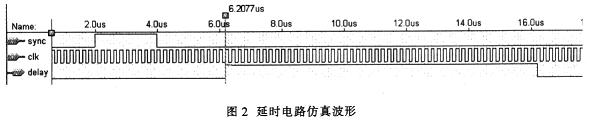

在5 MHz時鐘CLK控制下對同步信號SYNC進行N延時(SYNC脈衝寬度為2 μs,脈衝重複頻率為1 kHz;0μs≤N≤998 μs)。要求每次在同步脈衝上升沿到來時開始延時,並在延時結束后產生寬度為10 μs的選通信號。

需要產生的延時時序如圖2所示(延時量N=4.2μs)。

這裡採用3個計數器和1個或門產生上述延時信號,如圖3所示,模N計數器計延時量;模50計數器計選通信號的寬度;模N+50計數器用於產生使能信號。用VHDL硬體描述語言進行硬體電路設計時,同一個進程中不能用2個時鐘來觸發,而時序圖中又要求在同步脈衝SYNC的上升沿開始延時,為了解決這一問題,採用了模N+50計數器和1個或門。

當同步脈衝為高電平時,模N計數器和模N+50計數器開始計數,並置dly_en為高電平。模N計數器滿,置dly_enl為高電平同時產生選通信號。當模N+50計數器計滿即選通信號產生完之後置dly_en為低電平。當下一個同步脈衝到來時重複以上過程。這種設計電路的好處是當同步脈衝的寬度改變時對時序控制並無影響,因為在計數過程中只用了SYNC的上升沿,從延時開始到選通信號結束,在或門的作用下SYNC對計數器不起控制作用。

上述電路的VHDL程序如下:

該程序選擇N=20,即延時量是4.2 μs,由於要使用時鐘來判斷SYNC的上升沿情況,因此,如果令N=0,產生的delay信號仍然會有1個時鐘的固有延時,在計算延時量時應充分考慮到這一點,延時量=(N+1)×時鐘周期。