所有邏輯器件的廠商生產的器件都支持JTAG 載入電路, 它是一種通用的載入電路. 幾乎所有的邏輯工程師或硬體開發工程師都曾被這種簡單的JTAG 控制電路困惑過. 本人通過多次的現場應用,把JTAG電路的應用技巧總結如下.(以ALTERA,並且FPGA支持CPU+JTAG編程模式為例).

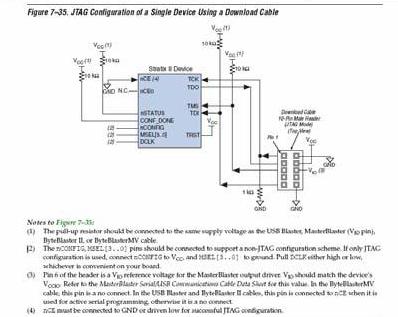

典型的JTAG 控制電路

很多設計者在應用此電路的時候,往往達不到理想的效果.該電路使用方法不正確,可能導致如下結果:

問題一: 電路無法正常載入.

問題二: 電路可以正常載入,編程軟體顯示載入過程正常,但載入后內部邏輯被複位.(多出現在CPLD+FLASH 方式和CPU+FLASH 方式)

問題三: CONF_DONE 信號不能夠正常變高.

工程師在使用此電路的時候,不要忽略nCONFIG, MSEL[3..0]和DCLK 等特殊管腳的作用, 更不要忽略上拉和下拉電路的作用.

nCONFIG, MSEL[3..0],DCLK 等特殊管腳的作用.

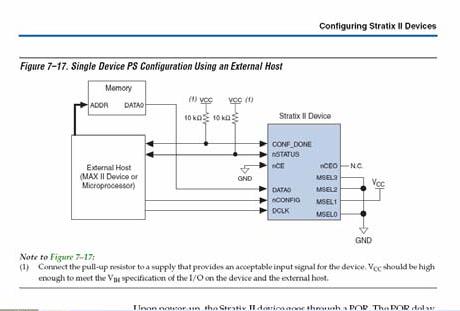

1. nCONFIG信號是FPGA的另一種載入模式PS(Passive Serial)的握手信號,該信號低電平有效.因為PS模式的時鐘可以由設計者靈活控制,並且時序簡單.PS模式常用於CPU載入或CPLD+FLASH等方式的載入,以方便CPU或CPLD模擬PS的時序.其典型電路為:

CPU載入或CPLD+FLASH 載入方式

PS模式時序圖

FPGA 既採用CPU 載入又採用JTAG 的載入模式.這是一種典型的應用,CPU 載入可以避免使用昂貴的配置晶元,在產品量產時使用. JTAG 載入模式一般用於量產之前的調試.在調試的過程中,如果不對nCONFIG信號進行正確的處理,可能導致”問題二”.從PS 模式的時序圖上可以清楚的看到,nCONFIG 信號是低電平有效,PS 的控制電路檢測該信號的下降沿.如果採用CPU+JTAG模式編程FPGA,因在調試時只會用到JTAG模式,那麼此時的nCONFIG必須保證為高電平.也就是PS 模式無效.

2. MSEL[3..0]是Mode Select 管腳.因為FPGA支持不同的載入模式.在用到特殊模式編程FPGA 時,必須把MSEL[3..0]設置為對應的狀態.

從下面的註釋可以看到,JTAG模式對MSEL[3..0]無任何要求,可以接’1’,’0’,NC 等.由於電路支持CPU 載入模式.MSEL[3..0]以PS 模式的要求為準.

3. DCLK 屬於AS(Active Serial)模式的時鐘管腳.AS 模式是專用配置晶元和FPGA 的連接電路.如果電路只支持CPU+JTAG方式,那麼DCLK 應為一個確定的電平,可以為高/低電平,但不能夠接NC.

上拉和下拉電路的作用

Altera 公司不斷優化JTAG 模式中的上拉和下拉電路,這是隨著FPGA 內部的JTAG 控制的發展而發展的.這些電阻有不可低估的作用,不但需要設計者在PCB 上一個不漏,而且需要靈活應用.

上拉/下拉電阻的三大作用:

[admin via 研發互助社區 ] JTAG控制電路的應用與研究已經有5677次圍觀

http://cocdig.com/docs/show-post-43000.html