摘要:介紹用FPGA 實現PCI匯流排的方法.方法根據數字電路設計的自上而下的設計方法,用VHDL 實現,並在Xilinx的SpartenII器件中進行驗證.結果與結論結果表明:用FPGA 實現PCI匯流排是經濟可行的.

PCI的含義為周邊器件互連(Peripheral Component Interconnection).PCI匯流排規範1.0由Int口公司開發,現由一個工業廠商協會管理,稱為PCI SIGN.PCI匯流排有許多其他匯流排(如ISA)所沒有的優點,如高速、熱插拔、自動配置等,在圖像處理、網路、數據採集等領域有廣泛的應用.PCI匯流排的實現一般有3種方法:

本文主要探討用FPGA實現PCI匯流排,並以Xilinx公司的SpartenII器件來實現PCI Slave介面為例進行說明.

1 系統整體框架

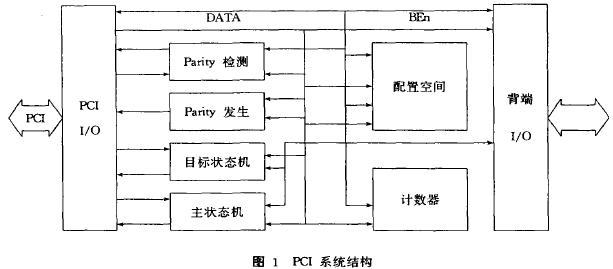

現代數字電路設計一般採用自上而下的方法,即從數字電路的總體要求入手,先將較為複雜的數字系統化為簡單的子系統,再通過邏輯和介面設計用各種功能部件實現要求的數字系統.在設計PCI匯流排時也採用這種方法.根據文獻[1,2],可以將系統劃分為配置空間、PCI協議狀態機、Parity校驗、Parity發生、背端介面等幾部分,如圖1所示.

2 PCI目標狀態機實現和配置寄存器空間

2.1 PCI目標狀態機實現

PCI設備分為主設備和目標設備兩種.主設備是指既能發起交易的設備也能接受交易的設備,而從設備只能被別的設備讀寫.因此實現PCI匯流排時可按需要分為兩種來實現.目標設備的實現要比主設備簡單一些,這裡僅以目標設備的實現來描述PCI協議的實現過程.目標狀態機由4個狀態組成,狀態轉換如圖2所示.

2.2 配置寄存器空間

PCI規範規定,每個PCI功能擁有64個配置雙字的單元.第一個16雙字的格式和用法由PCI規範預定義.具體可以參考PCI規範.實現的框圖如圖3所示.

3 錯誤校驗和處理模塊的設計

PAR 是奇偶校驗I/O 引腳.在數據傳輸期間,它包含數據匯流排AD[31,…,0]和位元組使能線C/BE#[3,…,0]的奇偶校驗位,並且是在一個時鐘后出現.用最簡單的方法產生奇偶校驗位是用有36個輸入的異或門構成. 必須注意,在PCI時鐘為33 MHz時,奇偶校驗位必須在30ns內產生,60ns 內被校驗.Xilinx 的SpartenII每一個CLB有4輸入,因此實現36輸入異或門要4級或5級邏輯才能實現,當時序不能滿足時,可以採用管道線技術實現.例如:奇偶發生邏輯可用圖4所示的管道線邏輯實現.

4 硬體實現

在上述設計的基礎上,就可以開始實現硬體電路.對於複雜數字系統而言,傳統設計方法已不適用,用硬體描述語言成為當代數字系統的主要設計方法.本PCI系統也是採用硬體描述語言(VHDL)並按照FPGA 的設計流程來進行設計的.首先寫出系統的行為級描述,並寫出測試基準(Testbench)進行模擬;模擬成功后,再對系統進行RTL級描述,用綜合工具對其綜合;綜合完成後,再進行綜合后模擬.下一步就是設計實現,放置和路由,時序模擬;最後就可以下載到FPGA 中,對實際電路測試和模擬.

5 結論

通過在Xilinx的SpartenII實現PCI匯流排控制邏輯,可以發現用FPGA 實現是一種經濟和實用的方案.PCI目標控制器消耗大概1萬邏輯門左右,剩下的大部分可用來實現用戶背端邏輯.但是也要注意到的是,實現PCI是一個非常複雜的過程,一般很難在短期內設計成功.要進行產品化設計,可以選擇已經過測試的PCI CORE.本次設計在SpartenII系列的XC2S30進行驗證,達到了預期效果.

[admin via 研發互助社區 ] 基於FPGA 實現PCI匯流排控制器已經有2213次圍觀

http://cocdig.com/docs/show-post-43159.html