隨著多媒體通信技術的發展,人們不再滿足單一文字或聲音的傳遞,從普通電話到視頻電話,從SMS(short messaging service)到EMS(enhanced message service)再到MMS(multimedia messaging service),多媒體技術逐漸進入千家萬戶。因此,研究如何高效地處理多媒體信源,讓其更方便有效地存儲和傳輸是非常必要的。JPEG標準作為圖像壓縮編碼的一項重要技術,不僅適用於靜止圖像的編碼,其分支M-JPEG也適用於低成本場合的運動圖像編碼。現在的圖像顯示卡已發展到高速處理3D圖像的水平,但是,對靜止圖像JPEG壓縮的評測仍是一項基本指標。

目前的嵌入式處理器種類繁多。Altera公司的Nios II處理器是用於可編程邏輯器件的可配置的軟核處理器,與Ahera的低成本的Cyclone FPGA組合,具有很高的性價比。本系統採用Nios II和CycloneEP1C6嵌入式系統開發板,以及VGA顯示器,實現了一個嵌入式JPEG圖像顯示系統。

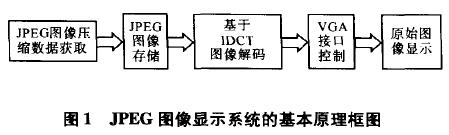

1 總體設計及系統架構

JPEG圖像顯示系統有三大功能:JPEG圖像的存儲、解碼和顯示。基本原理如圖1所示。利用串口通信、USB介面或乙太網數據傳輸獲取JPEG圖像壓縮數據並將數據存入高速存儲器(Flash或SRAM);圖像的解碼主要包括預處理、Huffman解碼、反量化、IDCT變換;圖像顯示是將解碼后的圖像數據轉換為適合VGA工業標準的RGB信號,再利用D/A轉換,最後顯示原始圖像。

該系統在結構上分為3層:系統硬體平台、操作系統和基於IDCT解碼演算法。最底層是系統硬體平台,是系統的物理基礎,提供軟體的運行平台和通信介面。系統的硬體平台在Altera的Nios II Cyclone嵌入式系統開發板上實現,顯示器採用VGA標準的顯示器,可輸出大小為640×480像素、解析度為500 dpi的24位真彩色圖像。第2層是操作系統,採用uCOS II。uCOS II是一個基於搶佔式的實時多任務內核,可固化、

可剪裁、具有高穩定性和可靠性。這一層提供任務調度以及介面驅動,同時,通過硬體中斷來實現系統對外界的通信請求的實時響應,如對乙太網數據流傳輸的控制、對串口通信的控制等。這種方式可以提高系統的運行效率。最上層是JPEG圖像解碼核心演算法的實現。該演算法高效地對壓縮圖像數據進行解碼處理和空間域的轉換。採用C語言在Nios II的集成開發環境(IDE)中實現。

2 系統硬體的設計與實現

2.1 NiosⅡ 嵌入式軟核處理器簡介

Nios II嵌入式處理器是Altera公司於2004年6月推出的第2代用於可編程邏輯器件的可配置的軟核處理器,性能超過200 DMIPS。基於哈佛結構的RISC通用嵌入式處理器軟核,Nios II能與用戶邏輯相結合,編程至Altera的FPGA中。處理器具有32位指令集,32位數據通道和可配置的指令以及數據緩衝。它特別為可編程邏輯進行了優化設計,也為可編程單晶元系統(SoPC)設計了一套綜合解決方案。Nios II處理器系列包括3種內核:一種是高性能的內核(Nios II/f);一種是低成本內核(Nios II/e);一種是性能/成本折中的標準內核(Nios II/s),是前兩種的平衡。本系統採用標準內核。

Nios II處理器支持256個具有固定或可變時鐘周期操作的定製指令;允許Nios II設計人員利用擴展CPU指令集,通過提升那些對時間敏感的應用軟體的運行速度,來提高系統性能。

2.2 硬體平台結構

系統的硬體平台結構如圖2所示。本系統採用USB至UART橋接器CP2102實現與上機位的通信。由Silicon Laboratories推出的CP2102,使RS232升級到USB介面更加簡單,原先採用RS232串口通信方案的設備在軟體上無需作改動即可直接升級到USB。CP2102內建EEPR0M、穩壓器、USB收發器和整合式內部振蕩器。這套組件還包含完整的USB2.0全速(ful1.speed)裝置控制器、橋接控制邏輯以及傳送/接受緩衝器和數據機商議訊號(handshake signa1),這些功能全都整合至5 mm×5 mm的小型封裝內。圖像數據傳輸的流程是:首先初始化串口UART的各個寄存器,主要是接受寄存器(rxdata)、發送寄存器(tx.data)、狀態寄存器(status)、控制寄存器(contro1)、波特率分頻器(divisor)等;然後傳輸等待,圖像數據以1 15 200 bps的速率進人數據寄存器,再通過DMA存入Flash。

本系統硬體平台主要是在Nios II Cyclone嵌入式開發板上實現。系統的主要組件,包括Nios II的標準內核、片內存儲器、UART、DMA控制器、并行I/O介面、Avalon匯流排、定時器等都集成在一塊Ahera的cyclone FPGA晶元上,使用SoPC Builder來配置生成片上系統。

SoPC Builder是功能強大的基於圖形界面的片上系統定義和定製工具。SoPC Builder庫中包括處理器和大量的IP核及外設。根據應用的需要,系統選用Nios II Processor、On Chip Memo~、Flash Memo~(Common Flash Interface)、SDRAM Controller、UART、DMA、Interval timer、Seven Segment PIO、Avalon Tri StateBridge、Ethernet Interface等模塊。對這些模塊配置完成後,使用SoPC Builder進行系統生成。SOPC Builder自動產生每個模塊的HDL文件,同時自動產生一些必要的仲裁邏輯來協調系統中各部件的工作。

2.3 使用Nios II的定製指令提高系統性能

使用Nios II的定製指令,可以將一個複雜的標準指令序列簡化為一個用硬體實現的單一指令,從而簡化系統軟體設計並加快系統運行速度。Nios II的定製指令是與CPU的數據通路中的ALu相連的用戶邏輯塊。其基本操作是,接收從dataa和/或datab埠輸入的數據,經過定製指令邏輯的處理,將結果輸出到result埠。

JPEG圖像解碼的核心演算法是離散餘弦反變換IDCT,二維DCT/IDCT變換需要經過兩次矩陣乘法,8*8的圖像子塊的DCT/IDCT需要進行8 192次乘法和3 584次加法。基於Nios II的JPEG圖像顯示系統採用w Li循環斜卷積演算法,在保證不增加加法器個數的同時,大大減少了乘法器數目,改進了傳統的DCT/IDCT硬體實現方法,採用流水線結構,實行并行優化演算法,提高了IDCT模塊的運算速度,減小了延遲。

定製指令邏輯和Nios II的連接在SoPC Builder中完成。Nios II CPU配置嚮導提供了一個可添加256條定製指令的圖形用戶界面,在該界面中導入設計文件,設置定製指令名,並分配定製指令所需的CPU時鐘周期數目。系統生成時,Nios II IDE為每條用戶指令產生一個在系統頭文件中定義的宏,可以在C或C++應用程序代碼中直接調用這個宏。

3 系統軟體的設計與實現

本系統的JPEG圖像處理和解碼演算法採用c++語言在Nios II IDE中實現 。JPEG圖像解碼演算法的流程如圖3所示。

預處理演算法需要識別不同的標記碼,並提取標記碼中的有用信息。JPEG圖像文件可分為2個部分:壓縮數據和標記碼。壓縮數據是以MCU(最小編碼單元)形式存儲的經過壓縮編碼后的數據。標記碼給出了諸如圖像長度、寬度、量化表、Hufman表等重要信息,而這些信息都包含在不同類型的標記碼中。對一個MCU進行Hufman解碼,需在完成亮度解碼后才能進行色度解碼。解碼后得到6個具有64位元素的一維數組,分別是:4個Y亮度數組、1個cb色度數組、1個cr色度數組(4:1:1模式)。對一個數組來說,Huffman解碼包括直流解碼和交流解碼。對數組第一個元素的解碼稱為直流解碼(簡記為DC解碼),對剩下的63個元素的解碼稱為交流解碼(簡記為AC解碼)。JPEG文件中一般包含4個Hufman表,即亮度DG表、AC表,色度DC表、AC表。一個Huffman碼包括碼頭和碼值2部分,碼頭用來惟一的標識該Hufman碼,並與Hufman表一一對應,碼值是該碼的實際大小。

量化運算需要量化表的配合。從JPEG文件中讀取的量化表一般有2個,分別用2個64位元素的一維數組來存儲,用於對亮度和色度進行反量化。反量化運算就是將上面經Huffman解碼得到的數組中的元素與量化表中對應位置元素相乘。為了進行後面的IDCT,還需要將完成反量化運算的數組進行z字型變換,將一維數組變換成8×8的二維數組。

IDCT變換直接利用自定製指令快速完成8×8的二維數組的離散餘弦反變換。後續處理的任務之一就是完成顏色空間的轉換,即將JPEG圖像數據的Y、cb、cr顏色空間轉換為RGB顏色空間。但是,為了使計算出的R、G、B的值都是正數,需要對Y、cb、cr分別加128進行修正,同時乘法運算出現了浮點數,故需要對浮點數進行定標處理.

4 結束語

本文提出了一種基於Nios II嵌入式處理器軟核的JPEG圖像顯示系統的實現方法。使用Altera的Cyclone FPGA實現,具有開發周期短、成本低等特點;同時,採用Nios II的定製指令來提高系統性能,利用硬體實現演算法速度快的優點,使以Nios II處理器為核心的系統能夠快速地完成大量圖像數據處理。

[admin via 研發互助社區 ] 基於Nios II的JPEG圖像顯示系統研究已經有2237次圍觀

http://cocdig.com/docs/show-post-43134.html