1 引言

PSpice通用電路模擬軟體目前已廣泛地應用於電子線路的設計中,因此在電子技術的教學與實驗中也應充分重視PSpice的學習和運用。對於電路設計,採用模擬的手段,可以大量地減少硬體調試過程中出現的各種問題,易於電路的實現。

2 階梯波發生器的設計

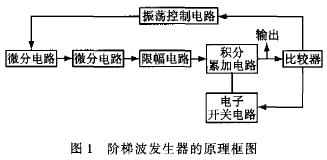

階梯波發生器的應用很廣泛,設計方法也很多,本文採用模擬電路中的基本模塊電路進行階梯波的設計,是為了便於利用PSpice對各功能電路及整個系統進行深入的分析。原理框圖如圖1所示。

階梯波發生器的電路如圖2所示。

2.1 方波發生器

方波發生器由反向輸入的滯回比較器(U1及外圍元件構成)和R4C1構成,其中滯回比較器的閾值電壓

式中Vz為穩壓管的穩壓值。電容器的最高充電電壓和最低放電電壓即是兩個閾值電壓的值。輸出方波周期

通過調節相關參數可改變電路的振蕩頻率。

圖3所示為利用PSpice模擬的電容上電壓的波形以及方波發生器的輸出振蕩波形。

2.2 微分與限幅電路

微分電路採用簡單的電路形式,由C2和D8及與之並聯的負載構成,要求電容充放電的時間常數遠小於輸入方波的周期,使電容C2上電壓近似等於輸入方波的波形。圖4的模擬波形分別為微分電路輸出的波形、電容C2電壓波形及輸入方波的波形。

限幅電路主要由二極體D7構成,將微分電路形成的反向尖脈衝削掉。D8也兼作反向限幅的作用,限幅電路輸出波形如圖5所示。

2.3 積分累加電路

積分累加電路由U2、R5和C3構成,將限幅電路輸出的尖脈衝進行積分累加,從而輸出階梯波,為實現周期性的階梯波,採用電子開關電路對累加器進行控制,當C3上電壓累加到規定值,對其進行放電。輸出階梯波的階梯數可由C3與C2的比值進行控制。

2.4 電子開關電路與比較器

電子開關在這裡由結型場效應管J2N4393擔任,其導通和截止由比較器輸出電壓控制。J2N4393的PSpice模型參數如下:

.model J2N4393 NJF(Beta=9.109m Betatce=-.5 Rd= 1 Rs= 1 Lambda=6m Vto=-1.422

+ Vtotc=-2.5m Is=205.2f Isr= 1.988p N = 1 Nr= 2 Xti=3 Alpha=20.98u

+ Vk=123.7 Cgd=4.57p M=.4069 Pb=1 Fe=.5 Cgs=4.06p Kf=123E-18

+ Af=1)

其中夾斷電壓Vto的值主要決定了飽和漏極電流,間接地影響了積分器中C3的放電是否徹底,因此本文採用Vto作為參數,對J2N4393的轉移特性進行了參數掃描模擬,如圖6所示。

Vto分別取值為-2、-1.5、-1、-0.5、0V下的轉移特性曲線模擬如圖7所示。

比較器電路主要由U3及其外圍元件構成,也構 成了滯回比較器,閾值電壓分別約為0v和-10V。其輸出控制電子開關的導通與截止,同時通過D4也控制了方波發生器,使得電子開關導通的同時開始一個新的階梯波周期。比較器輸出波形如圖9所示。

輸出階梯波的波形如圖10所示。

3 結語

在利用PSpice對階梯波發生器進行模擬分析的基礎上,進行了硬體的安裝和調試,誤差範圍內輸出波形與模擬結果相同。PSpice在這裡作為一個軟體的實驗平台,對硬體電路的調試具有很強的指導作用,可使調試少走很多彎路,並有助於學生對電路的深入理解。

[admin via 研發互助社區 ] 基於PSpice的階梯波發生器分析與設計已經有6055次圍觀

http://cocdig.com/docs/show-post-43113.html