1 引言

基於FPGA的數字系統設計中大都推薦採用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍晶元的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘域帶來的亞穩態、採樣丟失、潛在邏輯錯誤等等一系列問題處理不當,將導致系統無法運行。本文總結出了幾種同步策略來解決跨時鐘域問題。

2 非同步設計中的亞穩態

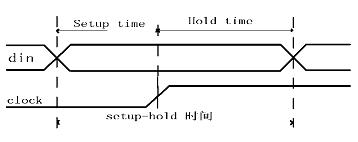

觸發器是FPGA設計中最常用的基本器件。觸發器工作過程中存在數據的建立(setup)和保持(hold)時間。對於使用上升沿觸發的觸發器來說,建立時間就是在時鐘上升沿到來之前,觸發器數據端數據保持穩定的最小時間。而保持時間是時鐘上升沿到來之後,觸發器數據端數據還應該繼續保持穩定的最小時間。我們把這段時間成為setup-hold時間(如圖1所示)。在這個時間參數內,輸入信號在時鐘的上升沿是不允許發生變化的。如果輸入信號在這段時間內發生了變化,輸出結果將是不可知的,即亞穩態 (Metastability)。

一個信號在過渡到另一個時鐘域時,如果僅僅用一個觸發器將其鎖存,那麼採樣的結果將可能是亞穩態。這也就是信號在跨時鐘域時應該注意的問題。如圖2所示。

信號dat經過一個鎖存器的輸出數據為a_dat。用時鐘b_clk進行採樣的時候,如果a_dat正好在b_clk的setup-hold時間內發生變化,此時b_ dat就既不是邏輯"1",也不是邏輯"0",而是處於中間狀態。經過一段時間之後,有可能回升到高電平,也有可能降低到低電平。輸出信號處於中間狀態到恢復為邏輯"1"或邏輯"0"的這段時間,我們稱之為亞穩態時間。

觸發器進入亞穩態的時間可以用參數MTBF(Mean Time Between Failures)來描述,MTBF即觸發器採樣失敗的時間間隔,表示為:

其中fclock表示系統時鐘頻率,fdata代表非同步輸入信號的頻率,tmet代表不會引起故障的最長亞穩態時間,C1和C2分別為與器件特性相關的常數。如果MTBF很大,就認為這個設計在實際工作中是能夠正常運行的,不會因為亞穩態導致整個系統的失效。當觸發器處於亞穩態,且處於亞穩態的時間超過了一個時鐘周期,這種不確定的狀態還會影響到下一級的觸發器,最終導致連鎖反應,從而使整個系統功能失常。

3 同步策略

在非同步設計中,完全避免亞穩態是不可能的。因此,設計的基本思路應該是:首先儘可能減少出現亞穩態的可能性,其次是儘可能減少出現亞穩態並給系統帶來危害的可能性。以下是根據實際工作總結出來的幾種同步策略。

3.1 雙鎖存器法

為了避免進入亞穩態,應當使參數MTBF儘可能大。通常採用的方法是雙鎖存器法,即在一個信號進入另一個時鐘域之前,將該信號用兩個鎖存器連續鎖存兩次(如圖3所示)。理論研究表明這種設計可以將出現亞穩態的幾率降低到一個很小的程度,但這種方法同時帶來了對輸入信號的一級延時,需要在設計時鐘的時候加以注意。

對於上面的雙鎖存器法,如果a_clk的頻率比b_clk的頻率高,將可能出現因為dat變化太快,而使b_clk無法採樣的問題。即在信號從快時鐘域向慢時鐘域過渡的時候,如果信號變化太快,慢時鐘將可能無法對該信號進行正確的採樣,所以在使用雙鎖存器法的時候,應該使原始信號保持足夠長的時間,以便另一個時鐘域的鎖存器可以正確地對其進行採樣。

3.2 結繩法

由於雙鎖存器法在快時鐘域向慢時鐘域過渡中可能存在採樣失效的問題,我們引入了一種安全的跨時鐘域的方法:結繩法。結繩法適合任何時鐘域的過渡(clk1,clk2的頻率和相位關係可以任意選定),如圖4所示。

圖4中的_clk1表示該信號屬於clk1時鐘域,_clk2的信號表示該信號屬於clk2時鐘域。在兩次src_req_clk1之間被src_vld_clk1結繩(Pluse2Toggle)。將src_vld—clk1用雙鎖存器同步以後,該信號轉換為dst_req_clk2(Toggle2Pluse)。同理,用dst_vld_clk2將dat_req_clk2結繩,dst_vld_clk2表明在clk2時鐘域中,src_dat_clk1已經可以進行正確的採樣了。最後將dst_vld_clk2轉換為dst_ack_clk1(Synchronizer and Toggle2Pluse)。dst_ack_clk表明src_dat_clk1已經被clk2正確採樣了,此後clk1時鐘域就可以安全地傳輸下一個數據了。可以看出,結繩法的關鍵是將信號結繩以後,使其保持足夠長的時間,以便另一個時鐘可以正確採樣。圖5描述了結繩法的具體實現,主要包括3個基本單元:Pluse2Toggle、Synchronizer和Toggle2Pluse。

Pluse2Toggle模塊負責將兩個脈衝信號結繩,即將單脈衝信號延長;Synchronizer模塊用雙鎖存器法將得到的信號過渡到另一個時鐘域;Toggle2Pluse模塊與Pluse2Toggle功能相對,即將延長的脈衝信號還原為單脈衝,這裡用到了異或門。整體的設計思想就是用Pluse2Toggle將信號延長,用Synchronizer過渡,再用Toggle2Pluse還原,以保證另一個時鐘域可以正確採樣,而接收方用相反的流程送迴響應信號。

結繩法可以解決快時鐘域向慢時鐘域過渡的問題,且適用的範圍很廣。但是結繩法實現較複雜,在設計要求較高的場合應該慎用。

4 結束語

本文主要把FPGA非同步時鐘設計中產生的問題,原因以及解決問題所採用的同步策略做了詳細的分析。其中雙鎖存器法比較適用於只有少數信號跨時鐘域;結繩法比較適用快時鐘域向慢時鐘過渡的情況。所以,在實際的應用中,應根據自身設計的特點選擇適當的同步策略。

[admin via 研發互助社區 ] FPGA非同步時鐘設計中的同步策略已經有2836次圍觀

http://cocdig.com/docs/show-post-43107.html