1 概述

在基於FPGA的SOC設計中,常使用串口作為通信介面,但直接用FPGA進行串口通信數據的處理是比較繁雜的,特別是直接使用FPGA進行串口通信的協議的解釋和數據打包等處理,將會消耗大量的FPGA硬體資源。為簡化設計,降低硬體資源開銷,可以在FPGA中利用IP核實現的嵌入式微處理器來對串口數據進行處理。

本文中的設計採用了XILINX的FPGA,可選用的嵌入式微處理器IP核種類繁多,但基於對硬體資源開銷最少的考慮,最終選用了Picoblaze。

嵌入式微處理器PicoBlaze適用於Spartan-II/E、CoolRunner-II和Virtex系列FPGA,運行速度可達到40MIPS以上,提供49個不同的指令,16個寄存器,256個地址埠,1個可屏蔽的中斷。其性能超過了傳統的8bit微處理器。嵌入式微處理器Picoblaze的功能、原理見參考文獻[1]。

Picoblaze使用靈活,但其缺點是可定址的存儲空間非常有限,因此為滿足實際需要本文同時也提出了使用片外SDRAM器件對其存儲能力進行擴展的設計方法。

2 串口收發介面設計

2.1串口收發介面硬體設計

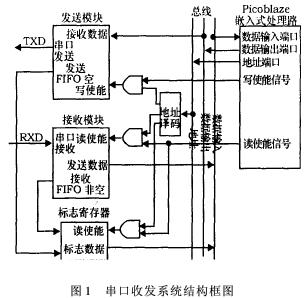

嵌入式微處理器PicoBlaze本身並不具備串列介面,因此必須在FPGA中設計串口接收和發送模塊並通過匯流排結構與Picoblaze連接。

串口接收和發送模塊的設計可採用成熟的IP核。實際設計中採用了XLINX的串口收發IP核,其特點是串口波特率,符號規則都可以靈活地定製,同時具有16位元組的接收FIFO和16位元組的發送FIFO。串口收發IP核的功能、原理見參考文獻[2]。

使用Picoblaze和串口收發IP核構成的串口收發系統結構見圖1。

在設計中,發送模塊、接收模塊和標誌寄存器分別有不同的地址,Picoblaze通過地址埠對串口收發模塊進行訪問。設計中的標誌寄存器,可用於指示發送模塊和接收模塊中FIFO的狀態,Picoblaze通過查詢標誌寄存器來完成對串口數據的收發控制。

2.2串口收發介面軟體設計

·串口發送、接收子程序

Picoblaze通過對標誌寄存器的查詢,根據FIFO的狀態進行操作。串口發送和接收子程序流程見圖2。

Picoblaze的編程,類似於彙編語言。

串口發送子程序代碼如下:

(1)串口接收子程序

receive:

INPUT s0,uartrxflag ;查詢接收FIFO是否非空

AND s0,01

AND s0,s0

JUMP Z,receive ;若FIFO為空時繼續查詢

INPUT rxdata,uartrx ;若FIFO非空時讀取數據

RETURN

(2)串口接收子程序

translate:

INPUT s0,uarttxflag ;查詢發送FIFO是否為空

AND s0,01

AND s0,s0

JUMP NZ,translate ;若發送FIFO非空時繼續查詢

OUTPUTtxdata,uarttx ;若發送FIFO為空時寫入數據

RETURN

·協議處理子程序

本文應用中的串口通信,採用應答機制,數據具有一定的幀結構,Picoblaze需要對命令幀進行拆包處理,並根據幀的內容進行相應的操作,然後發送響應幀。

| 幀頭 | 字長 | 控制字 | 數據 | 校驗 | 幀尾 |

| 8bit | 16bit | 8bit | N bit | 8bit | 8bit |

| 幀頭 | 字長 | 控制字 | 數據 | 校驗 | 幀尾 |

| 8bit | 16bit | 8bit | N bit | 8bit | 8bit |

根據幀格式,Picoblaze對串口數據的處理流程見圖3。

以上的Picoblaze程序流程所處理的數據幀結構是較為簡單的,當需要處理複雜的通信協議時可以考慮採用多個Picoblaze并行處理。

3 存儲器介面設計

Picoblaze的優點是資源佔用少,使用靈活,但可定址的地址空間最多為256位元組,無法滿足對大量通信數據進行存儲的需要。因此本文中採用了SDRAM器件來對Picoblaze的存儲能力進行擴展。

SDRAM器件的管腳分為控制信號、地址和數據三類。通常一個SDRAM中包含幾個BANK,每個BANK的存儲單元是按行和列定址的。SDRAM的具體特性見參考文獻[3]。

SDRAM在使用時需要專用的控制器來產生滿足SDRAM所需的信號。FPGA中SDRAM控制器也有多種IP核可以選用。出於對設計通用性的考慮,本文中採用了一款Altera提供的SDRAM控制器IP核,並增加了必要的設計以滿足與Picoblaze的介面要求。SDRAM控制器IP核的功能、原理見參考文獻[4]。

對Picoblaze與SDRAM控制器的介面設計有以下幾個出發點:

3.1存儲器介面硬體設計

Picoblaze與SDRAM存儲器介面的硬體原理框圖見圖4。

控制狀態機控制的地址計數器為SDRAM控制器提供地址,同時控制狀態機還控制輸入數據緩衝區和輸出數據緩衝區,並且根據Picoblaze的地址埠數據和讀/寫使能信號產生SDRAM控制器的命令字。

(1)SDRAM初始化

每次加電或複位后控制狀態機執行對SDRAM控制器的初始化操作,設置SDRAM的時間參數和刷新周期等。

(2)數據寫入SDRAM

輸出數據緩衝區由16×8bit的FIFO構成,當Picoblaze向輸出數據緩衝區寫入超過8個位元組后,通過“半滿”信號使控制狀態機進入SDRAM的長度為8的突發寫模式,在寫入完成後控制狀態機將地址計數器增加8,以準備好下一次的寫入。

(3)數據讀取

數據讀取時Picoblaze首先向控制狀態機發送讀取請求,控制狀態機進入SDRAM的長度為1的突發讀模式,並將讀取的數據寫入輸入數據緩衝區,此後Picoblaze再由輸入數據緩衝區中讀取數據。在讀取后,地址計數器做相應的增加,以實現先入先出功能。

以上的設計方法適用於需要數據連續寫入后再連續讀取的場合。

控制狀態機狀態圖見圖5。

3.2存儲器介面軟體設計

由於在SDRAM控制器與Picoblaze之間增加了控制狀態機,簡化了Picoblaze的程序設計。

(1)數據寫入

數據寫入時Picoblaze向輸出數據緩衝區直接寫入數據即可。

(2)數據讀取

數據讀取時Picoblaze首先向控制狀態機發出請求,然後等待輸入數據緩衝區的數據準備就續后再讀取。

4 結論

本文在XILINX FPGA中採用嵌入式處理器Picoblaze進行SOC設計,以較少的硬體資源實現了對串口通信數據的處理,同時採用SDRAM器件對Picoblaze的存儲能力進行擴展。所採用的設計已應用於多個產品中。經過了長期的使用和測試證明文中的設計方法穩定、可靠,並且具有資源佔用少,設計靈活的優點。

參考文獻

[1]PicoBlaze 8-BitMicrocontroller forVirtex-E and Spartan-II/IIE Devices,Ken Chapman Xilinx Ltd,XAPP213 (v2.1)February 4, 2003

[2]UART Transmistter and Receiver Macros,Ken Chapman Xilinx Ltd,2002,10

[3]MT48LC2M32B2數據手冊[R].Micron Technology Inc., 2002

[4]SDR SDRAM Controller white pape,Altera Corporation

[admin via 研發互助社區 ] 基於FPGA的SOC系統中的串口設計已經有2396次圍觀

http://cocdig.com/docs/show-post-43102.html