1.引言

由於通信對帶寬的需求迅猛增長,促使一系列基於差分、源同步、CDR(Clock Data Recovery,時鐘數據恢復)等先進技術的互聯方式應運而生。在高速率的介面設計中,由於採用含有源同步的差分串列傳輸方式(如LVDS、LVPECL 等),傳輸過程中時鐘和數據分別發送,各信號瞬時抖動不一致,從而破壞了接收數據與時鐘之間的定時關係。時鐘恢復就是在串列數據輸入中引入數據比特率以產生某一相同的特定時鐘頻率。該時鐘的相位由可在數據模式的中心進行數據採樣的一個鎖相環來確定。通常情況下,數據時鐘的恢複電路是採用PLL(Phase Loop Lock,鎖相環)來實現的,PLL 是相位和頻率跟蹤的最有效的方法之一,可直接應用於大規模系統中。但對突發信號來說,鎖相環不能滿足其快速同步的要求,大的相位變化就能引起失鎖,而且再鎖定需要的時間也較長。也有人採用全定製的過採樣時鐘恢復的方法,但這種基於多相位的數據採樣和數字化后處理的方法需要用高於系統速率幾倍的採樣速率,然後通過相位比較選擇最佳的採樣,從而實現數據恢復。由於需要很高的採樣速率,對於高速率的接收模塊來說,工藝上很難得到實現。FPGA(Field Programmable Gate Array,現場可編程邏輯門陣列)在許多領域均有廣泛的應用,特別是在通信領域,由於具有很好的實時性而使得信號的實時處理成為可能。基於Xilinx 公司Virtex-II系列FPGA,採用相位偏移的方法,等效的實現高於系統時鐘的採樣速率,從而實現對時鐘數據信號的恢復。

2.設計原理

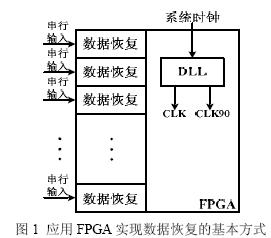

時鐘數據恢復允許接收器將輸入的數據流中的時鐘或數據提取出來。通常,接收器從到來的數據流中提取數據,並將這些數據送到一個單獨的時鐘域中,然後把這些提取的數據送到FIFO 作進一步的處理。有時,接收器的時鐘也用作數據的前向傳輸。數據恢復的速度受到DLL(Delay Locked Loop,延遲鎖定環)所能接受的最大時鐘的限制,典型的數據恢復的表示如圖1 所示。

系統時鐘輸入到一個DLL 單元,如圖1 所示。DLL 的CLK 為同步電路提供時鐘,同時反饋回DLL。DLL 的另一個輸出(即CLK90)延遲四分之一周期后與原時鐘同步。Xilinx公司Virtex 系列FPGA 中提供了多個數字時鐘管理器(DCM),DCM 模塊可提供CLK 及CLK90 輸出,其中CLK90 為CLK 相移90 度后的輸出,兩個輸出是完全同步的,如下圖2所示(DCM 其他埠省略)。

在數據時鐘恢復時,將到來的數據分別輸入到四個觸發器,其中兩個觸發器由CLK 作為計數時鐘(一個用CLK 的上升沿,一個用CLK 的下降沿),另外兩個由CLK90 作為計數時鐘(一個用CLK90 的上升沿,一個用CLK90 的下降沿),如下圖3 所示。這裡特別要注意:保證從輸入引腳到四個觸發器的延遲基本一致。要使延遲保持一致,可對設計的時鐘網路設置MAXSKEW 參數[3]。

對於圖3 數據時鐘恢複電路存在如下的時序關係,如圖4 所示。A、B、C、D 分別表示四個不同的採樣點,輸入數據1、2、3、4 分別表示四種不同的數據到來的情況。

圖3 中的第一列觸發器的觸發分別由時鐘CLK 的上升沿、時鐘CLK90 的上升沿、時鐘CLK 的下降沿及時鐘CLK 的下降沿觸發。按照這樣的方式來觸發就可以得到四個數據採樣點,即圖4 中所示的A、B、C、D 四個點。這樣就將原始時鐘周期分成了四個單獨的90度的區域,在這裡我們定義四個區域為四個不同的時鐘域a、b、c、d。這樣,如果系統時鐘為200MHz,那麼圖3 所示的電路就相當於產生了800MHz 的採樣速率。但是僅僅通過一階的觸發器,輸出的採樣數據存在亞穩態的問題,因此需對採樣點作進一步的處理。這裡可將四個採樣點通過進一步的觸發,除掉亞穩態的問題,從而使採樣點移到下一個相同的時鐘域。通常,亞穩態的去除要經過兩三級的處理,這就使得在有效數據輸出前會有數位無效的數據,但此時DCM 的locked 並未鎖定,因此可由此信號來指示輸出數據的有效性。在數據採樣的第一個階段,電路檢測數據線上數據的傳輸。當檢測到有數據傳輸時,對傳輸數據的有效性進行確認。確認數據有效后,輸出高電平來指示採樣點有數據傳輸。因為有四個輸出,所以需要一個復用器來選擇數據。復用器從選定的時鐘域中選擇數據位,例如檢測電路確定從時鐘域a 中採樣的數據有效,那麼將時鐘域a 中採樣的數據通過輸出端輸出。

3.FPGA 實現及模擬結果

應用DCM 模塊產生用於時鍾數據恢復的CLK 及CLK90。設計的時鐘數據恢複電路的模塊如圖4 所示。其中clk 為輸入時鐘,rst 為複位輸入,datain 為輸入待恢復的串列數據,locked 為DCM 鎖定端,dreco[1:0]為恢復的時鐘數據輸出端,dvalid[1:0]指示輸出恢復的時鐘數據有效。dreco[1:0]分為高位和低位,dvalid[1:0]的高位和低位分別指示dreco[1:0]的高位和低位有效。

對所設計的時鐘數據恢複電路應用ISE 軟體內嵌的XST(Xilinx Synthesis Technology)綜合工具進行綜合,得到的數據及時鐘恢復的模擬波形分別如圖5 和圖6 所示。

圖5 數據恢復的XST 模擬波形

圖6 時鐘恢復的XST 模擬波形

從圖5、圖6 所示的對輸入數據及時鐘信號進行恢復的XST 模擬波形中可以看出,當dvalid[1:0]指示輸出的時鐘數據有效時並不是從指示有效的第一位開始就能正確恢復,而是需要經過一段時間(這段時間主要是由於存在的亞穩態造成的),經過這段時間,到DCM的locked 端輸出高電平時,信號被鎖定,此時輸出的時鐘數據開始正確恢復輸入的時鐘數據信號。

4.結論

從模擬結果來看,由於電路穩定需要一定的建立時間,因此輸出數據流的前幾位是無效的數據位。但當電路穩定下來后,DCM 鎖定信號,此時可以有效地對輸入的時鐘數據進行恢復。同時,由於恢復速度受限於延遲鎖定環(DLL)所能接受的最大時鐘,因此該電路存在最大的可恢複數據的速率,通常情況下Virtex-II-5 器件所能恢復的最大數據傳輸速率為420Mb/s。

[admin via 研發互助社區 ] 基於Virtex-II的時鐘數據恢複電路的設計已經有4554次圍觀

http://cocdig.com/docs/show-post-43092.html