基於NiosII 軟核的SOPC(System On Programmable Chip)是Altera 公司提出的片上可編程系統解決方案,它將CPU、存儲器、I/O介面、DSP 模塊以及鎖相環(PLL)的系統設計所必須的模塊集成到一片FPGA 上,構成一個可編程的片上系統,使所設計的電路在其規模、可靠性、體積、功耗、功能、上市周期、開發成本、產品維護以及硬體升級等多方面實現最優化。

目前在Altera SOPC Builder 下集成了包括UART、SPI、Ethernet、SDRAM、Flash、DMA等控制器的IP 核。此外,用戶也可以根據系統的需要自己設計或者購買第三方廠商的IP 核通過Avalon 匯流排像搭積木一樣方便地將這些IP 捆綁的系統上。但是在顯示介面上,Altera公司只提供了一個16*2 的字元型LCD 控制器的IP 核,只能用來顯示數字和英文字母。如用戶需要圖形顯示(如MP4 和PDA)則需要外接專用控制晶元或自己設計IP 核,使用起來很不方便。因此我們設計一個基於Nios II 系統的可配置LCD 控制器的IP 核,本IP 核可以方便的通過Avalon 掛接到Nios II 的系統上。考慮到目前LCD 顯示屏的實際需要,我們設計的LCD 顯示控制IP 核具有以下主要功能:

1. Avalon 匯流排規範

1.1 匯流排概述

Avalon 匯流排是Altera 公司為SOPC 系統開發的一種專用的內部連線技術,是一種理想的用於系統處理器和外設之間的內聯匯流排。它是構建在Nios II 軟核的基礎上,由Altera 公司提供SOPC Builder 系統設計工具自動生成。

Avalon 匯流排支持多個主外設,任何一個主外設都可以直接進行存儲器訪問(DMA),而無須Nios II 處理器的干預。一般的系統匯流排(如AMBA 匯流排)都是採用主端總裁機制,而Avalon 採用DMA 從端仲裁機制,能夠實現真正意義上的多模塊DMA 并行傳輸,而不相互影響。

Avalon 匯流排允許多個主埠連接到匯流排模塊,實現匯流排的的併發多主埠傳輸的功能,而匯流排模塊不需要額外的特殊信號;當有多個主外設試圖同時訪問同一外設時,由Avalon匯流排模塊內部的從埠仲裁邏輯來處理衝突,對於主埠來說,它並不會感到有另一個主埠也在爭用該外設,而是簡單的發現它的等待請求信號一直有效,直到目標外設從埠準備好來處理自己的請求。因此,多個主外設只要不是同時訪問同一個從外設,即可同時進行匯流排傳輸。仲裁的詳細信息被封裝在匯流排內部,主外設和從外設的介面是一致的,與外設的數量無關。

1.2 Avalon 匯流排流傳輸模式

Avalon 規定了各種傳輸模式,這裡只介紹本IP 核所使用的流傳輸模式。關於其他的匯流排模式讀者可以Avalon 的匯流排規範。

流傳輸模式是在流模式主外設和流模式從外設之間建立一個開放的通道以供連續的數據傳輸。該通道使得只要存在有效數據,數據便能在主從埠對之間流動,主外設不必為了確定從埠是否可用而不斷地訪問從外設的寄存器。流傳輸模式使得主從埠之間的數據吞吐量達到最大,同時避免了從外設數據溢出。流傳輸模式最適合DMA 傳輸。一個只包含簡單的流控制信號和一個計數器的DMA 控制器就可以用來在一個從外設和一個存儲器之間連續地傳輸數據。

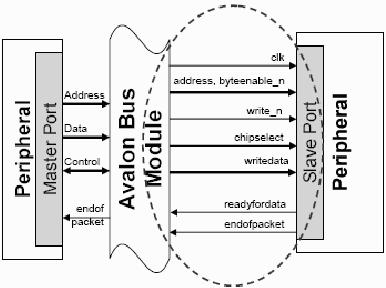

由於數據流是從Avalon 匯流排流向LCD 控制器,所以是流模式的從埠寫傳輸。圖1 顯示了流模式從埠寫傳輸的模型。

圖1 流模式從埠寫傳輸模型

除了基本從埠傳輸中使用的信號外,流模式外設的介面中又引入了readyfordata、dataavailable 和 endofpacket 三個信號。流模式從埠就是指使用了一個或多個上述信號的從埠。readyfordata 有效表示外設準備好接受 Avalon 匯流排模塊的寫傳輸;dataavailable 有效表示能夠為來自 Avalon 匯流排模塊的讀傳輸提供數據。Avalon 匯流排模塊只在 readyfordata或 dataavailable 有效時才會發起傳輸行為。endofpacket 信號的含義取決於用戶設計。

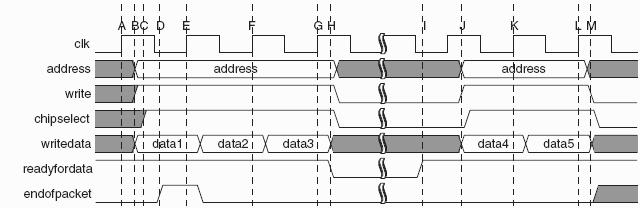

流模式從埠寫傳輸模型的時序如圖2 所示。

圖2 流模式從埠寫傳輸時序

2. Avalone 流模式LCD 控制器IP 核設計

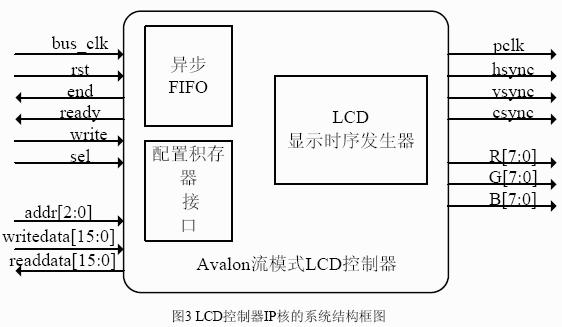

LCD 控制器按功能可劃分為三個模塊:介面模塊,數據處理模塊和時序產生模塊。介面模塊主要用來對系統進行配置,獲取系統狀態信息以及從內存讀出將要顯示的數據信息;數據處理模塊根據系統的配置信息,對讀入控制器的內存數據進行相應的處理,以符合用戶設置的顯示要求;時序產生模塊產生顯示時序信號,使得系統在不同的配置下都能產生與之相應的精確時序,以保證圖象的正確顯示。

在具體實現時,這三個部分又可以劃分為不同的功能模塊來完成系統的總體功能。整個模塊包括配置寄存器介面模塊、DMA 介面模塊組成和非同步FIFO 模塊,時序產生部分由時序產生模塊構成。圖3 為我們所設計的LCD 控制器IP 核的系統結構框圖。

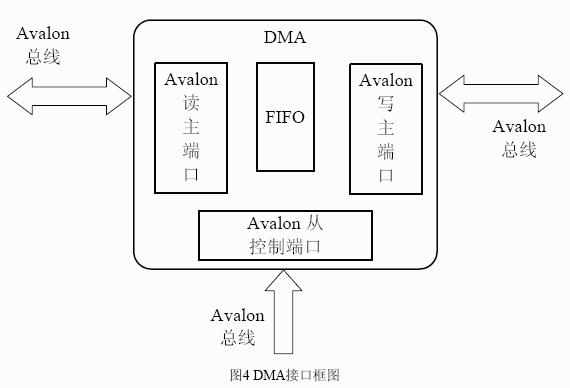

2.1 DMA 介面模塊

一般情況下,LCD 顯示需要進行大批量的數據傳送。在標準 VGA(640×480 60Hz)模式下,每個像素點的掃描周期只有40ns。如此高速的數據傳輸,如果直接通過CPU 來操作,將會消耗大量的CPU 時間。為了提高CPU 的工作效率,我們在Nios II 下利用DMA(Direct Memory Access,直接存儲器訪問)來完成。利用DMA 控制器在LCD 控制器和顯示存儲器SDRAM 之間建立一條專用的DMA 傳輸通道,通過DMA 控制器自動的讀去圖象數據,不需要CPU 干預。NiosII 中DMA 控制器如圖4 所示:

在DMA 傳輸時,首先需要由CPU 對DMA 進行初始化,設置顯示存儲器的基地址和長度以及LCD 控制器輸入寄存器的地址,然後打開DMA 傳輸通道,使DMA 在沒有CPU 干預的情況下直接從顯示存儲器讀取顯示數據傳送到LCD控制的FIFO中。Nios II 可以在DMA暫停傳輸的期間操作SDRAM 中的顯存,完成LCD 顯示圖像的更新。

DMA 介面採用Avalon 主設備埠來實現。

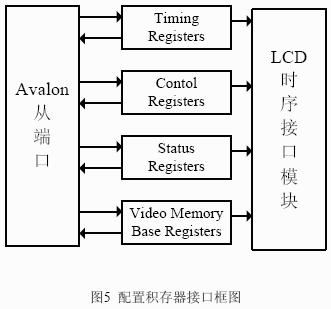

2.2 配置積存器介面模塊

系統可以通過配置寄存器介面模塊對LCD 顯示控制器進行各種功能配置;LCD 控制器也可以通過介面模塊向系統反饋所需的狀態信息,從而實現對系統狀態的檢測和控制。通過針對不同種類的LCD 屏幕和不同的顯示模式提供相應寄存器,可以保證對於各種LCD 顯示屏的兼容。

下圖5 為配置積存器介面模塊與Avalon 匯流排和LCD 時序發生器介面的示意圖

配置寄存器介面所採用的是Avalon 的從設備埠來實現。

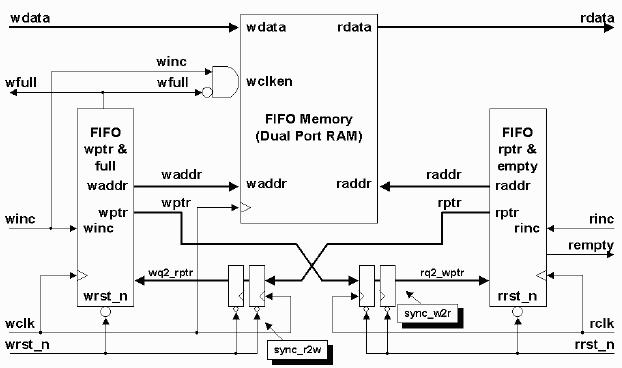

2.3 非同步FIFO 模塊

由於匯流排介面模塊和LCD 控制器工作在不同的時鐘域,如果直接傳送數據將會使電路進入亞穩態,無法正常工作。所以使用非同步FIFO 做為介面在兩個時鐘之間傳遞數據。典型的非同步FIFO 由非同步雙埠RAM 和控制邏輯構成。圖6 為典型非同步FIFO 的系統框圖

圖6 非同步FIFO的系統框圖

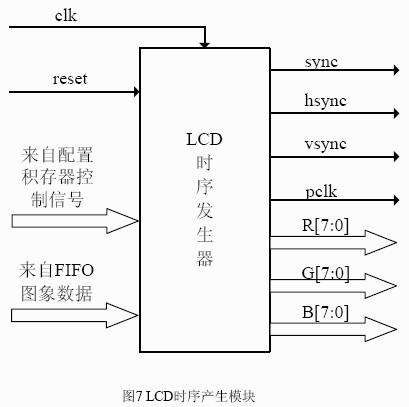

2.4 LCD 時序產生模塊

通過讀取配置寄存器獲得像素時鐘,行周期,幀周期,同步頭寬度以及時鐘分頻係數等信息后,LCD 時序產生模塊產生LCD 顯示需要的行同步信號、幀同步信號以及複合消隱信號。圖7 描述了LCD 介面時序發生模塊的介面信號

3. LCD 控制器IP 核的模擬調試與安裝

3.1 LCD 控制器IP 核的模擬調試

本IP 核使用Verilog HDL 來編寫,首先在Modelsim6.1 下先進行RTL 級的功能模擬,當所有功能都滿足要求時,就可以使用綜合工具綜合后加入延時信息進行進行時序模擬。如果時序模擬也滿足電路的設計要求,就可以當做一個NiosII 系統自定義的組件加到Nios II 系統中去。

3.2 LCD 控制器IP 核的安裝

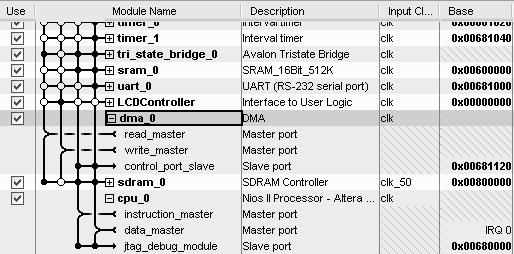

Avalon 流模式的 LCD 控制器需要安裝到 SOPC Builder 中,以便將其加入到NiosII 系統中。

這裡的LCD 控制器是一個典型的流模式自定義外設。啟動DMA 傳輸后,DMA 控制器將批量數據送往LCD 控制器,因此也可將LCD 控制器看成 FIFO 類型的存儲器外設。選擇Avalon Components->Legacy Components->Interface to User Logic,加入LCD 控制器的IP 核。

圖8 DMA、LCD 控制器模塊連接圖

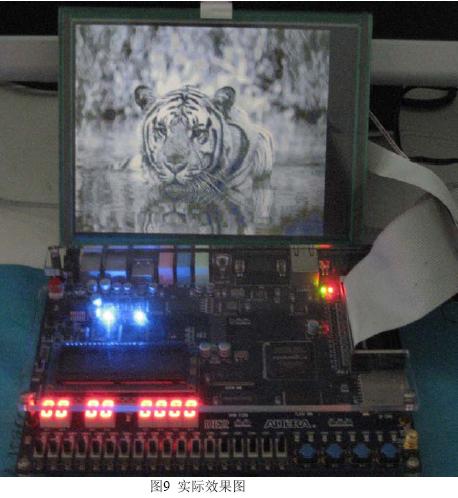

3.3 實際測試效果圖

實際測試是在Altera的DE2開發板上進行的。使用的LCD屏是夏普公司的800*600型號為LQ080V3DG01的TFT LCD屏,實際的顯示效果圖如圖9所示

4. 總結

本文討論了基於Avalon 匯流排流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能劃分設計,並對IP 核的模擬驗證,最後加入到Nios II系統中。該IP 核經測試效果良好。由於本IP 核是可配置的,具有很好的移植性,可以方便的應用以Nios II 為核心的各種需要圖形顯示的嵌入式系統中。

[admin via 研發互助社區 ] 基於Avalon 匯流排的可配置LCD 控制器IP 核的設計已經有4035次圍觀

http://cocdig.com/docs/show-post-43088.html