時鐘是整個電路最重要、最特殊的信號,系統內大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時序邏輯狀態出錯;因而明確FPGA設計中決定系統時鐘的因素,盡量較小時鐘的延時對保證設計的穩定性有非常重要的意義。

1.1 建立時間與保持時間

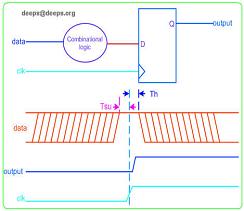

建立時間(Tsu:set up time)是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立的時間不滿足要求那麼數據將不能在這個時鐘上升沿被穩定的打入觸發器;保持時間(Th:hold time)是指數據穩定后保持的時間,如果保持時間不滿足要求那麼數據同樣也不能被穩定的打入觸發器。建立與保持時間的簡單示意圖如下圖1所示。

圖1 保持時間與建立時間的示意圖

在FPGA設計的同一個模塊中常常是包含組合邏輯與時序邏輯,為了保證在這些邏輯的介面處數據能穩定的被處理,那麼對建立時間與保持時間建立清晰的概念非常重要。下面在認識了建立時間與保持時間的概念上思考如下的問題。

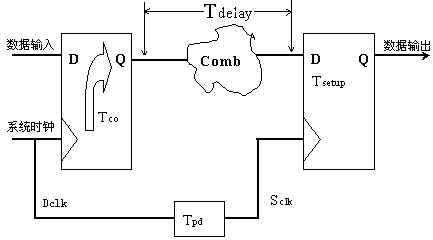

圖2 同步設計中的一個基本模型

圖2為統一採用一個時鐘的同步設計中一個基本的模型。圖中Tco是觸發器的數據輸出的延時;Tdelay是組合邏輯的延時;Tsetup是觸發器的建立時間;Tpd為時鐘的延時。如果第一個觸發器D1建立時間最大為T1max,最小為T1min,組合邏輯的延時最大為T2max,最小為T2min。問第二個觸發器D2立時間T3與保持時間T4應該滿足什麼條件,或者是知道了T3與T4那麼能容許的最大時鐘周期是多少。這個問題是在設計中必須考慮的問題,只有弄清了這個問題才能保證所設計的組合邏輯的延時是否滿足了要求。

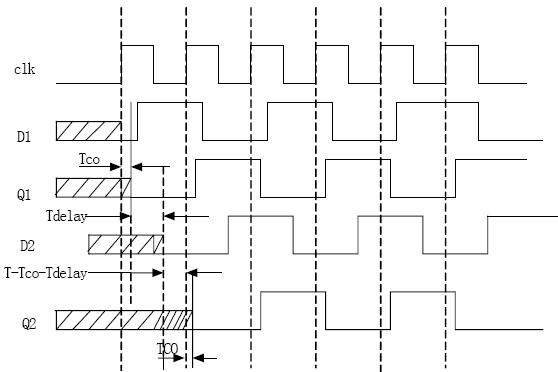

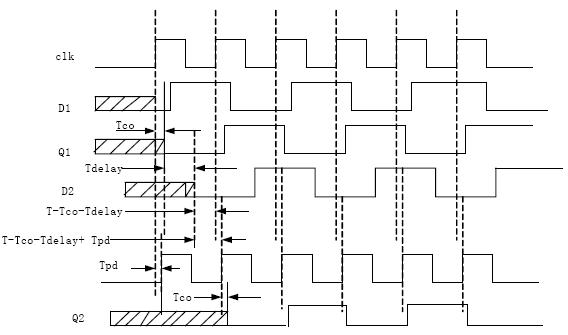

下面通過時序圖來分析:設第一個觸發器的輸入為D1,輸出為Q1,第二個觸發器的輸入為D2,輸出為Q2;

時鐘統一在上升沿進行採樣,為了便於分析我們討論兩種情況即第一:假設時鐘的延時Tpd為零,其實這種情況在FPGA設計中是常常滿足的,由於在FPGA設計中一般是採用統一的系統時鐘,也就是利用從全局時鐘管腳輸入的時鐘,這樣在內部時鐘的延時完全可以忽略不計。這種情況下不必考慮保持時間,因為每個數據都是保持一個時鐘節拍同時又有線路的延時,也就是都是基於CLOCK的延遲遠小於數據的延遲基礎上,所以保持時間都能滿足要求,重點是要關心建立時間,此時如果D2的建立時間滿足要求那麼時序圖應該如圖3所示。

從圖中可以看出如果:

T-Tco-Tdelay>T3

即: Tdelay< T-Tco-T3

那麼就滿足了建立時間的要求,其中T為時鐘的周期,這種情況下第二個觸發器就能在第二個時鐘的升沿就能穩定的採到D2,時序圖如圖3所示。

圖3 符合要求的時序圖

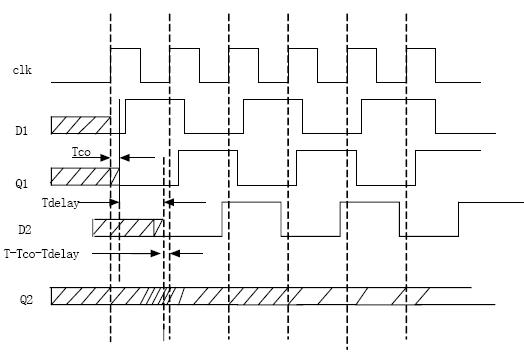

如果組合邏輯的延時過大使得

T-Tco-Tdelay<T3

那麼將不滿足要求,第二個觸發器就在第二個時鐘的升沿將採到的是一個不定態,如圖4所示。那麼電路將不能正常的工作。

圖4 組合邏輯的延時過大時序不滿足要求

從而可以推出

T-Tco-T2max>=T3

這也就是要求的D2的建立時間。

從上面的時序圖中也可以看出,D2的建立時間與保持時間與D1的建立與保持時間是沒有關係的,而只和D2前面的組合邏輯和D1的數據傳輸延時有關,這也是一個很重要的結論。說明了延時沒有疊加效應。

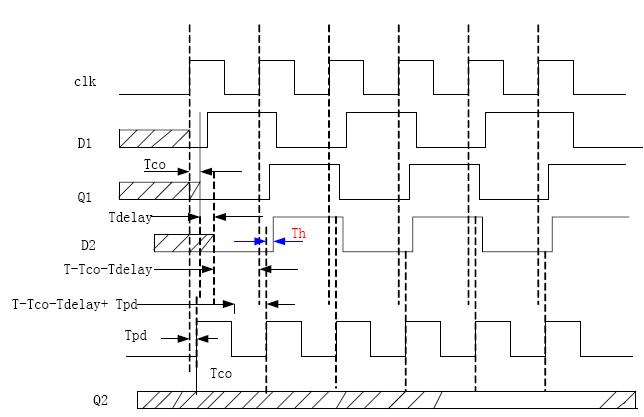

第二種情況如果時鐘存在延時,這種情況下就要考慮保持時間了,同時也需要考慮建立時間。時鐘出現較大的延時多是採用了非同步時鐘的設計方法,這種方法較難保證數據的同步性,所以實際的設計中很少採用。此時如果建立時間與保持時間都滿足要求那麼輸出的時序如圖5所示。

圖5 時鐘存在延時但滿足時序

從圖5中可以容易的看出對建立時間放寬了Tpd,所以D2的建立時間需滿足要求:

Tpd+T-Tco-T2max>=T3

由於建立時間與保持時間的和是穩定的一個時鐘周期,如果時鐘有延時,同時數據的延時也較小那麼建立時間必然是增大的,保持時間就會隨之減小,如果減小到不滿足D2的保持時間要求時就不能採集到正確的數據,如圖6所示。

這時即T-(Tpd-Tco-T2min)<T4,就不滿足要求了,所以D2的保持時間應該為:

T-(Tpd+T-Tco-T2min)>=T4 即Tco+T2min-Tpd>=T4

從上式也可以看出如果Tpd=0也就是時鐘的延時為0那麼同樣是要求Tco+T2min>T4,但是在實際的應用中由於T2的延時也就是線路的延時遠遠大於觸發器的保持時間即T4所以不必要關係保持時間。

圖6 時鐘存在延時且保持時間不滿足要求

綜上所述,如果不考慮時鐘的延時那麼只需關心建立時間,如果考慮時鐘的延時那麼更需關心保持時間。下面將要分析在FPGA設計中如何提高同步系統中的工作時鐘。

1.2 如何提高同步系統中的工作時鐘

從上面的分析可以看出同步系統時對D2建立時間T3的要求為:

T-Tco-T2max>=T3

所以很容易推出T>=T3+Tco+T2max,其中T3為D2的建立時間Tset,T2為組合邏輯的延時。在一個設計中T3和Tco都是由器件決定的固定值,可控的也只有T2也就時輸入端組合邏輯的延時,所以通過盡量來減小T2就可以提高系統的工作時鐘。為了達到減小T2在設計中可以用下面不同的幾種方法綜合來實現。

1.2.1 通過改變走線的方式來減小延時

以altera的器件為例,我們在quartus裡面的timing closure floorplan可以看到有 很多條條塊塊,我們可以將條條塊塊按行和按列分,每一個條塊代表1個LAB,每個LAB里 有8個或者是10個LE。它們的走線時延的關係如下:同一個LAB中(最快) < 同列或者同行 < 不同行且不同列。 我們通過給綜合器加適當的約束(約束要適量,一般以加5%裕量較為合適,比如電路 工作在100Mhz,則加約束加到105Mhz就可以了,過大的約束效果反而不好,且極大增加綜合時間)可以將相關的邏輯在布線時盡量布的靠近一點,從而減少走線的時延。

[admin via 研發互助社區 ] 影響FPGA設計中時鐘因素的探討已經有2640次圍觀

http://cocdig.com/docs/show-post-43060.html