1. FPGA和SOPC概述

1.1 FPGA的特點及最新進展

嵌入式系統是一個面嚮應用、技術密集、資金密集、高度分散、不可壟斷的產業,隨著各個領域應用需求的多樣化,嵌入式設計技術和晶元技術也經歷著一次又一次的革新。雖然ASIC的成本很低,但設計周期長、投入費用高、風險較大,而可編程邏輯器件(Programmable Logical Device)設計靈活、功能強大,尤其是高密度現場可編程邏輯器件(Field Programmable Gate Array)其設計性能已完全能夠與ASIC媲美,Xilinx公司最新推出的SpartanIII系列高性價比FPGA,其批量成本已經達到10美元/100萬門的成都,其性能價格比已足以與ASIC抗衡。因此,FPGA在嵌入式系統設計領域已佔據著越來越重要的地位。

FPGA的基本結構由以下幾個部分構成:

隨著工藝的進步和應用系統需求,一般在FPGA中還包含以下可選資源:

以FPGA為核心的PLD產品是近幾年集成電路中發展得最快的產品。隨著FPGA性能的高速發展和設計人員自身能力的提高,FPGA將進一步擴大可編程晶元的領地,將複雜專用晶元擠向高端和超複雜應用。目前FPGA的發展趨勢主要體現在以下幾個方面:

隨著處理器以IP的形式嵌入到FPGA中,ASIC和FPGA之間的界限將越來越模糊,未來的某些電路版上可能只有這兩部分電路:模擬部分(包括電源)和一塊FPGA晶元,最多還有一些大容量的存儲器。Xilinx等公司最新一代FPGA:Spartan II/E、Virtex II Pro,尤其是SpartanIII及其相關IP Core的推出,使我們有理由相信,可編程片上系統(System on Programmable Chip)的時代已經離我們不遠了。

1.2可編程片上系統(SOPC)的基本特徵

可編程片上系統(SOPC)是一種特殊的嵌入式系統:首先它是片上系統(SOC),即由單個晶元完成整個系統的主要邏輯功能;其次,它是可編程系統,具有靈活的設計方式,可裁減、可擴充、可升級,並具備軟硬體在系統可編程的功能。

SOPC結合了SOC和FPGA各自的優點,一般具備以下基本特徵:

SOPC設計技術實際上涵蓋了嵌入式系統設計技術的全部內容,除了以處理器和實時多任務操作系統(RTOS)為中心的軟體設計技術、以PCB和信號完整性分析為基礎的高速電路設計技術以外,SOPC還涉及目前以引起普遍關注的軟硬體協同設計技術。由於SOPC的主要邏輯設計是在可編程邏輯器件內部進行,而BGA封裝已被廣泛應用在微封裝領域中,傳統的調試設備,如:邏輯分析儀和數字示波器,已很難進行直接測試分析,因此,必將對以模擬技術為基礎的軟硬體協同設計技術提出更高的要求。同時,新的調試技術也已不斷湧現出來,如Xilinx公司的片內邏輯分析儀Chip Scope ILA就是一種價廉物美的片內實時調試工具;而在應對複雜設計方面,諸如Xilinx公司的System Generator for DSP就是一個利用可編程硬體邏輯實現數字信號處理演算法的強大輔助工具。

2. 基於Xilinx FPGA的SOPC設計方法

2.1 FPGA基本開發流程與開發工具介紹

FPGA基本開發流程主要包括設計輸入(Design Entry);設計模擬(Simulation);設計綜合(Synthesize);布局布線(Place & Route);配置(Configuration)五個主要步驟。

設計輸入主要有原理圖輸入和HDL輸入兩種方式,一般開發商都同時支持兩種輸入方式。有些熟悉硬體設計的工程師開始喜歡利用原理圖進行設計,這種方法非常直觀,但基於可移植性和規範化方面的考慮,絕大部分深入FPGA設計和ASIC設計的工程師最終都將統一到HDL平台上來。

設計模擬包含功能模擬和時序模擬兩項主要內容,功能模擬忽略了綜合和布局布線導致的時延等因素,僅僅從邏輯上進行模擬,這對設計思路的驗證是有幫助的,但必須通過時序模擬作進一步驗證,發現並修正時序問題。

設計綜合將HDL語言生成用於布局布線的網表和相應的約束。綜合效果直接導致設計的性能和邏輯門的利用效率,因此,許多可編程邏輯器件開發商都支持第三方綜合和模擬工具,著名的有:Synplicity、Synopsys和ModelSim等。

布局布線工具利用綜合生成的網表,在FPGA內部進行布局布線,並生成可用於配置的比特流文件。布局布線工具與可編程邏輯器件工藝及其布線資源密切相關,一般由可編程邏輯器件開發商直接提供。

隨著可編程邏輯器件容量的不斷增大和設計性能要求的不斷提高,對傳統的FPGA開發工具提出了挑戰。以Xilinx公司為例,應IP Core開發和集成的需要,開發了IP Core使用工具Core Generator並內嵌了IP Core包裝工具IP Capture;提供了模塊化設計工具Modular Design用於超大規模設計的團隊項目開發;用片內邏輯分析儀ChipScope ILA進行片內邏輯調試;Xpower則用於設計功耗分析並得出相應的解決方案;還有System Generator結合Simulink甚至可以簡單地實現數字信號處理模型(如FIR濾波器和FFT等)的FPGA硬體實現。此外,一些有爭議的設計工具,如基於C語言的FPGA開發工具DK1等為超大容量FPGA設計和複雜邏輯設計提供了值得嘗試的途徑。

2.2 處理器IP Core:Micro Blaze

將處理器IP Core嵌入到可編程邏輯器件是基於FPGA的嵌入式系統設計的前提條件,目前,國內外許多單位已成功的將51單片機、ARM和PPC等處理器內核嵌入各種可編程邏輯器件並進行了應用系統的設計,其中最著名的要數Xilinx公司的Micro Blaze和Altera公司的Nois了。Xilinx從Pico Blaze到Micro Blaze,再到PPC405,完成了從8位單片機到32位微處理器的逐步完善和性能提升。

Micro Blaze 是一個專門為Xilinx FPGA優化的RISC嵌入式軟處理器,符合IBM Core Connect標準,能夠與PPC405系統無縫連接,Micro Blaze軟處理器內核的結構如圖2所示,它具備以下基本特徵:

Micro Blaze是一個非常簡化,但有具有較高性能的軟處理器內核,他可以在性價比很高的Spartan II(-E)系列FPGA上實現,系統時鐘頻率為75MHZ,僅佔用400個Slice資源,相當於10萬門FPGA容量的三分之一,而10萬門的Spartan II系列FPGA的批量目標市場價格僅為10美元左右,非常適合消費類嵌入式產品應用需求。

2.3 基於EDK3.2的SOPC軟硬體開發

基於嵌入式處理器內核的SOPC系統開發是一個軟硬體協同設計的過程,一方面,它極大地提高了系統設計的靈活性和快速的設計迭代周期,使整個開發過程變得更加可控;另一方面,一些新的調試和設計問題,如邏輯分析儀和數字示波器的接入等,對調試設備和調試手段提出了更高的要求,為了儘可能避免問題的產生,要求有更好的設計工具和集成開發環境,保證IP Core資源的可用性和設計實現的一致性,讓設計工程師從煩瑣的內部時序調試中解放出來。

Xilinx提供了針對Micro Blaze Core應用系統開發的集成開發環境EDK3.2,該開發環境包含了用於硬體描述和系統生成的Platform Generator、用於軟體設計和編譯的Micro Blaze IDE,GDB調試可通過FPGA配置JTAG介面進行,無需任何附加的調試硬體,配合Foundation ISE5.2和FPGA目標板即可進行全功能開發,EDK還包含了UART、GPIO、Watchdog、Timer/Counter、EMC和中斷控制等基本處理器外設庫,用戶可以添加兼容OPB匯流排標準的任意IP Core。Insight和依元素科技均提供了功能全面的Micro Blaze Core評估工具。

PPC405 Core是一個高性能的處理器內核,它具有獨立於FPGA JTAG的調試埠和更加複雜的調試功能,我們甚至可以將基於PPC405 Core的SOPC調試直觀地理解為基於IBM PPC405處理器和大容量FPGA的單板機調試,只不過這個單板機無需進行傳統的PCB設計和調試,設計迭代過程全部在計算機上進行。PPC405 Core的軟體集成開發環境支持傳統的IBM PPC405開發環境,Xilinx提供了相應的系統集成開發環境和GNU軟體開發工具包支持。第三方軟體開發商Wind River和Montvisa已分別宣布其VxWorks和HardHat Linux實時操作系統(RTOS)及其集成開發環境支持Virtex II Pro 系列FPGA,Insight和Avnet已開始銷售含有Virtex II Pro FPGA的高端評估板。依元素科技也推出了用於開發PowerPC系列處理器的GNU集成開發工具和利刃®系列調試工具,以及含有PowerPC處理器的原型評估板。

2.4 基於ChipScope Pro的FPGA調試技術

新一代FPGA器件所具有的規模、速度和板級要求使得利用傳統邏輯分析方法來調試採用FPGA器件進行的設計幾乎是不可能的。CS和BGA封裝無法提供進行物理探測用的外露引腳。為了解決這些問題,Xilinx公司推出了ChipScope Pro 片內邏輯分析儀解決方案。基於開創性的ChipScope ILA產品,ChipScope Pro實際上是將邏輯分析儀(ILA)和匯流排分析儀(IBA)核心嵌入到了您的設計中。這些嵌入核心允許用戶觀察所使用的FPGA器件中的所有內部信號和結點,此外還包括對業界領先的Virtex-II Pro™ FGPA 器件內所集成的IBM PowerPC 405處理器的IBM CoreConnect片上外設匯流排的分析支持。

ChipScope Pro主要包含以下幾個核心部件:

(1) ChipScope Pro核心生成器:為綜合控制器(ICON)核心、CoreConnect™ OPB的匯流排分析核心(IBA/OPB)、邏輯分析(ILA)核心及安捷倫跟蹤核心(ILA/ATC)提供網表和實例化的模板;

(2) ChipScope Pro核心插入器:自動地為用戶已經綜合完的設計中插入ICON、ILA和ILA/ATC的核心;

(3) ChipScope Pro分析儀軟體:提供器件的配置、觸發的設定和ILA、IBA/OPB及ILA/ATC核的蹤跡顯示功能。各種核心實現了信號的觸發和捕獲,而ICON核心專門用於與邊界掃描(Boundary Scan)管腳的通信。

ChipScope Pro分析儀軟體支持所有通過JTAG邊界掃描鏈連接PC與器件的下載電纜,如Xilinx的並口電纜 Cable III、Cable IV和依元素提供的利刃系列下載調試電纜等。

用戶可以使用ChipScope Pro 核心生成器生成的例示代碼插入HDL源程序中,從而將ICON、ILA等核心插入到他們的設計中。當然,你也可以使用ChipScope Pro核心插入器將ICON、ILA等核心直接插入到已經綜合完成的設計網表中。然後,利用Xilinx ISE 5.2i的綜合工具進行綜合布線,生成配置文件。這樣用戶就可以通過ChipScope Pro分析儀軟體將配置數據流下載到待測的器件中,進行分析測試。

3. IP Core設計及其在SOPC中的應用

3.1 IP資源復用與IP Core設計方法

由於晶元設計的複雜性和產品面市時間對於保證終端市場的成功率至關重要,設計師不斷尋求縮短設計周期的方法,以及更有效的設計方式。隨著我們步入系統級晶元時代,利用IP內核和可編程邏輯進行設計復用顯得日趨重要。IP資源復用(IP Reuse)是指在集成電路設計過程中,通過繼承、共享或購買所需的智力產權內核,然後再利用EDA工具進行設計、綜合和驗證,從而加速流片設計過程,降低開發風險。IP Reuse已逐漸成為現代集成電路設計的重要手段,在日新月異的各種應用需求面前,超大規模集成電路設計時代正步入一個IP整合的時代。

IP Core是IP Reuse的載體和核心內容,基於應用需求、規範協議和行業標準的不同,IP Core的內容也是千差萬別的。但是,為了使IP Core易於訪問和易於集成,其設計必須遵循一定的規範和準則。 在IP Core的開發方面,許多開放性的團體都付出了巨大的努力來推動各種IP Core的開發和IP Reuse理念的推廣,其中比較著名的是Open Cores開發組織(http://www.opencores.org)。他們不僅開發了許多開放源代碼的IP Core,涵蓋了處理器IP、處理器外設控制器IP、算術運算單元IP、DSP演算法IP等方面,而且編寫了詳細的IP Core編碼風格和項目模板。國內開放性團體IP Core開發小組(http://www.IPcore.com.cn)也在IP Core開發和IP Reuse理念的推廣和普及方面進行了不懈努力。

編碼風格(Coding Style)是基於HDL的IP Core源碼編寫的指導性文檔,其可讀性直接關係到IP Core的易於訪問和易於集成性。編碼風格一般包含幾個方面的約定:文件頭和版本說明、聯機註釋、命名規則、可綜合編碼等。

項目模板則規定了完成一個IP Core設計包含的主要內容及所需提供的文檔,項目模板內容及其文檔直接關係到IP Core的易於集成特性,一個IP Core必須是完整的、經過全面驗證的,才能順利地集成到應用項目中去。項目模板一般包含幾個方面的內容:項目定義、介面說明、系統結構和模塊、設計文檔說明、測試驗證報告、約束和實現、版本說明、試用評價以及參考文獻等。

3.2 IP Core驗證:模擬、測試與評估板

IP Core設計在完成編碼階段以後,對其功能的測試驗證是一項非常重要的內容,因為這直接關係到IP Core資源的可用性。僅僅通過功能模擬、時序模擬和測試向量驗證的IP Core是不完備的,它必須通過實際系統的驗證。國際上各大公司通常採用的辦法是評估板驗證,也即構建一個與實際系統IP Core應用一致的硬體環境,通過下載FPGA配置使其具備相應的邏輯功能,並進行實物模擬,圖3是依元素科技開發的專用於SOPC和IP Core設計驗證的評估板實物照片和原理框圖。

4. SOPC設計應用實例:單晶元動態可重構信號處理器

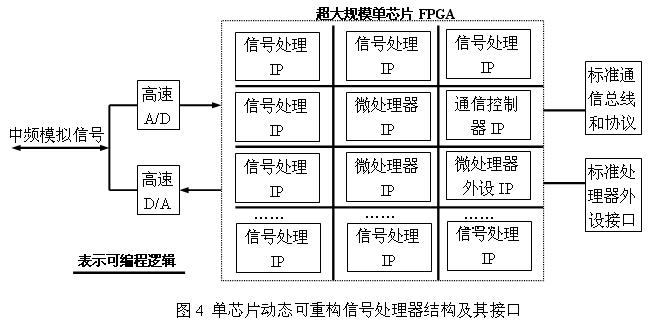

數字信號處理器是一種為高度密集運算量而專門優化的嵌入式處理器,典型的有TI的TMS320系列和AD公司的ADSP,其中TI公司最新產品TMS32C641X系列處理器工作頻率高達1GHZ,而處理能力可達數GFLOPS。但是,歸根結底,數字信號處理器還是一種基於軟體程序順序執行指令的串列處理器,從微觀上看,處理器中某一特定時刻,只有一個算數邏輯單元(MAU)在執行特定的指令,如果要在硬體上實現多個MAU并行,只能通過將多個DSP器件并行處理,這樣必然導致PCB設計及調試方面複雜性的大幅度提高,而且DSP器件之間的藕合程度、處理任務劃分與進程間通信等方面的靈活性也存在一定問題。基於可編程邏輯器件實現的可編程片上系統設計技術則從很大程度上克服了上述問題,SOPC的處理器IP、控制器IP、信號處理演算法IP等各種數字邏輯都是基於可編程邏輯在同一個FPGA晶元內部實現,可以任意添加、裁減以及改變連接關係,而且它們之間的互連方式是比板級PCB互連更具有緊藕合特徵的片內互連。

基於SOPC設計技術實現的單晶元動態可重構信號處理器結構及介面如圖4所示:

5. 結束語

隨著新新一代超大規模可編程邏輯器件工藝的不斷進步和開發工具的不斷完善,以FPAG為基礎的SOPC技術將更加廣泛的應用在各個領域,FPGA的將在更廣泛的範圍普及,成本和價格將不再成為我們拒絕在設計中採用FPGA的理由。我們有理由相信,SOPC、IRL等設計理念將會對我們的設計方式產生新的變革,也必將給每一位嵌入式工程師帶來有益的思路和更加寬廣的創意空間,從而為更新日益加速的嵌入式產品設計注入新的活力。

[admin via 研發互助社區 ] 可編程片上系統(SOPC)設計技術已經有2316次圍觀

http://cocdig.com/docs/show-post-43059.html