我們的設計需要多大容量的晶元?我們的設計能跑多快?這是經常困擾工程師的兩個問題.對於前一個問題,我們可能還能先以一個比較大的晶元實現原型,待原型完成再選用大小合適的晶元實現.對於後者,我們需要一個比較精確的預估,我們的設計能跑50M,100M 還是133M?

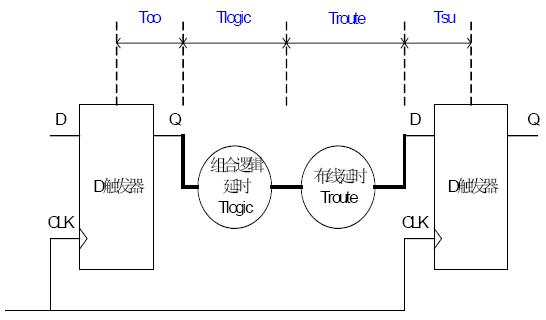

首先讓我們先來看看Fmax 是如何計算出來的.圖(1)是一個通用的模型用來計算FPGA的.我們可以看出,Fmax 受Tsu , Tco , Tlogic 和 Troute 四個參數影響.( 由於使用FPGA 全局時鐘,時鐘的抖動在這裡不考慮).

時鐘周期 T = Tco + Tlogic + Troute + Tsu

時鐘頻率 Fmax = 1/Tmax

其中:

Tco : D 觸發器的輸出延時

Tlogic : 組合邏輯延時

Troute : 布線延時

Tsu : D 觸發器的建立時間

圖( 1 ) 時鐘周期的計算模型

由圖(1)可以看出,在影響Fmax 的四個參數中,由於針對某一個器件Tsu 和Tco 是固定的,因此我們在設計中需要考慮的參數只有兩個Tlogic 和Troute.通過良好的設計以及一些如Pipeline 的技巧,我們可以把Tlogic 和Troute 控制在一定的範圍內.達到我們所要求的Fmax.

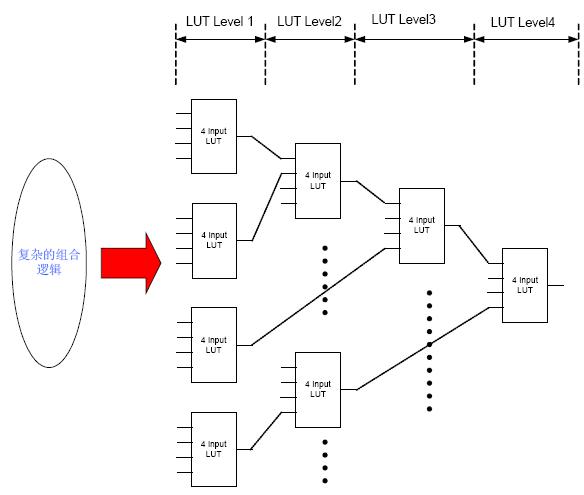

經驗表明一個良好的設計,通常可以將組合邏輯的層次控制在4 層以內,即( Lut Levels <=4 ) .而Lut Levels( 組合邏輯的層次 )將直接影響Tlogic 和Troute 的大小. 組合邏輯的層次多,則Tlogic 和Troute 的延時就大,反之, 組合邏輯的層次少,則Tlogic 和Troute 的延時就小.

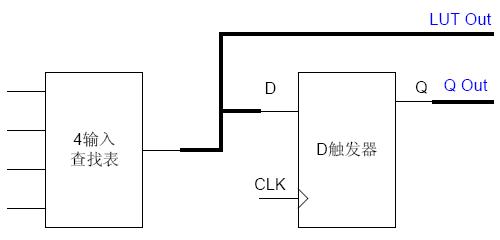

讓我們回過頭來看看Xilinx 和Altera 的FPGA 是如何構成的.是由Logic Cell ( Xilinx )或 Logic Element( Altera )這一種基本結構和連接各個Logic Cell 或Logic Element 的連線資源構成.無論是Logic Cell 還是 Logic Element ,排除其各自的特點,取其共性為一個4 輸入的查找表和一個D 觸發器.如圖(2)所示.而任何複雜的邏輯都是由此基本單元複合而成.圖(3).上一個D 觸發器的輸出到下一個D 觸發器的輸入所經過的LUT 的個數就是組合邏輯的層次( Lut Levels ).因此,電路中用於實現組合邏輯的延時就是所有Tlut 的總和.在這裡取Lut Levels = 4 .故Tlogic = 4 * Tlut .

圖( 2 ) FPGA基本邏輯單元

圖( 3 ) 複雜組合邏輯的實現

解決的 Tlogic 以後,我們來看看Troute 如何來計算.由於Xilinx 和Altera 在走線資源的設計上並不一樣,並且Xilinx 沒有給出布線延時的模型,因此更難於分析,不過好在業內對布線延時與邏輯延時的統計分析表明, 邏輯延時與布線延時的比值約為1:1 到1:2.由於我們所選用的晶元大量的已經進入0.18um 和0.13um 深亞微米的工藝,因此我們取邏輯延時與布線延時的比值為1:2.

Troute = 2 * Tlogic

Tmax = Tco + Tlogic + Troute + Tsu

= Tco + Tsu + 3 * Tlogic

= Tco + Tsu + 12 * Tlut

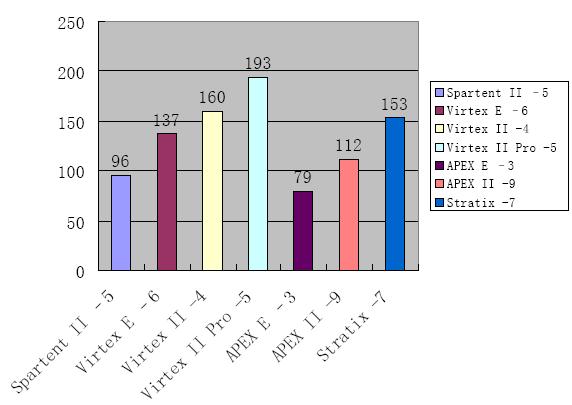

下表是我們常用的一些 Xilinx 和Altera 器件的性能估算.我們選取的是各個系列中的最低的速度等級.由於Altera 的APEX ,APEX II 系列器件的不同規模的參數不同,我們選取EP20K400E 和 EP2A15 作代表.

| Tsu ( ns ) | Tco ( ns ) | Tlut ( ns ) | Fmax | |

| Spartent II-5 | 0.7 | 1.3 | 0.7 | 96 M |

| Virtex E-6 | 0.63 | 1.0 | 0.47 | 137M |

| Virtex II-4 | 0.37 | 0.57 | 0.44 | 160M |

| Virtex II Pro -5 | 0.29 | 0.40 | 0.37 | 193M |

| APEX E-3 # | 0.23 | 0.32 | 1.01 | 79M |

| APEX II-9## | 0.33 | 0.23 | 0.7 | 112M |

| Stratix -7 | 0.011 | 0.202 | 0.527 | 153M |

[admin via 研發互助社區 ] 如何計算FPGA設計頻率已經有4268次圍觀

http://cocdig.com/docs/show-post-43039.html