CPLD的時代

我在12年前,偶然接觸PLD,沒有想到自己居然就在這個行當里安身下來。可是這個行業也的確是個飛速發展的行業,十多年過去后,從當初的接近十家主要供應商,到今天已經激烈搏殺后,只有差不多如論壇題目一樣的,成為了今天三足鼎立的局面。想來想去,決定以這個名字作為論壇的主題。同時也和大家分享我多年來的一些經歷和感受。

全局布線,ISP,PLD,宏單元機構,成為PLD市場必備的武器。

CPLD時代,進入我國最早的供應商是Lattice,那個時候,也不是每個行業都用的了這種產品。首先,軟體是需要收費的。這個和今天你可以輕鬆下載到免費的版本有很大的不同。另外,不同的授權,也決定你能使用不同的產品規模和設計語言。

90年代中,是電信行業大發展的年代。同時也是專用應用領域大發展的時代。當時pld是解決一個邏輯粘連的功能。同時由於Lattice很早進入市場, 推廣很成功。全局布線池的結構,對於布局布線要求不高。一度時間,很多大的通信企業,研究所,都很快成為Lattice的用戶。但是,有句話說得好。“長江後浪推前浪,前浪死在沙灘上。”太早的成功也孕育著。安則危!

94年Altera已經有了一些用戶。但是相對來說。還是很有局限性。另外過去的信息遠遠不可以與今天同日而語. 但是用過altera的工程師,已經為他的界面和功能留下了深刻的印象。96年是ALTERA在中國發力追趕的開始。當然,亂世出英雄。當時的代理商是一家香港的公司。他們很快找出這種集成電路最好的銷售和支持模式。並且這種從大洋那邊繼承過來的方式,經過適當的改良,的確收到很好的效果。代理商有專門負責的現場應用工程師。 這種方式極大方便了設計者與供應商之間的信息交流。在推廣初期是否有技術支持,變得非常重要。這個時期在整個中國市場上湧現出很多非常優秀的現場技術工程師。今天已經有很多人成為這個行業的領軍人物。

Lattice首開ISP技術先河,也就是今天常說的在線可編程,給所有設計者帶來很大的方便。晶元在電路板上,可以直接編程調試。不用每次拔插晶元,再通過紫外線來擦寫要方便得多。這個時候,Lattice還是明顯佔有上風的。畢竟先入為主嘛。當時主要的型號集中在Lattice ispLSI1032, 1016, Altera的EPM7128E,不過Altera已經做好了準備,因為,Altera畢竟是pld的發明者。而且也是最早採用Windows平台的開發工具。在美國市場上佔有先機。他不會輕易放棄這樣一個市場

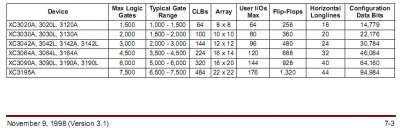

當時的應用在電信領域主要是將之前的74系列的一些單元進行集成。同時加入一些控制功能。不過這個時期的產品結構都是採用mc單元結構。每個mc實際上就是相當於32到36個與非門,以Altera EPM3032為例就是認為有32*30到256*30, 大致就是7000門左右,因此產品命名為MAX7000,但是當時的設計很多還在大量應用非同步設計。因此,電路的結構如果能導致利用率的上升,將是更加有競爭力的表現。MC的結構就是採用先組合,后時序多個時鐘輸入結構。Lattice是用4個宏單元一組。altera 採用8個一組。而且,altera在利用率上,稍微佔有上風。同時Altera當時的maxplusII的良好界面。在97,98年的兩年時間裡,已經奠定在中國的基礎。更深層次,Altera已經看到未來市場的需求,前面說到,成功太早有時候也不是好事。在MAX7000的鋪墊下,Altera已經有了進攻Xilinx的武器,可Altera一致宣稱那不是FPGA,換以一個更加中性的名字---CPLD(複雜可編程邏輯器件)。 那什麼是Altera的武器呢。FLEX8000!他的出現是Altera奠定今天可以和xilinx平分秋色的基礎。

在1996,97年, 成都,西安多家做專業領域的公司和研究單位,也使用了一些Actel,Actel的產品和那個時候的Quicklogic來說,都是屬於Antifuse的技術。 使用他的最大好處在當時就是有防止輻射,就是說在航空產品中可以用。 但是需要你認真的模擬。 如果你燒入進去設計, 就只能換下一片了。 而且為了燒斷裡面的熔絲, 第三方的編程器支持的也不多。 但是他們有些軍用溫度的產品。 還是在這個領域有不錯的口碑。

Actel當時的策略結構是, 基本上和他們現在的論調也非常一致, 就是精細顆粒, 所有的DFF,還是可以靠獨立的門來搭建。 這個在他早先的A1020等產品系列上可以看到。 而且晶元上有一部分是組合邏輯區, 有一部分是時序邏輯區。 另外他們的軟體也是多家EDA工具的組合。 特別是庫的一致性不是特別通用。

Quicklogic的產品是FPGA公司中最早嵌入Synplify的商家,而且他們的LE結構是基於Mux的,底層的layout也可以清晰看到路由,資源消耗。輸入法和庫的建立很特別。 但是也存在上面的問題。產品好像是QLxxx的,我還去應聘過一次這家公司,因為他們最早採用Synplify。而且,當時我已經感覺Synplify和 雷昂納多(拼寫忘記了),以及exzampler??這個拼寫也有問題。我在做FAE的時候,總是用這3個工具都綜合一次,看他們哪個強。後來證明是對的。Sy是最平均的,而且簡單的優點傻瓜。遺憾他也在今年被Synopsys收購了。現在Quicklogic也專註一些細分市場。

為什麼要這樣的結構-先組合,后時序多個時鐘輸入

隨著科技的進步,有很多人已經忘記了很多細節,當然,我們也要遵循一個原則。難事做易,大事做細!就像朱熹說的--“問渠哪得清如許,為有源頭活水來“,如果你不知道原理,碰到重要的問題,或者是設計的時候,即使成功,也是不知不覺成功,同樣呢,也是不知不覺失敗。

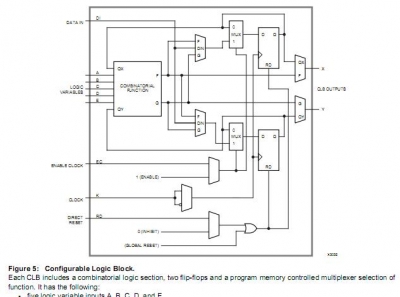

拉回話題,當你設計一個掃描電路的時候,例如,你可以採用一個時鐘,輸入一個計數器,然後計數器的輸出,再驅動一個解碼器,這樣你的電路就出來了。當然事情完成了一半。功能實現了,但是,有沒有更好的辦法。後者換句話說。有沒有適合PLD的方法。實際上用另外一個角度看,這個設計是典型的, 先時序模塊,才是組合電路。這個實際上,不是很和PLD本身的結構相符。還有一個問題時,隨著電路速度的提高,每個解碼輸出之間的抖動也成為問題。就是輸出的不一樣的。 從資源的角度來說,一個計數器,要3各單元。一個解碼器,由於有8個輸出,還是需要8各單元。但是如果用一個移位寄存器的方式,可以只需要8個單元。或者用狀態機的方式實現,也是消耗同樣的資源。可是,輸出都是由於同一個時鐘鎖定,每個輸出的延遲也比較一致。另外,當時對匯流排數據的解碼是經常有的事情,因此,每個單元的扇入數量都是很高的。都有30個以上。因此,你設計的時候,要有兩個思想: 用同步設計模式,用先組合后時序的模式。後來的Xilinx的95系列更是將扇入係數擴大到90個。 也是這個原因。當時PLD廠商比較的也是這些指標。

Xilinx , FPGA的發明者

Xilinx實際上成立的日期,比altera還晚了一年。但是他走的道路,從開始就註定了有今天的成就。在1996-1998,pld的高端市場,也就是FPGA市場,都是Xilinx把持,主要是xc3000/4000 ,當然Xilinx開創了一個新的結構,不過這種結構還是能夠找到一些共同點,也是先組合,后時序。不過很重要的閃亮點是:

細顆粒查找表結構,豐富的寄存器資源,以及分段式路由布線結構,電路上電載入。 當然如果這個也算是的話,那就是,他的內部甚至直接集成了三態門。這個特點是那個時代Xilinx擁躉攻擊Altera,Lattice的重要工具。甚至有人說,沒有這個不能實現某些電路設計的障礙。 當然了,Altera, Lattice的pld也是具有三態門,不過是在輸入輸出管腳上。的確是不如Xilinx的來的強大和直接。 有的人問了,這種結構有何好處。

在那個時代,衡量一個PLD很重要的指標,就是比誰的規模更大。從這個角度來看。Xilinx無疑走到了最前面。當然,也有人說, 這樣的設計不可靠。這樣的設計指標難以預測。還有地說這樣的設計無法保密。但是市場的成功,應用需求的推動,證明這些都是雜音。

我們可以從當時xc3000的選型指南上看到。最大規模的產品,也就是今天xilinx最小的xc3s50a規模相當的東西。可是這個和當時PLD流行的規模,實在是一個飛躍。

Xilinx FPGA的架構。

Xilinx的成功,激勵了Altera的新產品的推出。同時也有了革命性的突破。世界就是這麼奇怪。中國古語。塞翁失馬,焉知非福。實際上,如下所言,這款產品因該8282,具有282個邏輯單元的。但是在中國基本上只是在1995年有個別公司使用。

| 1992 | FLEX® 8000 FPGA | Altera的第一款現場可編程門陣列(FPGA) |

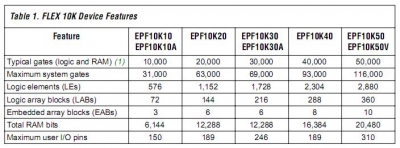

| 1996 | FLEX 10K® FPGA | 帶有集成鎖相環(PLL)的FPGA |

| 1995 | FLEX 10K FPGA | 帶有嵌入式模塊RAM的FPGA |

實際上,這個時間就是Lattice噩夢的開始,由於設計規模的迅速攀升,規模已經是決定一個產品的關鍵因素。但是Lattice一直沒有代表作。市場份額已經開始逐步被Xilinx,Altera蠶食。Altera的結構到底是什麼革新呢?

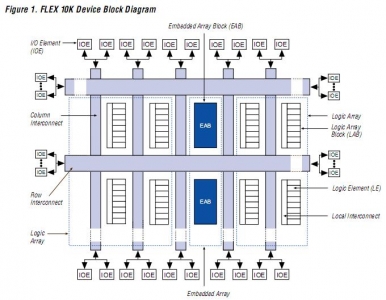

Altera FPGA粗顆粒結構,嵌入式存儲器,長聯線結構.

Flex10K,他的推出,已經表明,altera的思維已經非常清晰,大規模的fpga將會是將來的王道!而且,高速的嵌入式塊RAM是一個開創新的思維。當時,Xilinx憑藉分散式RAM以及內置三態的結構,的確大有橫掃千軍的架勢。但是Flex10K的出現,有效提升了Altera的FPGA產品的競爭力。在RAM需求應用不斷上升的市場中。Altera迎來了市場的春天。

Xilinx的分散式RAM儘管很靈活,但是隨著RAM容量的增加,訪問的速度也是遞減。同時也要消耗大量的邏輯資源。這個時候,應該說Xilinx和Altera的產品已經是勢均力敵。因為中國是新興的市場。這一點表現得很明顯.

規模製勝的產物

世界是運動的,粗顆粒,也是好結構!

這裡又回到了我們的主題,產品的內在結構。先說細顆粒結構。當時,Xilinx的3000是以CLB為基本機構。

實際上,這個輸入的個數是很有講究的。當時,也有一種激烈的爭論,就是5輸入的好,還是4輸入的好。在實際應用中,應該說,最小的邏輯單元是這樣的規模是合理的。但是要注意一點。Xilinx和Lattice後面推出的fpga一樣,兩個寄存器是具有同一個時鐘輸入的。

粗顆粒結構,Altera還是依託自己以前在PLD的經驗的積累,他的fpga有很多他的pld產品的血統。世界是基於以權制利的。因為這個時候如果已經有了Wintel的名字一樣。 數字電路以及CPU的發展,都和8以及8的倍數有關係。因此。這種大顆粒的結構確保:

Cyclone,Stratix,Vertex

Cyclone 的出現和FPGA的市場定位和產品定位

好的技術是需要,但是有效的市場定位和銷售策略也要跟上。在2002年左右,為了更好服務各種不同市場的需要。而且當時的DSP市場仍然不太明朗,有的觀望,也有大力投入。而且也有兩種不同的策略。

一種是同一個器件平台,但是不同的應用區隔,例如Vertex和Spartan,有一段時間,他們可能是同一個產品平台,只是Spartan的東西就是Vertex屏蔽了一部分高級的性能,對於不使用的地方,也不需要檢測,同時依靠同一個平台來維持成本優勢。

另外一種,就是Altera的策略,完全依賴客人市場的需要,簡化不需要的特性,推出簡化的結構,面向主要的邏輯集成和LVDS信號鏈集成。推出Cyclone,市場反響非常強力,是Altera有史以來,市場響應最快的產品。

today's:看得很爽。但是那個“先組合后時序”的方法,要怎麼設計才能符合這樣的設計要求,我想了很久也沒想出來。

wisdomz:實際上, 有很多講述如何避免毛刺,或者是提高系統穩定性,以及全同步的時鐘設計概念。都是採用了類似的含義。

1--毛刺消除

有後面的DFF以高的頻率,進行打一次的動作,毛刺可以被消除

2--系統的模塊間如果有DFF進行輸出,或者輸入的隔離,那麼你可以很好加入探針,通常優化綜合是不會將DFF給幹掉的。

3--全同步,就是現在的時序分析工具是基於全同步的,如果有兩個不同的時鐘,你就要加入這兩個時鐘間的相對關係。來進行約束。 最後要說,你已經花錢買了這個FPGA上的整個資源。就要為了設計的穩定性, 應該把這些為了使你設計穩定而增加的資源給利用了!說的是不是太繞了呢?

today's:1和2懂了,但只是在我設計完的數字邏輯中插入D觸發器,來增加穩定性,或方便測試。3也懂,但是不知道和“先組合后時序”有何關聯呢。但總的來說我還是在用“先時序后組合”的方式,就是先設計時序電路,由時序電路輸出再經過組合邏輯得到最終輸出,不知樓主所說“先組合后時序”與我慣用的方式的根本區別在哪裡?

wisdomz:就是先設計時序電路,由時序電路輸出再經過組合邏輯得到最終輸出,不知樓主所說“先組合后時序”與我慣用的方式的根本區別在哪裡?

1--實現一個8路輸出的掃描電路,每個之間都是一個有一定相位差的方波。

如果用先計數器, 然後再用解碼,這個是採用線性思維,what和when的思考模式,非常合乎常情。但是, 當速度高的時候,每個輸出之間由於解碼長度傳輸不同,就導致毛刺多。

而且,你的邏輯資源也會是,組合+ 時序,(計數器實現),再加上組合(後面解碼),最後,你的那個時序資源就是DFF,就浪費了。 要不就是再次用高速clk打一次,要不就是先組合,后時序,用掃描狀態機,或者就是移位寄存器實現。這個就是系統思維模式,是How和why的思考方式。

你認為哪一種更好呢?相信你已經找到答案了。

[admin via 研發互助社區 ] FPGA三國志-第一篇/不可不看的故事已經有2428次圍觀

http://cocdig.com/docs/show-post-43033.html