寬頻視頻切換集成電路AD8108,AD8109中資料

摘要:介紹了AD8108,AD8109的主要功能、工作原理、控制邏輯的編程方法,指出了用AD8108設計8×16視頻切換系統的軟、硬體設計時應注意的幾個問題。實踐表明,該切換系統可靠性好,抗干擾能力強。

視頻矩陣切換器主要用於電視視頻領域。隨著計算機技術、多媒體技術的發展,它的應用範圍越來越廣泛。基於此,許多大公司紛紛推出了寬頻視頻切換集成電路。其中美國模擬器件公司生產的AD8108/AD8109不僅集成了許多分立元件實現的功能,而且成本低、使用壽命長、電磁兼容性好、擴展性好。本文從寬頻視頻切換集成電路AD8108/AD8109的功能入手,著重討論了其工作原理和控制邏輯和編程,並結合AD8108的應用對應用時需注意的問題進行了討論。

1 AD8108/AD8109的功能原理

AD8108/AD8109是一種高速8×8的視頻切換矩陣,其-3 dB帶寬大於250 MHz,通道切換時間少於25 ns,且其損耗小於l%。AD8108/AD8109在5 MHz時僅有-83 dB的串擾和-98dB的隔離度,具有優於0.02%,0.02°的微分增益誤差/微分相位誤差。由於其具有0.1 dB的增益平坦度,從而使AD8108/AD8109成為視頻信號切換的理想器件。

1.1 引腳功能

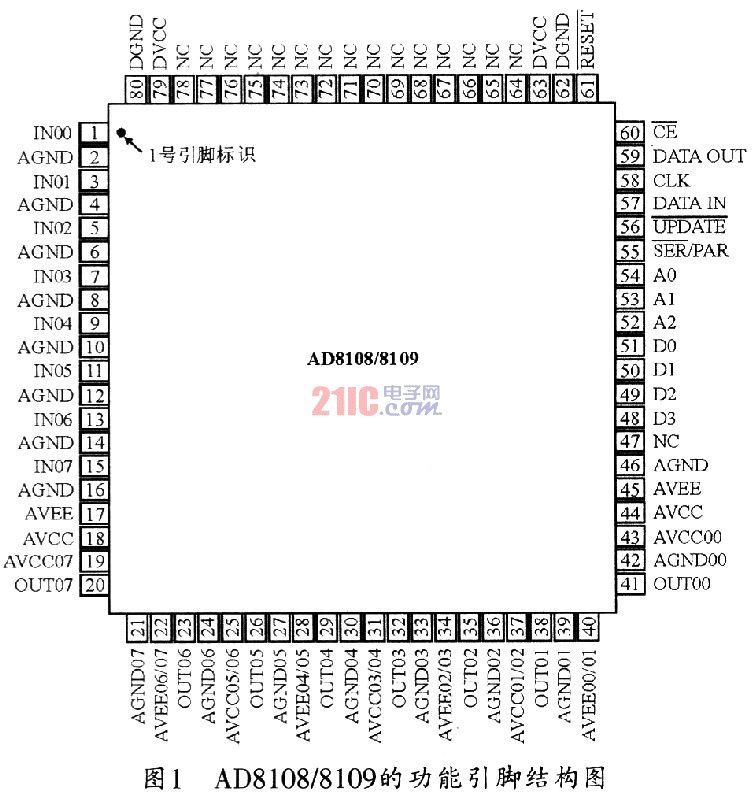

AD8108/AD8109採用TQFP封裝,共有80引腳,其引腳結構如圖1所示。各主要引腳的功能如下:

INxx:模擬輸入通道,xx表示通道號00~07;

DATA IN:串列數據輸入,兼容TTL電平;

CLK:時鐘,下降沿有效,兼容TTL電平;

DATA OUT:串列數據輸出,兼容TTL電平;

:數據控制端。為低時,允許寄存器數據直接送到開關矩陣;為高時,鎖存數據;

:晶元使能端,低電平有效;

:複位端,低電平有效;

:工作方式選擇端。低電平,選擇串列模式:高電平時,選擇并行模式。

OUTyy:模擬輸出,yy表示通道號00~07;

A2~A0:并行數據輸入端,兼容TTL電平,

其中A0是最低位;

D2~D0:并行數據輸入端,兼容TTL電平,

其中D0是最低位;

D3:并行數據輸入輸出使能,與TTL兼容。

NC:懸空端。

其它還有比如模擬地(AGND)、數字地(DGND)、模擬負電源(AVEE)、模擬正電源(AVCC)等都比較容易理解,此處不再贅述。

1.2 工作原理

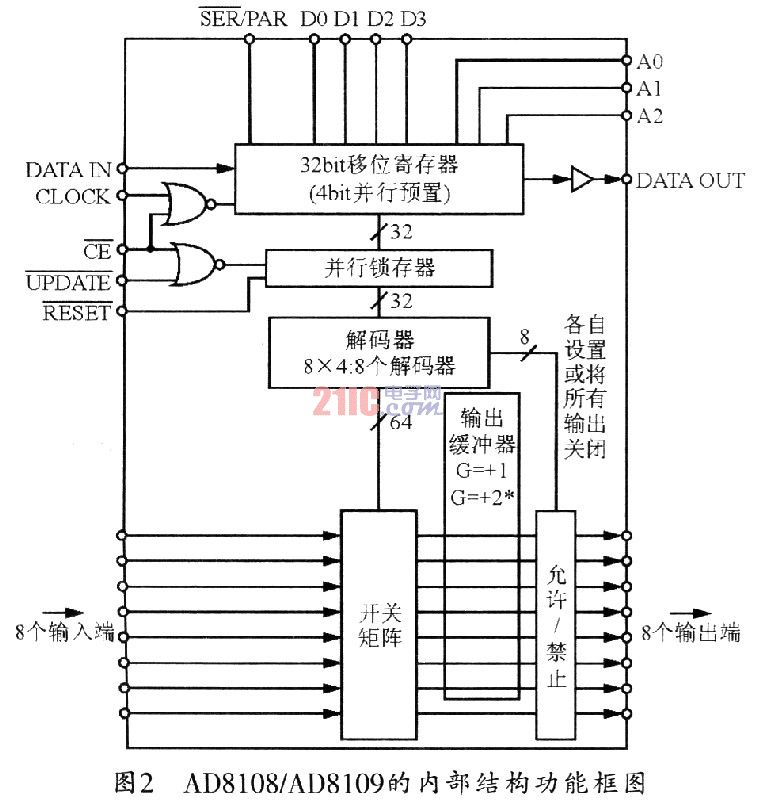

AD8108(G=1)和AD8109(G=2)具有相同的內核。其容量都是8×8。主要由32 bit移位寄存器、并行鎖存器、解碼器、64點的切換矩陣和輸

出緩衝器等部分組成,圖2是其內部結構框圖。

由圖2可以看出,AD8108/AD8109有兩種控制方式,它們均通過晶元內的32 bit移位寄存器對8路輸入和8路輸出進行切換控制。

當為低電平時,選擇串列模式。在該模式下,以默認的順序確定輸出埠,而不用輸入地址。AD8108/AD8109有8個輸出埠,分別對應4bit數據,即D3~DO。其中D3用來阻斷或使能該輸出埠,當D3為0時,D2~DO無效,相應的輸出埠阻斷。D2~DO用來確定與某個輸出埠相連接的輸入埠。DATA IN通過CLK信號的下降沿驅動,依次傳輸OUT7[D3]、OUT7[D2]、OUT7[D1]、OUT7[D0]、 ……、OUT0[D3]、OUT0[D2]、OUT0[Dl]、OUT0[D0]數據到晶元內的32bit移位寄存器中,並由移位寄存器控制輸入信號和輸出信號的對應切換關係。當32bit數據全部輸入完畢時,停止CLK信號,變為低電平,同時根據剛輸入的32bit數據來切換矩陣的輸入和輸出。若CLK信號沒有停止,則切換矩陣數據動態更改。當變為高電平時,32 bit數據鎖存完畢。採用串列模式的特點是使用的控制信號少,但速度慢:同時每次更改輸入輸出配置時,必須提供32 bit的串列數據,這樣才能將整個矩陣數據更改:此外,串列數據輸出端也可為構建大容量的矩陣切換器提供方便,此時,只需將一個晶元的DATA OUT端連接到另一個晶元的DATA IN,而其它(如CLK、、、)則應該并行連接。

當為高電平時。選擇并行模式。在該模式下,當為低電平,設置為高電平且在CLK下降沿時,包括、A2~A0、D3~DO在內的引腳上的邏輯值都將進入帶有4位并行載入功能的32位移位寄存器中。至於4位數據D3~D0裝入到32位移位寄存器的哪一個4位單元,則由A2~A0決定。A2~A0將32位移位寄存器分成8個4位單元段,每一個4位單元段對應一個輸出緩衝器。當為低電平時,上述移位寄存器的內容進入并行鎖存模塊,然後經8x4:8解碼后,即可對開關矩陣進行控制,以實現由D3、D2~D0、A2~A0決定8路輸入中的任一路輸入向8路輸出中的任一路輸出。并行模式的特點:一是使用的控制信號多,但速度快;二是在改變單個輸出通道的工作方式時,不需要重新編程設置整個切換矩陣。

2 時序及控制邏輯編程

AD8108/AD8109的信號通道帶寬不低於250MHz(-3dB),高於計算機視頻信號和許多雷達視頻脈衝的帶寬,因而可用於複合視頻、分量

視頻、壓縮視頻等許多寬頻帶信號的切換;該晶元將輸出緩衝器集成在晶元內,減少了寄生電容,且使它的抗干擾能力較強;這種高密度集成模塊更便於集成更大規模的視頻矩陣切換電路;器件有串列或并行兩種控制方式,其控制都比較簡單,而且驅動能力強,能驅動150Ω負載。此外,該晶元功耗低,工作電流僅45 mA,並有輸出禁止功能,可允許多個晶元的輸出直接連接。

2.1 時序圖

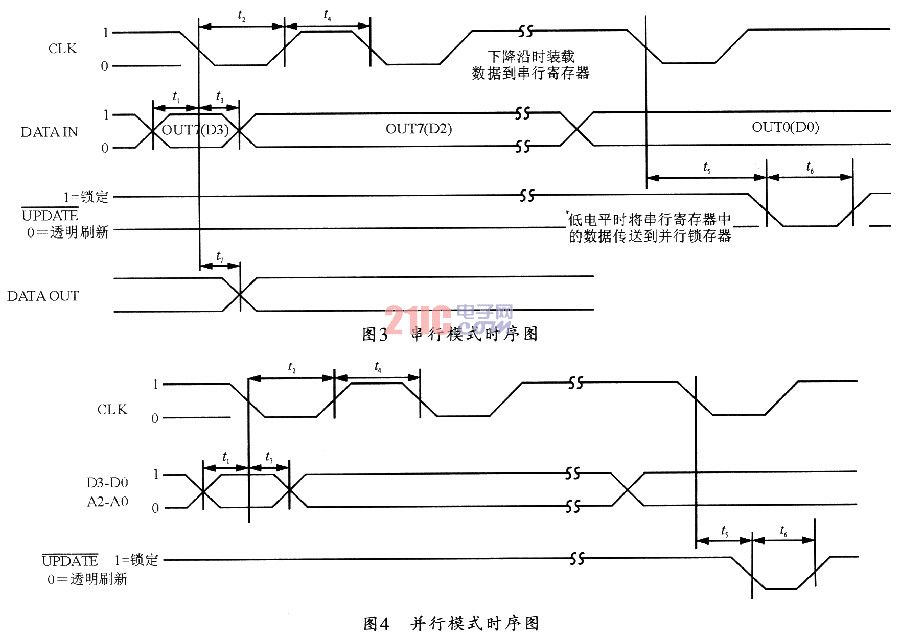

AD8108/AD8109的串列模式時序圖如圖3所示。圖中,其時鐘信號CLK和刷新信號均是下降沿有效。特別應當注意的是,數據的建立時間t1最少為20 ns,的鎖存時間t6最少為50 ns,即在數據建立后,最長不超過180 ns(t7)串口輸出數據。故當一組數據(D3-D0)傳送完時,可立即在時鐘下降沿有效,(降為低電平)鎖存數據;也可停止時鐘,隔一段時間使有效。

圖4所示是其工作在并行模式時的時序圖。該模式下,數據的建立時間和信號的鎖存時間均與串列模式相同。

2.2控制邏輯的編程

串列工作模式通常使用引腳、CLK、DATA IN、和。第一步,應在低電平有效的情況下,設為低電平,使其工作在串列模式;第二步,串列輸入32 bit的數據以完成一次輸入輸出配置的更改。每個輸出埠對應4 bit位(D3~DO,D3先輸入,如D3為低電平,則相應的輸出阻斷,緊跟的D2~D0則沒意義),共8個輸出埠,第8個輸出埠的數據最先輸入;第三步,在32 bit的數據全部輸入完畢時,停止CLK信號,變為低電平,並根據剛輸入的32 bit數據來切換矩陣的輸入輸出配置。如果在為低電平期間,CLK信號沒有停止。則切換矩陣數據動態更改;第四步,變為高電平,32 bit數據鎖存完畢。

需要注意的是:如果多個AD8108/AD8109器件級聯,則一次更改所需bit數是32與器件數的乘積。串列數據首先輸入第一個晶元的DATA

IN,然後依次進入其它晶元,直至最後的晶元。因此,給最後一個晶元的數據是程式控制序列的前端。

并行工作模式一次只允許更改一個輸出埠的配置。由於一次更改只花費一個CLK和周期,因而極大地提高了更改速度。并行工作模式需用到引腳、CLK、、D3-D0、A2~A0和。第一步,首先是在低電平有效的情況下,設置為高電平,使其工作在并行模式;第二步則設置為高電平,同時設置輸出地址A2~A0,和輸入地址D2~DO,以及輸出使能端D3,以使4位數據D3~D0裝入由A2~A0決定的32位移位寄存器中的某個4位單元段。第三步,端置低電平。32位移位寄存器中的數據被鎖存到并行寄存器中,再經8x4:8解碼后控制矩陣完成切換。

必須重點考慮的是:複位信號不能複位AD8108/AD8109中的所有寄存器,只是將切換矩陣的所有輸出通道設為禁止狀態,而寄存器中切換邏輯仍置於一個隨機的排列中。因此,不管是串列模式還是并行模式,初始上電后,都必須將所有的移位寄存器編程為期望的狀態。

3 AD8108/AD8109的應用及注意事項

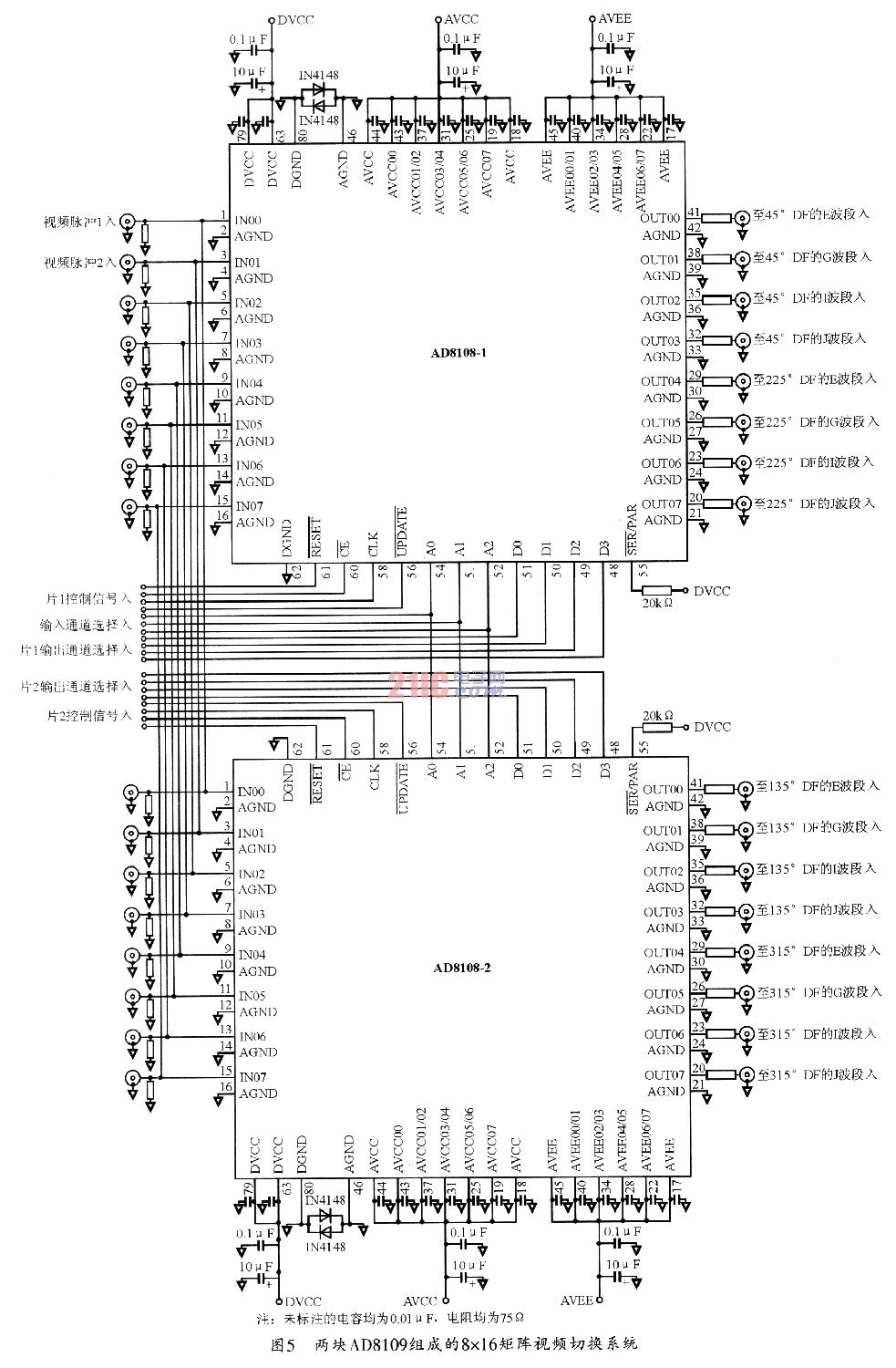

AD8108/AD8109是高密度集成模塊,利用其輸出使能、片選使能的不同特徵可構建超過8x8的大尺寸視頻切換開關。構建更大的矩陣開關

時,可將它們與AD8116配合使用。圖5所示是使用2片AD8108組成的8x16視頻切換系統,該系統可實現8路輸入中的任一路向16路輸出中的任一

路輸出,可滿足某型雷達告警設備比幅測向功能測試時需要將兩路視頻窄脈衝序列不同時切換到四個方向、四個頻段16通道的需求。

AD8108/AD8109主要用於視頻切換。由於視頻信號頻率較高,頻帶較寬,故在使用AD8108/AD8109時,應注意以下幾點:

(1)信號通道帶寬的考慮

信號通道帶寬是視頻切換系統的重要指標,它決定了視頻切換系統的技術難度、功能和成本。ADI公司的8×8矩陣切換晶元有AD8108/

AD8109,它們的-3 dB帶寬為325 MHz/250 MHz,雖然這些都遠遠高於電視視頻信號和計算機視頻信號的帶寬,但整個系統設計完成後的通道帶寬往往會降低。實驗表明,前級選用AD8108進行小信號切換,后級選用AD8109進行切換和放大,並注意阻抗的匹配,有利於提高矩陣切換器的通道帶寬,並加強系統的抗干擾能力。

(2)隔離度要求

隔離度是衡量系統抗交叉串擾能力的重要指標。雖然AD8108/AD8109在5 MHz時的隔離度為-83 dB/-75 dB,但隔離度與串擾信號的頻率有很大的關係,因此,設計完成整個系統后,其隔離度指標往往要降低很多。研究表明,人眼視覺可覺察到3%的亮度差異,相當於-30 dB的隔離度。而-45 dB的隔離度相當於0.56%的噪音(或串擾),遠低於3%,由於有足夠的余量,因而人眼感覺不到串擾光點。因此,設計完成整個系統后,其隔離度應不低於-45 dB才能滿足要求。

(3)大型切換矩陣構建

AD8108和AD8109最大的不同是增益不同。AD8108的增益為+1,而AD8109的增益為+2。故在構建大型切換矩陣時,為了減少切換時的串擾、提高信號通道帶寬,同時考慮到AD8109較強的驅動能力,一般將AD8108用在前級,而將AD8109用在後級。

(4)印製板設計

AD8108/AD8109是高密度集成模塊,其輸出使能、片選使能的不同特徵使得它們在構建大型切換矩陣中發揮了重要作用。為了最小化系統電路板產生的串擾,設計時必須仔細處理接地、屏蔽、信號通路和供電旁路等,具體應注意的:一是各路視頻信號間應用較粗的地線隔開;二是模擬地和數字地應當嚴格分開,只在電源處相連;三是模擬電源和數字電源獨立,電源的走線應盡量與數據傳遞的方向一致;四是採用多點接地屏蔽,且接地線應盡量粗,並在關鍵部位配置去耦電容;五是在用多片AD8108/AD8109組成大容量系統時,其控制線及片選線須加驅動電路。

(5)軟體編程式控制制

軟體控制切換時,應先使所有的輸出處于禁止狀態,然後,使相應的輸出處於允許狀態,再接通對應的輸入。考慮到AD8108/AD8109通常工作於并行模式時,複位信號只能將切換矩陣的所有輸出通道設為禁止狀態。而不能複位AD8108/AD8109中所有寄存器,寄存器中切換邏輯仍置於一個隨機的排列中。因此,初始上電后,和不允許都置低,以防止矩陣開關處於一個未知狀態。

4 結束語

通過本文的分析和設計,利用2片AD8108組成的8x16矩陣切換系統,目前已成功運用於某型雷達告警設備比幅測向功能的測試中,並成功實現了在兩路視頻窄脈衝序列不同時切換到四個方向、四個頻段16通道的切換功能。實踐表明,該切換系統可靠性高,抗干擾能力強。

[admin via 研發互助社區 ] 寬頻視頻切換集成電路AD8108,AD8109中資料已經有2188次圍觀

http://cocdig.com/docs/show-post-37974.html