1、引言

串擾可以定義為來自鄰近信號對某個信號通路的干擾。其耦合通路是以互容和互感為特徵的。在高速PCB線路中串擾會改變系統匯流排的傳輸性能,串擾會將雜訊感應耦合到其他的傳輸線上,會降低信號的完整性,導致雜訊容限變小,過大的串擾會引電路的誤觸發,導致系統無法正常工作。隨著信號頻率變高,信號上升、下降時間減小,PCB尺寸變小,布線密度加大等,都使串擾越來越成為一個值得注意的問題。

2、串擾產生原理

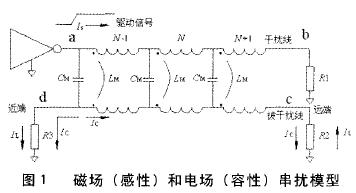

高速PCB線路之間的串擾既可以是由互電感產生的磁場耦合引起的,也可以是由互電容產生的電場耦合引起的。圖1是兩種耦合傳輸線串擾的模型,這裡定義兩個概念:近端串擾和遠端串擾,近端串擾是指在被干擾線上靠近干擾線驅動器的串擾,遠端串擾是指被干擾線上靠近干擾線接收端的串擾。

感性耦合是由於干擾源上的電流變化產生的磁場在被干擾對象上引起感應電壓從而導致的干擾。圖1中線路ab上傳輸信號的磁場在線路cd上感應出電壓,可以把干擾線看作變壓器的一次側,把被干擾線看作變壓器的二次側,被干擾線產生的電流在近端負載電阻和遠端負載電阻中流動。由互感耦合引起的各點波形如圖2(a)所示,圖2中Tp為傳輸線的延遲時間,Tr為驅動信號的上升時間。由圖2(a)可知遠端耦合產生一個負脈衝,其脈衝寬度為Tr,近端耦合存2TP時間展開,其幅度不變,但它們耦合串擾的總面積相等。串擾耦合總面積大小與LM(dIs/dt)、耦合長度成正比。

容性耦合是由於干擾源上的電壓變化在被干擾對象上引起感應電流從而導致的干擾。由互容耦合引起的各點波形如圖2(b)所示,與互感耦合不同的地方是遠端耦合為正脈衝。其耦合串擾面積大小與CM[(dv/dt)、耦合長度成正比。

感性與容性共同耦合的串擾,實質是兩種耦合串擾疊加的結果。由圖2可知,電感耦合和電容耦合串擾都試圖在近端d加強它們的效果(它們在d點的極性相同),而在遠端c試圖抵消彼此的效果(它們在c點的極性相反)。近端串擾脈衝的幅度大小是常數,而脈衝寬度由耦合區域表示的傳播時間Tp的2倍。遠端脈衝的寬度大約為干擾線上脈衝的上升時間Tr,幅度大小隨著耦合長度的增大而加大。正常條件下,在一個完整平面上,感性和容性的串擾電壓大小基本相等,在PCB線路中帶狀線電路具有很好的感性和容性耦合平衡性,其遠端串擾小;對於微帶線路,與串擾相關的電場大部分穿過空氣,而不是其他的絕緣材料,因此容性串擾比感性串小,導致其遠端耦合是一個負數。如果串擾是主要面對的問題,那麼就把所有的敏感走線都布置成帶狀線。

由傳輸線理論可知,若PCB走線有恆定的特徵阻抗Z0,如果它的終端阻抗匹配,就不會在這終端造成反射,但是終端阻抗不匹配就會造成反射。電壓反射係數為

其中RL是終端負載電阻。由式1可知,若RL=Z0,ρ=0,若終端開路(RL= ∞),ρ=1,若終端短路(RL=0),ρ=-1。在圖1中若近端終端電阻不匹配,會使近端串擾在遠端造成反射。為了消除近端串擾反射到遠端,可以通過在近端接入正確的終端匹配電阻,使ρ=0,消除反射。

3、串擾模擬

為了理解和研究串擾,尋找減小串擾的方法,使用Mentor Graphics公司的HyperLynx的LineSim模擬工具對串擾進行模擬。

3.1 微帶線模型

微帶線模型參數設置如下:走線寬度為6 mil,間距為4 mil ,走線距下方參考平面的高度是10 mil,相對介電係數為4.3,驅動器為“CMOS 3.3V FAST”,微帶線的長度為55in。完成設置后,HyperLynx計算出微帶線的特徵阻抗Z0為81.7ohms,傳輸延遲Tp為8.079ns。建立的模擬模型如圖3所示,模擬結果如圖4所示。

模擬結果分析如下:圖4中A0是驅動信號波形,這個波形從0V上升到3.3V用了1ns時間。B0是干擾線遠端也就是8.079ns延遲之後的波形。A1是被干擾線近端10Mohms終端電阻的波形,並在此處反射,它的寬度大約為16nS,也即是傳輸延遲Tp的2倍。

B1是遠端串擾波形,其中負脈衝部分是互容互感串擾疊加的結果,負脈衝之後的部分是近端反射到遠端的結果,其大小為A1點串擾的一半,這是由於81.7ohms傳輸線與81.7ohms遠端匹配電阻構成分壓器所起怍用的結果。

3.2 用終端匹配微帶線

參數設置與微帶線模型相同,只是被干擾線近端終端匹配電阻由原來的10M ohms改為81.7ohms,建立的模擬模型如圖5所示。由於傳輸線電阻與終端電阻匹配,從前面的分析可知近端串擾不會在遠端造成反射,模擬波形如圖6所示,從圖6中可以看B1點負脈衝之後沒有了近端的反射串擾,大大改善了遠端的總串擾。

3.3 帶狀線模型

使有帶狀線模擬,這裡使用的走線尺寸與微帶線模型相同,建立的模擬模型如圖7所示。由於走線處於帶狀線中,所以走線的一些性質發生了變化,特徵阻抗Z0變為64 ohms,傳輸延遲Tp變為9.663ns。從模擬結果圖8中可以看出B1沒有負脈衝,只剩下近端的反射串擾,也就是說在帶狀線環境中,串擾的容性成分與感性的成分一樣大而方向相反,它們相互抵消。

3.4 改變耦合長度、走線到參考平面層高度

改變耦合長度,模擬模型採用圖3中的模型,圖9中a、b、c曲線分別為傳輸線長度為27.5in、55in、110in的遠端串擾,從圖9中看出隨著耦合長度的增加,負脈衝的幅度也不斷增加,但是脈衝寬度不變,等於信號的上升時間Tr。近端串擾脈衝的幅度不變,但是脈衝寬度隨著耦合區域的長度增大而增大。在圖3所示的模擬模型中改變走線到參考平面層高度為5mil,圖10中a1、b1為原來間距到參考平面層高度為10mil的串擾,A1、B1為改變高度后的串擾,從圖10可知減少間距到參考平面層的高度,可以減少串擾。

4、結束語

串擾在高速PCB線路設計中是一個不可忽視的問題,正越來越來受到關注。通過對串擾產生原理及特點的分析,可知採取走線布置在帶狀線環境中,利用近端阻抗匹配,縮短傳輸線的耦合長度,減少走線到參考平面層的高度等方法可以減小串擾。此外還有學者提出走防護線減小串擾的方法,但這種方法在高速PCB設計中還存在較大的爭議。

[admin via 研發互助社區 ] 高速PCB線路串擾初探已經有4924次圍觀

http://cocdig.com/docs/show-post-44270.html