對於電路板的高頻阻抗控制,對於許多客戶而言應不陌生,但就特性阻抗是如何設計而來?或者特性阻抗在線路設計時有何限制?甚至高頻特性阻抗傳輸線又應設計多長才能達到最好的傳輸匹配環境?等多方面的問題尚不甚明了。

今就電子學的領域出發解譯影響高頻特性阻抗品質?諧振(resonance)?。

所謂的諧振意指可發生於任一物理系統中,只要該系統具有相對形式之貯能零件。當貯存於這些零件中之能量作相互交換時,就不需再自能源取得額外之能量,而將有諧振存在。

我們都知道當駕駛一前輪不平衡之車輛時,在某些特定速率下,不平衡的輪子之振動率等於前端懸吊者之自然諧振頻率,則存在在一系統中之彈簧及質量中之能量可彼此互作交換導致一大的振動及方向盤之移動,這些情形司機常見到之。

在此文中,我們將討論在電路中之諧振特性及一些應用。電路中之諧振,要求電抗量必須能互相抵銷。在一串聯RLC電路中,此需電抗性電壓降抵消:在一併聯RLC電路中,則需電抗性電流互相抵消。

一串聯電路的阻抗,為電阻值及電抗值之向量和。在一串聯RLC電路中,將有一頻率,在該頻率下可使其電感抗及電容抗相等,此頻率稱為諧振頻率。可使電抗值互相抵銷,導致凈電抗值為0,在諧振頻率(f0),|XL|=|XC|。

其中所言的RLC電路即指電阻、電感、電容組件所組合而成的電子迴路,所以了解何為特性阻抗之前,甚至何謂諧振頻率應先就其材料特性加以了解。

就電阻而言:電阻器(resistor)在高頻電路中應用甚廣,但是一般對電阻特性的了解,仍多局限於電阻在直流電路中所呈現的阻尼特性。實際上,電阻在高頻電路中,因受信號頻率的影響,不僅電阻值會隨之改變,更可能會呈現電感或電容的特性。

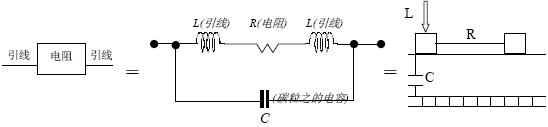

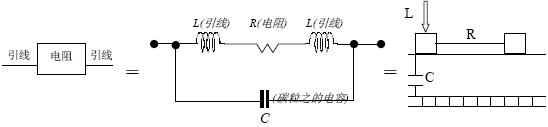

如圖所示電阻器在高頻時的等效電路,R為電阻器的電阻值,L為其兩端引線的電感,C為存在於電阻器內所有雜散電容的總和。雜散電容形成的原因,隨電阻器結構的不同而異。以碳粒合成電阻(carbon composite resistor)為例,由於其結構為以微小碳粒壓合而成,故在各碳粒之間都存有電容。此即為等效電路中雜散電容C的來源之一。由此可以推知碳粒合成電阻的高頻特性甚差。

另外就TDR測量空板上的傳輸線而言亦可依上述的方式解譯,其中上述所提L的效應來自電阻的兩端引線,同理推驗可知,TDR所使用探棒的測頭如接於導通孔時即產生傳輸路徑,此輸入通道愈長則L效應相對愈大,此現象將如同業先前所提的測阻抗泥效應,亦指目前TDR在測試時所看到前端振蕩效應。該效應對於愈短距離的傳輸線而言,將會造成觀察的困難。

就電容器而言:電容器對基本結構,是以兩片金屬平板中間隔以絕緣介質而成的組件,該組件在電路設計大都用作高頻旁路或交連電容如與電感器結合,則可設計為濾波電路或為調諧電路,但一般對高頻電路設計者來說其設計使用的電容器,往往不一定是選擇最適合的,常以取得方便為主做為考慮,所以往往高頻訊號傳輸過程將因電容器所造成的諧振點不同而使阻抗值偏差,所以電容器在設計時即應慎重考慮其品質。

另就空板電路板的結構,且以目前多層板的結構而言,往往層與層之間的結構形同為電容器的結構如圖。

就電容器而言有一品質因子Q,其公式為Q = 1/DF (Dissipation factor散逸因子)。當DF值愈小時即Q值愈大,所以就真正的電容器或電路板的層與層之間的結構而言,訊號傳輸過程的能量損失愈小則品質愈佳。

所以就板材材料而言,在單體材料時即應做電容值測試甚至於材料后加工后,亦應做電容值測試,因在壓合后每平方單位面積上的流膠分佈將因溫度、壓力而異於原始材料結構,因為材料於加工后其特性會有所差異,再者就電路板廠製程的一銅製程而言,在做電化學銅時因電鍍的效應關係,所以往往在該銅層之中會有縫隙,而該縫隙或漏洞將同前敘所言,電阻組件中碳粒之間都存有電容,意指銅層中的漏洞將產生額外的雜散電容,如此將導致以後諧振頻率中所需的|XC|不易控制,最後終將導致特性阻抗的無法精確控制,因此一銅的製程將不隻影響到二銅的結果而已。所以在預估階段的特性阻抗時往往無法有效掌控壓合后真正的介電常數值。

就電感器而言,電感器(inductor)多以導線繞制而成,導線在繞成線圈后,其所呈現的電感量,都比同樣長度的導線為大。使得線圈電感量增加的原因,在於線圈每匝所產生的磁通量,都能通過相鄰各匝,進而形成較強的磁場所致。因此,任何能加強磁場的方法,都能使電感量增加。電感量的大小,與線圈的形狀有關。

電感器在高頻電路中,是為常用組件之一,諸如諧振、濾波、相移以及延時等電路,都必須應用電感器。

如上述所言,今為就電路設計者而言應考慮在設計高頻訊號傳輸環境時此參數即因甚重考慮。因如前之所述,在諧振率(f0)時|XL|=|XC|此時的匹配阻抗將達最完美狀態,但就一條高頻的傳輸線而言本身的自感量尚不及1nH,所含的電感量不多,此將如何增加磁通量將是一大困難。傳輸線上並無增加磁通量的裝置,因此如要解決下列問題應如何進行呢?簡單,只要在主要改傳輸線的二旁加入并行的傳輸線並控制彼此之間的間距即可,因為諸如此類對設計此方法可有效加強電感量於電路中,如RAMBUS線路如下圖。

計算公式為:L=

r =線圈的半徑cm N =線圈匝數

L =線圈的長度cm

當一電感量增加時再控制所需的|XL|的量,即可與|XC|平衡達到諧振頻率。如此,對諧振的問題將可有效控制,進而達到高品質的高頻傳輸線路。你可試著思考如果RAMBUS傳輸線二旁的地線或一些在試片上曾加入的模擬線於二邊的傳輸線,今如去掉模擬線就最後的特性阻抗將又如何?

今將就R.L.C在高頻時所衍生出來的串聯諧振特性說明如下,但在此之前就高頻電路板設計者首先要先決定多少的匹配阻抗值適用於高頻主動組件與被動組件之間的傳輸線阻抗。其必備已知的條件如下

1. 主動組件的輸出阻抗值(Output Impedance)

2. 被動組件的輸入阻抗值(Input Impedance)

說明:已知主動組件的輸出阻抗值為50Ω,及希望與已知被動組件的輸入阻

抗值為68Ω,如此即可得出傳輸線的阻抗匹配值將為58.31Ω,公式為:

如1-1公式算出匹配的傳輸線阻抗將為58.3Ω,若轉換成頻率對阻抗的曲線圖則如下所示:

由上述所言可知在諧振頻率時(f0)其阻抗剛巧等於電路之總電阻值,因此時可使電感抗與電容抗相等,並使電抗值抵銷此時的頻率即為諧振頻率。

在較f0為低之頻率時,電容抗大於電感抗。故電路之總阻抗是電阻值與凈電抗值之相量和。明顯地,工作頻率較諧振頻率愈低,則凈電抗值愈大,總阻抗值亦愈大。且阻抗的落後之相位角亦愈大,簡言之,對低於諧振頻率之頻率的串聯RLC的電路將呈電容性。

在較f0為高之頻率時,電感抗大於電容抗,阻抗為電阻值及凈電感抗之相量和。頻率較諧振頻率愈高時,電路變為更具電感性。阻抗之導前的相位角亦愈大,總阻抗值亦愈大。我們綜合上述諸效應如下:

f< f0 : ZT=R-j (XC-XL)

=tan-1 XC-XL

R

f< f0 : ZT=R 0

f> f0 : ZT=R+j (XL-XC)

=tan-1 XL-XC

R

因此如上說明后可得知,傳輸線的特性阻抗值將來自諧振頻率點(f0)的位置而定,而該位置則影響來自容抗及感抗的含量而定。

電路設計者另要對高頻傳輸線在高頻訊號傳輸時的傳輸介質做選擇,因就傳輸線的等效電路圖而言將如下所示:

由前述得知當電容的容抗及電感的感抗不相等時,即會使傳輸線的阻抗特色呈現電容或電感效應,其中電容效應尤為劇烈,因此如能調整電容參數即能控制介質常數的穩定,將進而可調整諧振點(f0)及得到最後傳輸線上的匹配阻抗值,因此就材料內的電容參數阻計算公式如下

C=εr×8.85×10-12 F/m

條件εr=4.3則

C=4.3×8.85×10-12 F/m=38PF

其中上述公式8.85×10-12 F/m為自然界的空氣介質常數,F則為電容的容量單位法拉。

電路設計者對於未來傳輸線上的傳輸線長度亦要做考慮,因不同的傳輸頻率及不同的傳輸介質,將影響傳輸線的長度,舉例說明

設計一串聯諧振的迴路線路在50Ω的同軸電纜線,其介質為PTFE材料,其傳輸頻率為402MHz

條件Z0=50Ω,εr=2.10( PTFE介質常數)

公式λg=

=0.5149m=20.27in

λg/4 =0.5149m/4=0.1287m=5.07in

其中公式中λg為導體內的波長長度,f-c為光速空氣介質的傳播值,因此就該傳輸頻率其最短的傳輸線長度應為5.07inch。