CRC碼是線性分組碼的一個重要子集,它是為了保證通信系統中的數據傳輸可靠性而採取的通道編碼技術。CRC碼除了具有分組碼的線性外,還具有循環性,其碼字結構一般用符號(n,k)表示,其中,n是該碼組中的碼元數,k是信息碼位數,r=n-k是監督碼元位數。循環碼具有許多特殊的代數性質,這些性質有助於按照要求的糾錯能力系統地構造這類碼,並能相應地簡化解碼演算法。目前應用的CRC編碼器主要由硬體電路實現,可以保證編碼的快速性和實時性,但其缺點是系統複雜,可維護性差。本文介紹了一種以EDA設計工具MAX+PLUSII軟體為基礎,利用VHDL語言設計一個CRC(7,3)編碼器的方法,採用此方法實現的編碼器具有編碼速度快,可靠性高以及易於大規模集成等優點。

1 編碼原理

在CRC(7,3)編碼過程中,要將任意的三位信息碼轉換為CRC碼,實施編碼時的主要決定因素有兩個:信息碼多項式m(x)和生成多項式g(x)。

信息碼多項式就是以待轉換信息碼字為係數所構成的多項式,一旦信息碼確定,則該多項式就是唯一的。信息碼多項式只是編碼器處理的對象,在整個編碼過程中起決定作用的是生成多項式。

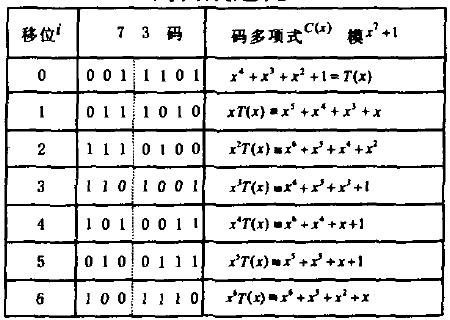

以CRC(7,3)碼構成來說明生成多項式在編碼中的作用,如表一所示。

表一 CRC(7,3)碼構成過程

由表一所示的構成2k-1=7個非全0碼字多項式的過程與結果看,編碼時從x4+x3+x2+x=T(x)開始進行逐一循環,並以模x7+1進行運算,該碼字正是信碼組中最低位為1,對應碼字多項式T(x),在全部非全0碼字中,它的最高位階次也最低,並等於n-k=4,即最高次項為x4。隨後一系列碼字都源於它的移i位(i=1,2,1,6)而形成,因此稱其為生成多項式g(x),即生成多項式是(x7+1)的一個最高階次為 (n-k)即4的因子,再將x7+1分解如下:

x7+1=(x+1)(x3+x+1)(x3+x2+1)

從該分解式中可以看到其中可以組合為二因式中包含最高次為4次的情況有兩種,即

g1(x)=(x+1)(x3+x+1)=x4+x3+x2+x

g2(x)=(x+1)(x3+x2+1)=x4+x2+x+1

這兩個式子都可以作為生成多項式,所不同的是選用不同的生成多項式所生成的CRC碼組不同。

當信息碼多項式m(x)(次數小於k)和生成多項式g(x)確定以後,用xn-k乘m(x),得到xn-k(x)的次數必然小於n。用g(x)除xn-km(x),得到余式r(x),r(x)的次數必小於g(x)的次數,即小於(n-k)。將此余式加與xn-km(x)之後作為監督位。得到的多項式就是CRC碼多項式,通過CRC碼多項式的係數即可得到所編的CRC碼字。

2 編碼器設計

2.1編碼框圖

CRC編碼器的主體是由移位寄存器和模2除法器構成的除法電路,通過邏輯開關的控制實施信息碼的輸入和CRC碼的輸出,編碼電路框圖如圖一所示。

2.2 VHDL實現

本次設計的CRC編碼器,利用MAXPLUS II軟體平台,據CRC編碼原理,採用VHDL文本輸入法。為了提高編碼的速度,在設計時採用信息位并行輸入,CRC碼并行輸出的演算法。程序經編輯調試通過後所生成的編碼模塊如圖二所示。具體程序代碼如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity yancrc4 is

port(sdata : in STD_LOGIC_VECTOR(2 DOWNTO 0);

datacrco :out STD_LOGIC_VECTOR(6 DOWNT 0);

hsend :out std_logic;

clk,datald:IN_STD_LOGIC

);

END yancrc4;

ARCHITECTURE rtl OF yancrc4 IS

constant multi_coef : STD_LOGIC_VECTOR(4 DOWNTO 0) :="10111";

SIGNAL cnt,rcnt,ttemp :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL dtemp :STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL sdatam,rdtemp:STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL rdatarcr:STD_LOGIC_VECTOR(6 DOWNTO 0);

SIGNAL st,rt:STD_LOGIC;

BEGIN

process(clk)

variable crcvar :STD_LOGIC_VECTOR(4 DOWNTO 0)

begin

if clk'event and clk='1''then

if st='0' and datald='0' then

-crcvar:=crcvar(3 downto 0)&'0';

dtemp<=sdata&'0'&'0'&'0'&'0';

sdatam<=sdata;

-crcvar:=sdata

cnt<= (others=>'0');

hsend<= '0';

st<='1';

elsif st='1'and cnt<3 then

cnt<= cnt+1;

if dtemp(6)='1'then

crcvar:=dtemp(6 downto 2)xor multi_coef;

dtemp<=crcvar(3 downto 0)& dtemp(1 downto 0)&'0';

else

dtemp<=dtemp(5 downto 0)&'0';

end if;

elsif st='1' and cnt=3 then

hsend<='1';

elsif st='1' and cnt=4 then

hsend<='0';

st<='0';

end if;

end if;

end process;

end rtl;

2.3模擬結果

系統設計完成後模擬結果如圖三所示。

3 結束語

本次設計的CRC編碼器經下載測試,具有編碼速度快、編碼準確率高等特點,達到了預期的設計要求。所生成的CRC編碼模塊可以以存檔模塊的方式存儲在模塊庫中,這為後續開發CRC編解碼系統奠定了良好的基礎,同時也可以使該模塊成為其他設計人員可共享的設計資源。

[admin via 研發互助社區 ] VHDL的CRC編碼器的設計已經有3748次圍觀

http://cocdig.com/docs/show-post-43142.html