狀態機是一種十分重要的時序電路,常用於描述數字系統的控制單元,在數字系統有著廣泛的應用,如步進電機、數據存儲器的讀寫、匯流排控制器等。本文結合具體課題;採用ALTERA的CPLD器件EPM7032實現了一種容錯的狀態機;採用VHDL語言編程,實際使用效果良好,不僅調試方便,而且增加了系統配置的靈活性,大大縮短了系統開發周期。

1 狀態機的真值表及狀態轉移

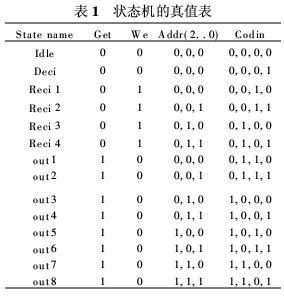

該狀態機是一種Moore型的,其真值表如表1。

該狀態機編碼方式採用順序方式,共採用4位編碼。這樣就存在兩個非法的狀態(即在狀態機中,未定義的狀態);採用該編碼方式與一位有效編碼方式相比,大大減少了非法狀態的存在。

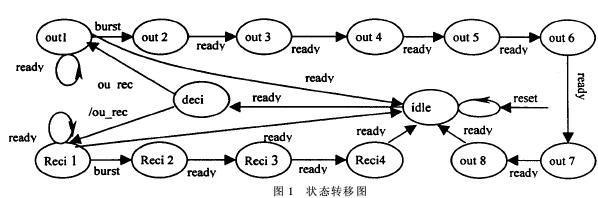

狀態轉移圖如圖1所示。

2 VHDL的描述

採用VHDL語言描述時、主要應包括:狀態變數、時鐘、狀態轉移指定、輸出指定、複位信號等幾個方面。

(1)狀態機的狀態變數定義如下:

TYPE StateTYPE is (idle, deci, reci1, reci2, reci3,reci4 ,out1,out2,out3,out4,out5,out6,out7,out8);

signal present_state,next_state:statetype;

signal codin:std_logic_vector(3 downto 0);

(2)狀態機的部分狀態轉移指定:

statedesc: process (reset, data, present_state, burst,ou_rec,ready)

begin

.........................

Case present_state is

When idle=>codin<="0000";

If(data="11111111")then next_state<=deci;

Else

Next_state<=idle;

end if;

..............

When out1=>codin<="0110";

If(ready=' 0' )then

Next_state<=out1;

Elsif (burst=' 0' )then next_state<=idle;

Else next_state<=out2;

end if;

...............

(3)狀態機的輸出指定

狀態機的輸出需要對codin進行解碼才能輸出,輸出指定放在另一個進程(在該進程中同時還實現次態到現態的轉化)中, VHDL的描述為:

state-change:process(clk)

begin

case codin is

when "0000"=> get<=' 0' ;we<=' 0' ;addr<="000";

...............................................

when"1101"=>get<=' 1' ;we<=' 0' ;addr< ="111";

when others= >get< = ' 0' ;we< = ' 0' ;addr< ="000";

end case;

end process state-change;

3 糾錯功能的實現

在實際的工作當中,由於硬體電路中,干擾、鐘擺、雜訊、電源的變化等都可能使觸發器翻轉,從而使狀態機誤入非法狀態。一旦出現這種情況將無法預見系統的反應,可能會出現狀態鎖死、系統非法輸出;信號衝突,過大的拉電流和灌電流,毀壞系統。

在進行容錯設計時,首先在枚舉類型的狀態定義中定義所有的非法狀態。因此狀態定義改為:

TYPE StateTYPE is (idle, deci, reci1, reci2, reci3,reci4, out1,out2,out3, out4,out5,out6,out7,out8,undefine1,undefine2);

最後,需要定義轉移出非法狀態的代碼。程序片段如下:

..................

case present_state is

.................

when others =>next_state <=idle,err<=' 1' ;

end case;

另外在進程的設計時,還需要充分注意信號的同步問題,這樣才能避免競爭冒險的問題。進行容錯設計,雖然犧牲了資源,但卻可獲得了高可靠的系統。

4 結束語

實踐證明使用可編程邏輯器件可以非常方便地實現狀態機。而採用VHDL語言設計,不僅描述方便,而且具有良好的可移植性,可以非常方便地應用於其它公司的CPLD,FPGA晶元中。實際使用中該晶元運行良好,同時可以隨時對晶元內部邏輯進行在線更改,體現了可編程邏輯器件的優越性。

[admin via 研發互助社區 ] 基於CPLD的一種容錯狀態機的設計已經有2553次圍觀

http://cocdig.com/docs/show-post-43078.html