1 概述

隨著電力系統進一步朝著“大電網、大容量、大機組”的方向發展,發、輸、配電過程要求高度自動化已成為不可逆轉的趨勢。因此,對其對應的“發、輸、配”環節的自動裝置、繼電保護裝置、故障檢測及診斷裝置等性能提出了更新更高的要求。而數據採集卡系統作為這些裝置的前向設備,其性能直接影響著這些裝置的整體性能,同時,也在一定程度上影響著整個電力系統運行的“穩定性、安全性”。

在電力測控系統中,常常需要採集周期性交流模擬量信號,並對它們進行相應的處理。一般情況下,監控系統中用普通MCU(如196、296等單片機或控制型DSP)是可以完成系統任務的。本系統要求對6路交流信號進行採樣,進行32次諧波分析並且對電力參數進行計算。如果僅僅依靠一個MCU(單片機或控制型DSP)既作為主系統的CPU對整個系統執行調度又要對信號進行採集和處理,而且隨著監控系統功能的增加和信號量的增多,這樣利用有限的MCU資源往往就不能完成任務,更不要說達到實時監控與響應的要求了。所以採用模塊化設計的思想,將數據採集處理與主系統分開。由數據採集系統將數據採集並進行處理后,主系統只要通過匯流排就可以訪問數據採集卡得到自己所需要的數據。數據的採集與處理完全通過FPGA由硬體執行實現,FPGA硬體的速度是ns級的,這是當前任何MCU都難以達到的速度。因此本系統將比其它系統更能實時地、快速地監測信號量變化,大大加快了處理速度,提高了實時性,同時也減少了對主系統資源的佔用。

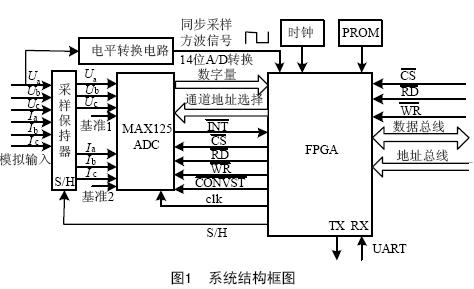

本系統中的外圍電路設計相對簡單、可靠。鑒於FPGA可編程實現的特點,系統具有較好的擴展性,在監控系統中也具有一定的通用性,而且通過通信口可有選擇的將信號參量值送往主控單元或直接送往鍵盤顯示單元。系統主要包括數據採集電路、ADC模塊、FPGA模塊,以及時鐘電源和PROM代碼下載電路等幾部分,其結構如圖1所示。

2 主要模塊介紹

2.1 數據採集電路以及ADC模塊

數據採集電路的採集對象為6路交流信號,交流信號經過PT或CT隔離,然後經移位放大後送入採樣保持器LF398。如圖1所示,本系統中,A/D轉換器採用MAX125,其單通道轉換時間為3μs,可同時對4路信號進行採樣保持再依次進行轉換,轉換時間為12μs,而且可以在2個4路通道間進行相互切換。由於系統需要同時採樣6路交流信號,所以在A/D轉換前加上採樣保持器,再通過MAX125分別對3路相電壓和3路相電流進行轉換。轉換完成後,由INT發出中斷通知FPGA讀取轉換結果,FPGA再將數據存放到各個信號所對應的區域中。總之,信號的採樣保持與A/D轉換的控制以及轉換后數據的讀取和存儲都由FPGA來完成。

2.2 FPGA模塊

本系統中的FPGA採用Xilinx公司Spartan-III系列的XC3S400-5PQ208。該系列具有低功耗、高性能的特點,內核採用3個獨立1.2V電源進行供電,系統最高時鐘可達326MHz;I/O埠供電從1.2-3.3V;內部帶有乘法器,有著豐富的分散式RAM和塊RAM;精確的時鐘管理模塊,以及性能優越、穩定成熟的IP核,有利於縮短開發周期。Xilinx公司的ISE軟體為FPGA的設計與實現提供了很好的開發平台,通過VHDL、原理圖和狀態機相互結合的設計方法使設計更趨於完善。

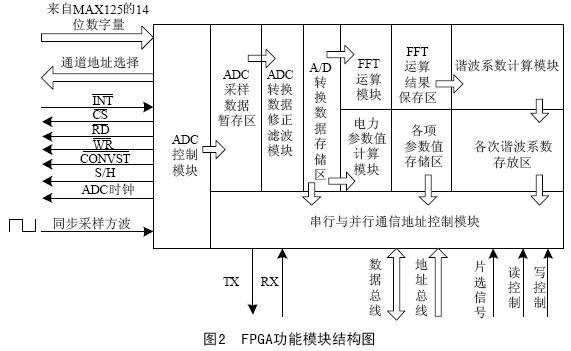

FPGA模塊是整個數據採集處理系統的核心,主要完成匯流排通信、數據採集控制、ADC數據的讀取和存儲、6路交流信號的諧波分析以及各項電力參數的計算。FPGA的內部工作結構如圖2所示。從功能上分有:控制模塊、運算模塊、存儲模塊和介面模塊。按照數據的傳遞方向有:ADC控制模塊、ADC轉換數據處理模塊、ADC轉換數據存儲區、FFT工作模塊、參數計算模塊、運算結果修正模塊、諧波係數及電力參數存儲單元以及串列和并行通信模塊。

(1)ADC控制模塊與數據處理模塊

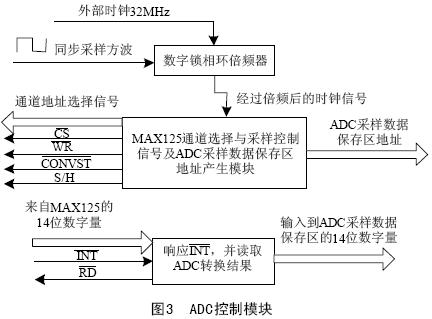

如圖3所示,ADC控制模塊除了完成對MAX125及採樣保持器LF398的控制外,還要響應MAX125的中斷(INT)來讀取轉換結果,並將其保存到ADC採樣數據保存區。如圖3所示,為了更準確地產生控制時序,對系統的採樣周期及相位的鎖定都採取了相應的處理。待採樣信號先經過方波轉換電路,將其轉換成0~+5V的方波信號,再經過FPGA中的數字倍頻模塊,將信號進行64倍頻后得到的時鐘信號作為採樣信號,以此來消除頻率漂移帶來的採樣周期誤差所造成的頻譜泄露現象。本系統採用的數字鎖相環在FPGA中實現,其具體的性能為:鎖相環的捕捉帶Δfmax=10Hz,鎖相頻率為50Hz±10Hz=40~60Hz。隨後產生的採樣周期Ts能夠滿足實際應用的要求,由同步方波信號所產生的倍頻信號是A/D轉換事件的一個觸發基準,在這一時鐘基準下,各個模塊按照所對應的時序執行相應的功能。同時,根據採樣保持信號和計數器,產生ADC採樣數據保存區地址,保存來自MAX125的14位數字量,分別將各個交流量存入相對應的存儲區域。

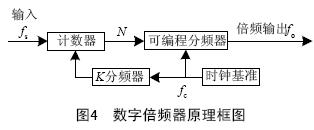

數字倍頻器的原理框圖如圖4所示,交流信號經整形后,轉換為與輸入信號同頻率的方波,其頻率為fs,要求對其進行K倍頻。設置一標準的時鐘信號,時鐘頻率為fc,採用可編程分頻器對時鐘信號進行分頻,其分頻係數由計數器提供,若分頻係數為N,則輸出頻率為fc的N分頻,即:

fo=fc/N (1)

時鐘信號經K分頻後送至計數器,計數器在輸入信號的一個周期內對fc/K脈衝計數,若忽略各種誤差因數其計數值為N,則:

N=(1/fs)×(fc/K) (2)

將(2)代入(1)式有fo=K×fs,實現了對輸入信號頻率的K倍頻。數字倍頻器中,計數器的實質是利用脈衝對輸入信號的周期驚醒填脈衝計數,實現周期測量。由於該模塊在工作過程中連續測量輸入信號的周期,所以它又是一個頻率計,兼有測頻與測周期的功能。

經過A/D轉換的數據暫時存放在一個區域內,通過ADC轉換數據處理模塊,同時利用對基準或0V電壓的轉換數據,對信號的A/D轉換值進行修正。修正過後,再對其進行64點的FIR濾波,這裡的FIR採用Spartan3系列自帶的IP核,從而得到了經過修正後的信號A/D轉換值,為後面的運算作好準備。

(2)諧波分析模塊

在交流信號採集處理系統中,採用快速傅立葉變換(FFT)進行諧波分析。該模塊採用的是S3系列中自帶的IP核進行設計而成的,它主要由介面和IP核兩大部分組成,介面主要負責將相應存儲區域內的A/D轉換數據送至IP核模塊執行FFT,然後再將變換后得到的結果送到各自的存儲區域內。

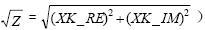

根據FFT運算的結果Z=XK_RE+j(XK_IM),計算各次諧波的係數

(3)電力參數值計算模塊

交流信號採集處理系統可以測量與交流信號有關的16個參量,它們分別是:頻率、功率因數、相電壓、相電流、有功功率以及無功功率等。

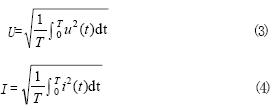

◆電壓、電流有效值的測量

電壓u(t)和電流i(t)為周期性函數。它們的有效值U和I可表示為:

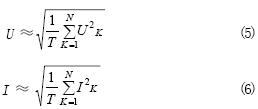

若在電網一周T內,等間隔採樣N點(N=64、128、256等),則它們的有效值可由下式做近似計算:

式中Uk、Ik分別為第K點的電壓、電流採樣值。

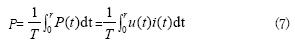

◆有功功率和無功功率的測量

電網線路中某一相的有功功率可表示為:

由式(7)可知,有功功率是瞬間功率在電網一周T內的平均值,而瞬間功率是同一時刻電壓與電流瞬時值的乘積,對電壓和電流採用同步採樣的方法即可獲得同一時刻的瞬時值。對電壓、電流模擬量進行離散採樣后,有功功率可由下式近似計算得到,

式中Uk、Ik為同一時刻,第K點的電壓和電流的採樣值。

由分析可知,電網線路中某一相的無功功率可由下式近似計算得到,

式中I(k+N/4)是第(K+N/4)點電流採樣值,比電壓採樣值Uk滯后1/4的電網周期。即相位滯后π/2。

◆功率因數

由同步採樣得到的採樣序列{Uk}、{Ik},K=1,2,3,……,N,即可由(5)、(6)、(8)、(9)、(10)計算得到線路中某相電壓、電流有效值、有功功率、無功功率和功率因數等電力運行參數,進一步可獲得某條三相線路的參數。參數值計算單元主要由時序控制、存儲單元和計算單元等組成。其中,計算單元由加、減、乘、除四則運算模塊以及平方根模塊組成。這裡求平方根模塊的實現與上面的方法相同。

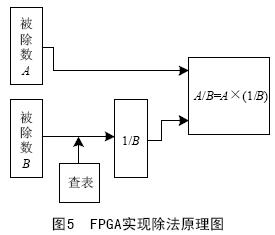

對於除法模塊,由於在FPGA中實現二進位除法演算法十分複雜,在實現除法時,採用了被除數與除數倒數相乘的方法。因此,在給定除數的同時必須計算出除數的倒數,由於除數的倒數是小數形式,所以將小數部分的16位與整數部分的1位組成一個17位二進位數,這樣可以和被除數進行二進位乘法運算,乘積的低16位為小數部分,其餘則為整數部分。在FPGA中,將除數作為寄存器地址,利用查表的方式查找其相應的倒數,這樣求倒數就相當於一次寄存器定址,其原理圖見圖5。通過除法運算得到的商精確到小數點后16位,達到了工程中對運算精度的要求。

(4)串、并行介面模塊

為了使數據採集卡能與匯流排或其它系統靈活的連接,FPGA提供了兩種通信方式:串列通信與并行通信。并行通信可以直接和系統機箱的背板匯流排相連接,可由主控系統的MCU對其進行訪問或命令控制。串列通信可以方便的和各種MCU連接進行數據交換,也可以與鍵盤和顯示單元組成單獨的電能質量監測系統。

3 總結

本數據採集處理卡能直接投入到現場使用,由於採用模塊化設計,所以也可以在原有的監控系統上工作,對遙測量進行採集和處理。它主要對多路的交流模擬信號進行採集並作諧波分析處理與電量的計算處理,FPGA作為協處理器,主要完成對交流信號的同步採樣控制功能與諧波分析FFT的運算以及電力參數的計算功能;並帶有通用的并行和串列介面。通過FPGA的設計使軟體硬化,採用FPGA提供的IP核進行設計,縮短了開發周期,提高了系統的穩定性;同時也大大提高了主系統的效率,減少了資源的佔用,節省了時間消耗。因為主控系統能與該系統并行運行,實時性將得到明顯的提高。該採集處理系統在電力監控系統中有較好的應用前景。

[admin via 研發互助社區 ] FPGA 的交流信號採集與處理系統已經有2460次圍觀

http://cocdig.com/docs/show-post-43064.html