FPGA的公司實際上換而言之,也可以成為EDA的公司了,只是他們在這方面的能力是否強大而已.這3家公司中,擁有自己HDL的公司只有Altera.可能很多人不太清楚,就是AHDL,當然這種語言的輝煌期已經過去了.這裡說這個,絕對不是鼓勵大家用這個語言.

這3家主要的開發軟體大家都知道,在中國應該以Quartus II用的最廣.ISE次之.但是現在這兩大軟體的外觀都已經有些一致的地方了.但是他們近乎同樣外觀的軟體,卻還是有很多地方非常不同.

Altera 在2000年前,在日本市場獨領風騷.大家知道日本是漫畫的國度,他們總是喜歡用圖形表達,這可以證明Altera的圖形輸入做的是爐火純青.但是,現在都是語言輸入為主導了,因此Altera的這個優勢才漸漸淡化.但是其他圖形界面仍舊有其鮮明的特色,簡單容易.

Altera的軟體像Canon的相機,很傻瓜,對著景物按個快門.當然也有些地方,你也可以仔細微調.

Xilinx的軟體洋洋洒洒,很專業,像部哈蘇相機,你在照相前,先成為相機的專家,才能成為設計的專家.有人開玩笑了,這是拿東西來說事.那在這裡引用Altera公司一些思想,給大家介紹一下.實際上,這個特點非常容易記憶.大家都知道TIPS這個單詞吧,就是提示的意思.那在這裡就給你一些提示,讓你可以過目不忘!

TIPS---提高設計效能的秘方!

這幾天準備一下,儘快讓大家看到下面的章節!

從TIPS中的T開始說,FPGA的趨勢如下

1--首先說一下眼前的大環境是怎麼影響你的設計的.過去的設計規模應該是比較小,一個FPGA工程師,寫個狀態機,寫個好的代碼,這個就是相對來說的高手了.但是你要知道這種高手都是關起門來自稱老大的.實際出門走多遠很難說.因為現在器件的發展速度是很快的.

2---規模的變化

1998---一位當時的PLD的廠商說 世界上有1000個宏單元的PLD就可以應付95%的設計了.今天你認為怎樣?

1998---最大的FPGA內含10000LEs,今天的CycloneIII的第二小的傢伙就是這個身段.

2008年---現今最大的FPGA內含530,000LEs,比1998年增大50倍!你還能用以前的設計方式來應付今天這個龐然大物嗎?

3---規模的變化,帶來複雜度的提高,調試也成為關鍵?

晶元規模大的時候,你就會要有些測試工程師的需求.因為人自己總是看不清自己的缺點.

4---一個模塊跑個固定的速度,是否可以和其他模塊都配合起來,還能保持性能?

目前EDA廠商眾口一辭的話: 20KLEs規模以上的設計,時序收斂是第一目標

當有問道Xilinx的軟體設計者時候 ,他們也承認了這樣的事實:

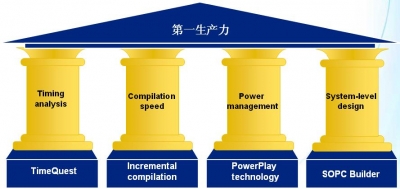

好了,第一個題目誕生了.T-IPS 中的T就是TimeQuest,以前FPGA的規模和設計ASIC不能相比,今天已經可以了.在FPGA中集成很多IP已經不是什麼難題了.TimeQuest是依照SDC來進行工作的,SDC,是ASIC中設置約束的工具,換言之,也算是你如何指揮你的軟體,將你設計的模塊讓他們統一協調好時間,然後保證最終的結構是你想要的.你不僅要看到設計,還要跑到那樣的速度的時候,他還是你要的功能 ,有人說了,以前沒有這樣的工具嗎? 有,但是那不是針對大的設計的.當然大也是相對的,到了一定的規模,就必須使用另外的標準了! 什麼能幫助你達到時序收斂,什麼可以加速你找到哪些地方不滿足,TimeQuest!

目前支持這個SDC的有以下工具,當然Quartus支持的最完整. 潛在的秘密是,Altera的器件的規模也是最大的了.

可能你會問,能不能詳細點說一下:

TIPS中的I是指"遞增編譯",就是英文"Incremantal compile"的第一個字母是I.

剛才說了,當你有時候改動了一部分設計的時候,你以前好不容易調好的時序,可能因為重新改動的影響,而在編譯路由后,將沒有改動的設計在布局和速度上發生了不期望的改變.那這個遞增編譯就是干這個的.他可以向制導武器一樣,讓你指哪裡,打哪裡.同時縮短編譯時間,提高你的工作效率!當然這裡絕非這麼一句話就可以涵蓋了.你也要有設計分離,規劃布局等工作.

現在經常有提到我的產品是最好的Price,但是,現在由於系統規模增大,Power也是一個很重要的制約,功耗在某些設計中甚至是第一位的.Quartus中有關於根據Power的要求來智能編譯設計的約束.就是TIPS中的P,也就是PowerPlay.

最後一個TIPS中的S就是指Systemlevel,或者是SOPC,因為你的設計可能要有各種介面,外部的,內部的,系統的互聯.匯流排的對接,時鐘域的交叉,這些,都可以用SOPC的工具SOPC builder來實現.不用內置處理器也可以.同時要求你在系統級的高度進行設計,這樣就提高設計速度.在第三篇中有詳細講.

生產力發展的標誌-生產工具,你現在和15年前設計方式的根本改變!

不管A,X,L,哪一家FPGA玩家,這三年來都在開發工具上投入了重兵.此前有網友爭論--

Lattice用的是Synplify進行的綜合,效果如何如何高.這個論調10年前是天經地義,顛覆不破的真理,但是今天再這樣說,絕對偏頗!

Synplicity公司不少人後來都轉投Altera門下.當時Sy最先得到Xilinx的結構的時候,大力發展所謂物理綜合等一系列亮點,但是卻對Altera提及甚少,大家都知道Sy的發家史,失去了FPGA廠商的支持,基本上也就失去溫床.在2004年QuartusII4以後,Quartus的綜合能力就已經與S家的不相伯仲了.Xilinx在10年前收購多家EDA廠商,例如StateCAD,當時用流程圖生成狀態機的VHDL和其他的一些廠商的時候,Quartus都是建立在自己的固有體系下.如果單獨從產品器件上,只有工藝和功耗是未來需要爭鬥的地方,那麼,綜合能力和相關路由(就是緊耦合的模塊放在一起)能力,以及EDA工具的全面性才是真正FPGA廠商的絕對命門.S家一共有250個軟體開發人員.A家可能就遠遠不止了.

另外Cadence,Synopsys,Magma,Mentor等大哥,也就是賣個綜合和核對工具,價值點相信大家已經悟到幾分吧.

QuartusII 在今天,作為FPGA攝影大師的工具來說,不僅是精密的哈蘇,更是Canon門下Eos MarkII的便捷傻瓜的代表.QuartusII就是今天FPGA的第一生產力

[admin via 研發互助社區 ] FPGA三國志-第四篇/工具篇已經有2628次圍觀

http://cocdig.com/docs/show-post-43030.html