前沿

在FPGA設計中,配置PROM(如18V00系列)/FLASH(XCF00系列)主要的功能是存儲FPGA設計,然後在上電之後,自動將設計裝載到FPGA當中。在有些時候,FPGA設計並未全部將配置PROM/FLASH的存儲單元全部佔用,因此,未被佔用的單元就被浪費掉了。

在某些應用中,用戶需要在片外(FPGA外)存儲自己定義的數據,這個時候就要單獨掛PROM/FLASH晶元到FPGA上,這樣不僅增加了設計難度(用戶需要專門編寫存儲控制介面)、增加成本、增加布板難度、增加FPGA管腳使用數量等,從而給設計者帶來很多不便。如果用戶自定義的數據量不是很大,而且正好可以放到PROM/FLASH的未被佔用的存儲單元中,那麼將極大減輕設計者的負擔,減少成本,增加系統可靠性。

下面將詳細介紹如何將用戶自定義數據存儲到PROM/FLASH中,以及如何讀取這些數據。

具體實現

原理

要想實現將用戶自定義數據寫入PROM/FLASH以及從它們當中讀出來,首先要明確以下幾個問題:

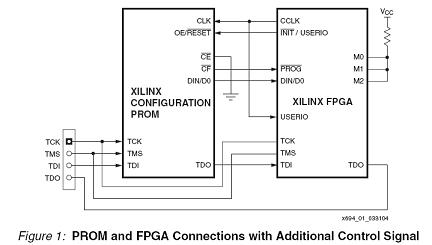

理解了以上兩個問題,我們就能從總體上知道是什麼原理使用戶數據能寫入到PROM/FLASH當中,並被讀出來。看FIG1:(註:以下所有的討論都是認為FPGA的配置模式是主-串模式)

在FIG1中,有幾個關鍵信號:CCLK,CE/,OE_RESET/,INIT/(INIT/在FPGA上)。在主-串模式配置過程中,上電之後,由FPGA的CCLK引腳發出時鐘,驅動PROM/FLASH的CLK,而PROM/FLASH根據CE/、OE_RESET/的狀態來確定是否地址增加(此“地址”是PROM/FLASH內部數據存儲單元的地址)。如果FPGA將所有的設計數據讀取完畢,則停止產生CCLK時鐘。而CE/、OE_RESET/的狀態可能在FPGA配置完畢之後變化,使地址複位。注意,當CCLK產生且PROM/FLASH有數據輸出時,要判斷這些數據是否是設計數據。判斷的方法是通過一個同步欄位來實現的。不同系列的FPGA同步欄位會有不同,比如Virtex系列FPGA同步欄位是AA995566h。在對應FPGA的配置手冊中會找到其同步欄位。

上述所述過程大概描述了一個FPGA的配置過程。因此,如果要想在FPGA配置成功之後,繼續讀取用戶自定義在PROM/FLASH中的數據,就要在上述過程中做一下變動,而且不影響正常的FPGA配置。

通過研究PROM/FLASH的手冊,可以知道,當CE/變高后,PROM/FLASH的地址計數器就會複位,而不再因為CLK有脈衝而地址增加。所以,當FPGA配置完畢后,設計者要阻值CE/變高。

在配置過程中,INIT/變低,表示FPGA接收的數據有CRC校驗錯誤,這時PROM/FLASH的地址計數器會清零。

當OE_RESET/為低,PROM/FLASH的地址計數器複位。

Tab1為OE_RESET/和CE/與PROM/FLASH地址的真值表:

通過前面分析幾個信號對PROM/FLASH地址的影響以及FPGA配置過程,可以有如下的方法來實現在成功配置FPGA之後,正確讀取PROM/FLASH中的用戶自定義數據:

以上兩個措施保證了在FPGA成功配置后,PROM/FLASH的地址不會清零。但是由於FPGA成功配置后,CCLK就停止產生,所以,儘管PROM/FLASH地址沒有被複位,但是也不會增加。還要想辦法使地址增加。

在上述條件滿足時,地址增加就要有時鐘輸入到PROM/FLASH的CLK引腳上。由於CCLK的不可控性(儘管BitGen中有一些選項可以影響CCLK的變化。我沒有仔細去研究過),因此需要有一個設計者可控的時鐘信號輸入到PROM/FLASH的CLK引腳上。當FPGA成功配置后,CCLK為3態且有一個弱的到VCCO的上拉,因此將一個USER IO連接到PROM/FLASH的CLK引腳上是可行的。也就是說FPGA的CCLK和一個USER IO同時都連接到PROM/FLASH的CLK引腳上。這樣,設計者就可以在FPGA成功配置后,通過控制USER IO來產生時鐘脈衝,來讀取自定義在PROM/FLASH中的數據。因為數據是串列的,而且PROM/FLASH的地址對設計者來說不可見,因此借鑒FPGA在配置時是如何確定從PROM/FLASH讀出的數據是設計數據的方法:識別同步頭。因此,在生成用戶自定義數據的時候,也要考慮一個有意義的同步頭數據。

如數據可以按照FIG2來分佈:

如何生成用戶數據並加入到mcs文件中,在後面有描述。

Read宏單元實現

從前面描述,清楚了在硬體上如何改動,使之適合在FPGA配置成功后,能讀取PROM/FLASH中的用戶自定義數據。但是,如何讀取、讀取這個動作如何實現,還是需要專門設計一個模塊才可以。

FIG3是一個標準的讀PROM/FLASH數據的宏單元框圖:

該宏單元實現了在FPGA成功配置后,從PROM/FLASH中讀取用戶自定義數據。各引腳信號說明,見Tab2:

| 信號名 | IO 方向 | 描述 |

| clock | 輸入 | 所有信號的寄存都是在clock的上升沿 |

| reset | 輸入 | 非同步低有效複位信號。該信號將所有邏輯複位到初始狀態。 |

| din/d0 | 輸入 | 連接到PROM/FLASH的數據輸出引腳。用戶數據出現在該引腳上。 |

| read | 輸入 | 該信號低有效。該信號指示該宏單元從PROM/FLASH中讀取下一個8bit數據。 |

| next_sync | 輸入 | 該信號低有效。該信號指示該宏單元搜索存儲在PROM/FLASH中的下一個同步欄位。 |

| dout[7:0] | 輸出 | 用戶自定義數據會出現在該匯流排上。該匯流排上是否是有效的用戶數據,由data_ready來指示。當data_ready保持一個時鐘周期的低電平時,表明該匯流排上的數據是有效的。 |

| data_ready | 輸出 | 該信號低有效。當該信號持續一個時鐘周期為低時,就表明dout[7:0]上的數據是有效的用戶自定義數據。 |

| sync | 輸出 | 該信號低有效。當從檢測到從PROM/FLASH中讀出的數據有同步欄位時,該信號變低。 |

| reset_prom | 輸出 | 該信號低有效。當該宏單元被複位時,該信號就會變低。該信號連接到PROM/FLASH的CE/或OE_RESET/上。當該信號為低時,使PROM/FLASH的地址計數器複位。 |

| cclk | 輸出 | 該信號非FPGA引腳上那個CCLK。該信號只是模擬CCLK。 |

下面詳細介紹該宏單元是如何被設計以及如何工作的。

如何將用戶定義數據加到PROM/FLASH

前面所述都是已經假定用戶數據已經裝到了PROM/FLASH當中,現在就講述具體怎樣實現數據的裝入。

首先存在一個名字為Perl的腳本文件,該腳本文件可以使用戶定義數據加到PROM文件中。格式是Intel Object和Hex格式。

Perl腳本文件可以在參考設計的/Perl_Script目錄中找到。

Perl腳本文件不支持Motorola EXORmacs和TEKTRONIX TEK兩種文件格式。

為了詳細解釋這個腳本文件做了什麼以及其如何工作,因此有必要詳細PROM文件的格式。將分3部分來詳細描述PROM文件的格式。

參考設計

在附件的壓縮文件里有參考設計。這裡簡單介紹一下參考設計。FIG9是參考設計的框圖:

從PROM/FLASH中讀到的數據在LCD上顯示。LCD的驅動有PicoBlaze實現。

其他實現方法

前面講的是在主-串模式下從PROM/FLASH中讀用戶數據。當然也可以採用SelectMap模式以并行方式從PROM/FLASH中讀取用戶數據。在設計方法與前述無太大區別,只是採用SelectMap方式后,數據為并行方式,少了串-並轉換以及bit計數。

在同步欄位問題上,如果用戶數據分為幾個不同部分,可以採用所有同步欄位都相同以及同步欄位不同的方式。兩者各有優缺點。如果同步欄位都相同,就不清楚當前所讀的數據是屬於哪一段;如果同步欄位不同,可以清楚當天所讀數據屬於哪個部分,但是存在同步欄位更新和存儲的問題。很好理解,不再贅述。

說明

本文檔全部內容完全來自於Xilinx XAPP694文檔。參考設計也完全來自Xilinx的XAPP694.zip。由於時間和個人能力原因,肯定存在翻譯和理解有偏差的地方,歡迎大家指正。有部分地方存在語句不通順及錯別字,也請大家海涵。

[admin via 研發互助社區 ] 從配置PROM/FLASH讀取用戶數據已經有2304次圍觀

http://cocdig.com/docs/show-post-42999.html