設計一個FIFO是ASIC設計者遇到的最普遍的問題之一。本文著重介紹怎樣設計FIFO——這是一個看似簡單卻很複雜的任務。

一開始,要注意,FIFO通常用於時鍾域的過渡,是雙時鐘設計。換句話說,設計工程要處理(work off)兩個時鐘,因此在大多數情況下,FIFO工作於獨立的兩個時鐘之間。然而,我們不從這樣的結構開始介紹—我們將從工作在單時鐘的一個FIFO特例開始。雖然工作在同一時鐘的FIFO在實際應用中很少用到,但它為更多的複雜設計搭建一個平台,這是非常有用的。然後再從特例推廣到更為普通的FIFO,該系列文章包括以下內容:

1.單時鐘結構

2.雙時鐘結構——雙鍾結構1

3.雙時鐘結構——雙鍾結構2

4.雙時鐘結構——雙鍾結構3

5.脈衝模式FIFO

單時鐘FIFO特例

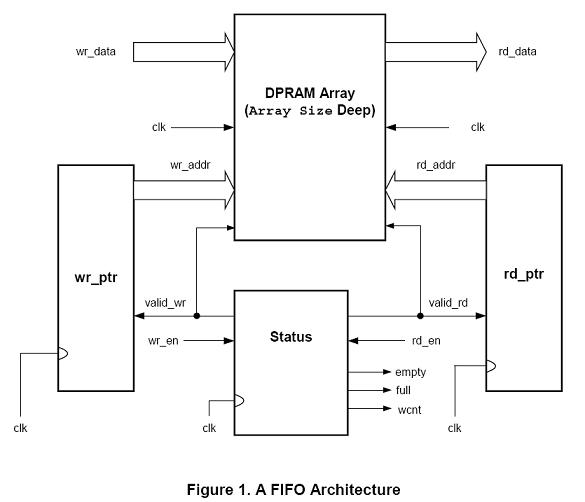

FIFO有很多種結構,包括波浪型(ripple)FIFO,移位寄存器型以及其他一些我們並不關心的結構類型。我們將集中討論包含RAM存儲器的結構類型。其結構如圖1所示。

通過分析,我們看到圖中有一個具有獨立的讀埠和獨立的寫埠的RAM存儲器。這樣選擇是為了分析方便。如果是一個單埠的存儲器,還應包含一個仲裁器保證同一時刻只能進行一項操作(讀或寫 ),我們選擇雙口RAM(無需真正的雙口RAM,因為我們只是希望有一個簡單的相互獨立的讀寫埠)是因為這些實例非常接近實際情況。

讀、寫埠擁有又兩個計數器產生的寬度為log2(array_size)的互相獨立的讀、寫地址。數據寬度是一個非常重要的參數將在在稍後的結構選擇時予以介紹,而現在我們不必過分的關心它。為了一致,我們稱這些計數器為“讀指針”(read pointer)和“寫指針”(write pointer)。寫指針指向下一個將要寫入的位置,讀指針指向下一個將要讀取的位置。每次寫操作使寫指針加1,讀操作使讀指針加1。

我們看到最下面的模塊為“狀態”(stauts) 模塊。這個模塊的任務實給FIFO提供“空”(empty)和“滿”(full)信號。這些信號告訴外部電路FIFO已經達到了臨界條件:如果出現“滿”信號,那麼FIFO為寫操作的臨界狀態,如果出現“空”信號,則FIFO為讀操作的臨界狀態。寫操作的臨界狀態(“full is active”)表示FIFO已經沒有空間來存儲更多的數據,讀操作的臨界表示FIFO沒有更多

的數據可以讀出。status模塊還可告訴FIFO中“滿”或“空”位置的數值。這是由指針的算術運算來完成了。

實際的“滿”或“空”位置計算並不是為FIFO自身提供的。它是作為一個報告機構給外部電路用的。但是,“滿”和“空”信號在FIFO中卻扮演著非常重要的角色,它為了能實現讀與寫操作各自的獨立運行而阻塞性的管理數據的存取。這種阻塞性管理的重要性不是將數據複寫(或重讀),而是指針位置可以控制整個FIFO,並且使讀、寫操作改變著指針數值。如果我們不阻止指針在臨界狀態下改變狀態,FIFO還能都一邊“吃”著數據一邊“產生”數據,這簡直是不可能的。

進一步分析:DPRAM若能夠寄存讀出的信號,這意味著存儲器的輸出數據已被寄存。如果這樣的話,讀指針將不得不設計成“read 並加1 ”,也就是說在FIFO輸出數據有效之前,必須提供一個明確的讀信號。另一方面,如果DPRAM沒有寄存輸出,一旦寫入有效數據就可以讀出;先讀數據,然後使指針加1。這將影響到從FIFO讀出數據和實現空/滿計算的邏輯。由於簡化的緣故,我們僅論述DPRAM沒有提供索鎖存輸出的情況。同理,將其推廣到寄存輸出的DPRAM並不是很複雜。

從功能上看,FIFO工作原理如下所述:複位時,讀、寫指針均為0。這是FIFO的空狀態,空標誌為高電平,(我們用高電平表示空標誌)此時滿標誌為低電平。當FIFO出現空標誌時,不允許讀操作,只能允許寫操作。寫操作寫入到位置0,並使寫指針加1。此時,空標誌變為低電平。假設沒有發生讀操作而且隨後的一段時間FIFO中只有寫操作。一定時間后,寫指針的值等於array_size-1。這就意味著在存儲器中,要寫入數據的最後一個位置就是下一個位置。在這種情況下,寫操作將寫指針變為0,並將輸出滿標誌。

注意,在這種情況下,寫指針和讀指針是相等的,但是FIFO已滿,而不是空。這意味著“滿”或“空”的決定並不是僅僅基於指針的值,而是基於引起指針值相等的操作。如果指針值相等的原因是複位或者讀操作,FIFO認為是空;如果原因是寫操作,那麼FIFO認為是滿。

現在,假設我們開始一系列的讀操作,每次讀操作都將增加讀指針的值,直到讀指針的位置等於array_size-1。在該點,從這個位置讀出的FIFO輸出匯流排上的數據是有效的。隨後的邏輯讀取這些數據並提供一個讀信號 (在一個時鐘周期內有效)。這將導致讀指針再次等於寫指針(在兩個指針走完存儲器一圈后)。然而,由於這次相等是由於一個讀操作,將會輸出空標誌。

因此,我們將得到如下的空標誌:寫操作無條件的清除空標誌。

Read pointer=(array_size-1) , 讀操作置空標誌。

以及如下的滿標誌:讀操作無條件的清除滿標誌,

Write pointer= (array_size-1), 寫操作置滿標誌。

然而,這是一個特殊的例子,由於一般情況下,讀操作在FIFO不是空的情況下就開始了(讀操作邏輯不需要等待FIFO變滿),因此這些條件不得不修改來存儲讀指針和寫指針的每一個值。

有這樣一個想法,那就是我們可以將存儲器組織成一個環形列表。因此,如果寫指針與讀指針差值大於1或更多,就進行讀操作,FIFO為空,這種工作方式對於用無符號(n-bit)結構來描述的臨界狀態非常適合。同樣的,如果讀指針與寫指針的差值大於1,就進行寫操作,直到FIFO為滿。

這將帶來如下的條件:

寫操作無條件的清除空標誌。

write_pointer=(read_pointer+1),讀操作置空。

讀操作無條件的清除滿標誌,

read_pointer= (write_pointer+1),寫操作置滿。

注意,讀操作和寫操作同時都在使其指針增加,但不改變空標誌和滿標誌的狀態。在空或滿的臨界狀態同時讀操作和寫操作都是不允許的。

綜上所述,我們現在能夠定義FIFO的status模塊,這裡提供了用VHDL編寫的代碼,由於是同步的,很容易轉換成Verilog HDL代碼。

library IEEE, STD;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity status is

port (reset : in std_logic;

clk : in std_logic;

fifo_wr : in std_logic;

fifo_rd : in std_logic;

valid_rd : out std_logic;

valid_wr : out std_logic;

rd_ptr : out std_logic_vector(4 downto 0);

wr_ptr : out std_logic_vector(4 downto 0);

empty : out std_logic;

full : out std_logic

);

end status;

architecture status_A of status is

signal rd_ptr_s : std_logic_vector(4 downto 0);

signal wr_ptr_s : std_logic_vector(4 downto 0);

signal valid_rd_s : std_logic;

signal valid_wr_s : std_logic;

begin

empty_P : process(clk, reset)

begin

if (reset = '1') then

empty <= '1';

elsif (clk'event and clk = '1') then

if (fifo_wr = '1' and fifo_rd = '1') then

-- do nothing

null;

elsif (fifo_wr = '1') then

-- write unconditionally clears empty

empty <= '0';

elsif (fifo_rd = '1' and (wr_ptr_s = rd_ptr_s + '1')) then

-- set empty

empty <= '1';

end if;

end if;

end process;

full_P : process(clk, reset)

begin

if (reset = '1') then

full <= '0';

elsif (clk'event and clk = '1') then

if (fifo_rd = '1' and fifo_wr = '1') then

-- do nothing

null;

elsif (fifo_rd = '1') then

-- read unconditionally clears full

full <= '0';

elsif (fifo_wr = '1' and (rd_ptr_s = wr_ptr_s + '1')) then

-- set full

full <= '1';

end if;

end if;

end process;

valid_rd_s <= '1' when (empty = '0' and fifo_rd = '1');

valid_wr_s <= '1' when (full = '0' and fifo_wr = '1');

wr_ptr_s_P : process(clk, reset)

begin

if (reset = '1') then

wr_ptr_s_P <= (others => '0');

elsif (clk'event and clk = '1') then

if (valid_wr_s = '1') then

wr_ptr_s <= wr_ptr_s + '1';

end if;

end if;

end process;

rd_ptr_s_P : process(clk, reset)

begin

if (reset = '1') then

rd_ptr_s_P <= (others => '0');

elsif (clk'event and clk = '1') then

if (valid_rd_s = '1') then

rd_ptr_s <= rd_ptr_s + '1';

end if;

end if;

end process;

rd_ptr <= rd_ptr_s;

wr_ptr <= wr_ptr_s;

end status_A;

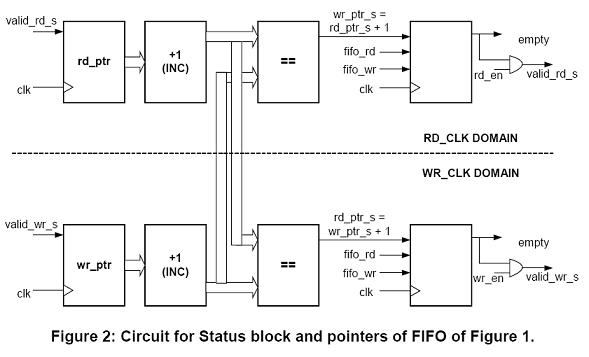

電路圖如圖2所示:

細心的讀者會注意到圖2中產生滿或空標誌需要同時用到兩個指針。在雙時鐘設計的情況下,希望用讀指針處理(work off) 讀時鐘,寫指針處理(work off) 寫時鐘。這會引起不希望發生的毛刺問題——自己可以去試一試,看一看。這些問題以及一些解決方案將在後續的該系列文章中提及。

PS: 文章中三次提到 work off clock,分別在開頭和結尾處,work off字面意思是“去除,消除,出售”的意思,可是在FIFO中,不應該是去除的意思,故根據前後文和常識,將其翻譯為“處理”,有不對的地方請批評指正!

[admin via 研發互助社區 ] 非同步FIFO結構已經有6345次圍觀

http://cocdig.com/docs/show-post-42993.html