1 引言

ARM作為一種16/32位高性能、低成本、低功耗的嵌入式RISC微處理器。普遍應用於工業控制、消費類電子產品、通信系統、無線系統等產品。大多數ARM微控制器都集成了DMA控制器。且直接內存存取(DMA)作為一種獨立於CPU的後台批量數據傳輸技術,以其快速、高效的特點在數據採集領域得到了廣泛的應用。本文以三星公司的S3C2410為例,介紹了其內部DMA控制器的特點和使用方法.以S3C2410和FPGA為核心結合DMA技術設計了CCD相機採集系統,並且給出Linux操作系統下DMA設備驅動程序的設計方法。

2 DMA工作過程簡介

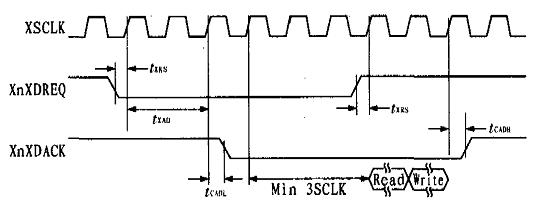

S3C2410是基於ARM920T內核的RISC微處理器.主頻可達203 MHz,適用於信息家電、手持設備、移動終端等領域。S3C2410可提供4個DMA通道.用於系統匯流排內部或與外圍匯流排之間的數據交換。現以外部DMA請求為例簡要介紹DMA的工作過程。圖1所示為DMA基本工作時序。

圖1 DMA基本工作時序圖

當需要進行DMA操作時,外部DMA請求引腳XnXDREQ置為低電平。此時DMA控制器向CPU發出佔用匯流排的請求,當匯流排請求成功后,XnXDACK引腳變為低電平,表示CPU已經將匯流排使用權交給DMA控制器,可以進行數據傳輸。當數據傳輸完成後應答信號XnXDACK置為高電平,通知CPU完成一次DMA操作。

S3C2410提供了3種不同的DMA操作模式,分別是單服務命令模式、單服務握手模式和全服務握手模式。在利用DMA進行數據傳輸前必須對其相關寄存器進行設置。主要有:源地址寄存器、目的地址寄存器和各自的控制寄存器,以及配置DMA模式的控制寄存器等。

3 採集系統硬體設計

根據DMA的特點,設計了基於ARM和FPGA的CCD相機採集系統。系統結構如圖2所示。

FPGA選用Altera公司的Cyclone系列器件EP1C6T144C8,可為CCD相機提供工作所需的驅動時序.同時接收經模數轉換的CCD輸出圖像數據。S3C2410通過DMA方式從FPGA內部採集數據,通過數據線、DMA信號線、片選信號和輸出時鐘線與FPGA相連。

這裡主要介紹DMA方式的數據採集,FPGA內部的CCD驅動邏輯暫不介紹。FPGA與ARM的介面邏輯電路如圖3所示。

FPGA內部採用非同步FIFO解決CCD輸出數據頻率和S3C2410採集頻率不匹配的問題,寫時鐘由CCD輸出位同步信號提供,讀時鐘由S3C2410的時鐘輸出引腳CLKOUT0提供。CLKOUT0根據ARM內部寄存器的設置可以輸出不同的時鐘頻率。FIFO輸出數據經過以nGCS4為選通信號的BUFFER後接到ARM的數據匯流排上。nGCS4是S3C2410存儲空間中BNAK4的片選信號,當S3C2410對地址範圍

0x20000000~0x28000000的存儲空間進行讀寫操作時,BANK4為低電平,其餘時間均為高電平.用它作為BUFFER的選通信號能有效地避免數據匯流排的污染。

FIFO的寫請求信號由S3C2410與FIFO的滿狀態共同控制。當ARM發出START信號並且FIFO未滿時,寫請求信號為高電平。FIFO在寫時鐘的控制下寫入數據。當START信號撤銷或者FIFO滿時,寫請求信號變為低電平,停止寫操作。

FIFO的讀操作與ARM的DMA操作配合進行。系統採用單服務命令模式的DMA操作,每次傳輸一個位元組數據位。當DREQ0信號變為低電平時DMA操作開始,每次傳輸一個位元組后產生一個DACK0應答信號,而且只要DREQ0為低電平DMA操作就繼續進行,直到DMA控制寄存器中的計數器為0.產生DMA中斷。根據上述時序特點,將FIFO的空信號作為DMA的請求信號DREQ0.當CCD輸出的數據寫入FIFO中時,空信號跳變為低電平啟動DMA操作,同時以DACK0信號作為FIFO的讀請求。每一次DMA傳輸完成後應答信號使FIFO的讀指針移動一位,以實現數據的快速準確採集。

4 Linux下的驅動程序設計

系統採用ARM+嵌入式Linux的構架,Linux版本為2.4.18,採集系統必須和高效靈活的介面驅動程序相結合才能在操作系統下正常工作。

4.1 驅動程序的基本概念

設備驅動程序是操作系統內核和硬體之間的介面,它屬於內核一部分,主要功能如下:

(1)對設備初始化或釋放;

(2)把數據從內核傳送至硬體。從硬體讀取數據:

(3)讀取應用程序傳送給設備的數據,回送應用程序請求的數據:

(4)監測和處理設備出現的異常。

設備驅動程序為應用程序屏蔽了硬體的細節,在應用程序中,硬體設備只是一個設備文件,可以像操作普通文件一樣對硬體設備進行操作。

4.2 修改代碼

嵌入式Linux在arch/arm/mach-s3c2410目錄下的dma.c文件中定義了一些與DMA操作相關的通用函數,主要有:申請DMA通道函數s3c2410_re,quest_dma()、申請DMA中斷函數request_irq()、加入DMA隊列函數s3c2410_dma_queue_buffer()、進行DMA操作函數process_dma()以及中斷處理程序dma_irq_handler()等。在進行特定介面操作時,必須對其進行適當的修改。根據介面設置修改如下內容:

增加外部DMA操作的寄存器設置:

#define XDREQ0_CTL(DEMAND_MODE | SYNC_HCLK | INT_MODE | TSZ_UNIT

| SINGLE_SERVICE | HWSRC(CH0_nXDREQ0) | DMA_SRC_HW | CLR_ATRELOAD | DSZ(DSZ_BYTE)| TX_CNT(0));

//設置DMA為單服務命令模式,8位數據匯流排、允許中斷且通過DREQ0硬體觸發DMA操作

#define XDREQ0_RD_SRC 0x22000000

#define XDREQ0_RD_SRC_CTL BUF_ON_MEM_FIX

//設置DMA操作的源地址為系統匯流排上的0x22000000且地址固定

#define XDREQO_RD_DST_CTL BUF_ON_MEM

//設置DMA操作的目的地址在系統匯流排且地址逐次加1

通過DMA讀取FPGA數據時必須由操作系統在內存中開闢一個空間做為DMA操作的目的地址。操作系統開闢的內存位於虛擬空間.而DMA操作的目的地址必須為物理地址,所以必須進行虛擬地址到物理地址的轉換。因此在process_dma()中增加如下代碼設置DMA的目的地址寄存器:

regs->DIDST=virt_to_bus(buf->dma_start)

virt_to_bus()是操作系統提供的虛擬地址到物理地址的轉換函數,buf->dma_start是系統開闢的虛擬地址空間的首地址。

另外由介面原理圖可知,S3C2410須向FPGA發送START信號啟動FIFO的讀寫和DMA操作。所以系統定義GPB3作為START信號,定義如下:

#define START(GPIO_MODE_OUT | GPIO_PULLUP_DIS | GPIO_B3);

同時在process_dma()函數中增加如下代碼啟動DMA操作:

write_gpio_bit(START,1);

START引腳置為高電平后立即啟動FIFO的寫操作,同時也就啟動了DMA操作進行數據傳輸,當DMA計數器減為0后發生DMA中斷,並且在中斷處理程序中將START位置0停止FIFO的寫操作。

4.3 介面驅動的關鍵代碼

利用系統提供的DMA操作函數,介面驅動的設計就顯得比較容易。介面驅動屬於字元設備驅動.重點在初始化和read函數部分。

初始化函數中完成DMA引腳定義、BANK4匯流排設置、申請DMA通道以及註冊字元設備等。read函數是介面驅動的核心。應用程序正是通過調用read函數來讀取數據。其核心代碼如下:

fpga_buf_t *b=&fpga_buf;

dma_addr_t *buf;

b->size=count;

buf=kmalloc(b->size,GFP_DMA);

s3c2410 dma_queue_buffer(b->dma_ch,(void*)b,buf,b->size,DMA_BUF_RD);

if(copy_to_user(buff,buf,b->size))

return -EFAULT;

kfree(buf);

return b->size;

系統調用read函數時首先通過kmalloc分配一段虛擬內存空間,並將其指針和DMA通道、傳輸位元組數一起通過s3c2410_dma_queue_buffer()加入DMA隊列.在隊列函數中調用process_dma()函數將

虛擬地址轉換為物理地址並且啟動DMA操作。DMA操作完成後退出隊列並調用copy_to_user()將採集到的數據由內核空間拷貝到用戶空間進行後續操作。

5 測試結果

圖4為邏輯分析儀測得的數據採集時序圖,A1表示FIFO中寫入的數據數量;A2表示ARM採集到的數據;A3(0)表示讀時鐘CLKOUTO,頻率為101.5 MHz;A3(1)表示片選信號nGCS4;A3(2)為DMA應答信號DACKO,即FIFO的讀請求信號;A3(3)表示FIFO的空信號,即DMA的請求信號DREQO;A3(4)表示FIFO的複位信號,高電平複位,低電平開始工作;A3(5)表示FIFO的寫時鐘,頻率為5 MHz;A3(6)表示寫請求;A3(7)表示FIFO滿信號。

由測試結果可以看出.DMA操作完全符合時序要求.一次數據採集所需時間約為220 ns,系統工作穩定正常。

6 結束語

本文討論了S3C2410微控制器的DMA通道在數據採集中的應用,並通過與FPGA相配合設計了基於DMA方式的數據採集系統,同時給出了Linux下設備驅動程序的設計思路。文章所設計的數據採集介面具有很強的通用性,可以廣泛用於各種信號量的採集。

[admin via 研發互助社區 ] ARM系統中DMA方式在數據採集中的應用已經有3929次圍觀

http://cocdig.com/docs/show-post-42243.html