1 引言

在以單片機為核心的測控系統中.微控制器往往需要兩個或兩個以上的串列口與其他主機或外設進行通訊,如何使系統具備多個串列介面,是一個具有普遍性的問題。尤其在航空航天領域,由於GPS、大氣數據系統、數字羅盤、無線電高度表、甚至陀螺等航空電子設備普遍採用串列通訊方式,單片計算機系統就更需要有多個串列口以滿足與外界信息交換的需要。

2 常用的多串列口設計方法

①選用多串列口單片機

直接選用多串列口單片機作為系統的CPU,顯然是最直接有效的方法。現在有許多新型CPU配備兩個或兩個以上串列口,如W77E58、DS80C320、MSP430F149、C8051F020單片機和數字信號處理器TMS320C30有兩個串列口,而cygnal的C8051F系列單片機有4-5個全雙工的非同步串列口。

②用CPU的I/O模擬串列口

當串列口的波特率設為9600波特時,傳送一個bit需要100us左右,對於一般的單片機而言,軟體定時器完全有能力按非同步串列通訊協議模擬出串列口的時序。所以,用CPU的兩個I/O口和一個軟體定時器,就可以純粹用軟體模擬出一個串列口來。文獻介紹了一種具體的實現方法,發送時,只需按時序一位一位輸出數據即可,接收時,首先利用外部中斷檢測到I/O接收口上的起始電平,然後利用定時器按半個bit的時間長度延時接收第一個bit的數據,再按一個bit的時間長度延時依此讀取其他位的信號。

③基於高速輸入輸出的軟體串列口

80C196系列單片機配備了高速輸入HSI和高速輸出HSO介面.可以利用HSI和HSO來模擬串列口。數據的輸出利用HSO,只要在HSO的定時器里寫入與波特率對應的延遲時間,HSO每中斷一次,輸出一個數據位,直到停止位輸出完畢。接收時,利用HSI自身的信號跳變檢測功能檢測起始位,併產生中斷通知CPU開始接收數據,後續的數據位由軟體定時器按波特率定時讀取。文獻詳細介紹了實現方法,並給出了完整的程序代碼;本方法在80C196MC/MD單片機中。則表現為事件處理陣列EPA和外設事物伺服器PTS的應用,其優點是EPA的每個模塊與CPU的指定引腳對應,減少了軟體開銷和程序設計的複雜度。

④16C550系列可編程通訊控制器

利用并行口擴展串列口的介面晶元種類較多,其中16C550系列通訊控制器普遍應用於計算機控制系統和通訊設備,以實現CPU與串列口和MODEM的通訊。16C550配備一個串列口,16C552配備兩個串列口,而16C554配備四個串列口。16C550系列器件的實質是實現串列口與CPU并行口的轉換,其自身有較強的數字邏輯功能。16C550系列器件的串列口工作方式均可編程,有的還帶有開關量輸入輸出介面,可以作為CPU的開關量擴展介面用。

⑤用分立器件將并行口轉換為串列口

文獻提供了一種利用555定時器、D觸發器和移位寄存器等分立元件實現串、並口互相轉換的電路。該電路用定時器產生與波特率一直的同步時鐘信號,把接收到的數據移位寄存到並口供CPU讀取,或把并行口的數據移位發出,其實質是用若干個分立元件模擬16C550的功能。

⑥串列口擴展晶元

現在有一種專門的SP系列串列口擴展晶元,可以將一路高速的全雙工串列口擴展為多路的低速全雙工串列口,串口的波特率通過晶振統一確定。如SP2328和SP2338可以將一路母串口擴展為三路子串口,SP2538可以將一路母串口擴展為五路子串口。該系列晶元有輸入地址線和輸出地址線,在通過母串口向子串口發送數據時要給輸出地址線上加選擇電平,確定從哪一路子串口輸出,在通過母串口從子串口讀取數據時要檢測輸入地址線的電平,以確定是哪一路子串口的信號。該系列晶元應該是採用分時機制,通過內部的邏輯電路將一路數據分解為多路或將多路數據合成為一路。如SP2328母串口的波特率是子串口波特率的四倍,SP2538母串口的波特率是子串口波特率的六倍。

⑦用多路復用器擴展串列口

文獻提供了一種利用多路復用器MAX353將一路串列口擴展為兩路的方法。在發送信號的時候,CPU先給出MAX353的埠選擇地址,串列信號經多路復用器的切換,從指定通道發送出去。在接受信號的時候,將多路復用器默認為第一通道,第二路串列口的RXD2同時接到(2PU的外部中斷引腳上。如果第一通道有數據,則直接接收。如果第二通道有數據.RXD2的起始位將產生一個外部中斷,CPU進入中斷響應程序,將復用器切換到第二通道,接受RXD2的數據。一個位元組接收完畢后,將復用器切換回第一通道。

文獻的方法佔用了一個外部中斷,且只能將一路串口擴展為兩路。基於同樣的思路,可以利用四選一多路復用器將一路串列口擴展為兩路以上。發送

數據的操作過程同上。為了實現數據的接收,需要用可編程邏輯器件或鎖存器及編碼器設計一個通道選擇電路,哪一路先有起始位,將多路復用器選通到哪一路。CPU根據通道選擇電路的輸出確定所收數據的通道編號。

⑧運用FPGA/CPLD設計串列口

FPGA/CPLD具有強大的電路模擬功能。利用FPGA/CPLD可以設計并行口轉串列口的時序邏輯電路,該電路一般由四部分組成:匯流排介面與控制邏輯部分、波特率發生部分、移位輸出與鎖存部分、移位輸入與鎖存部分。該電路波特率可以調節,有片選線和讀寫線。CPU通過并行口對電路進行訪問。從實質上說,該電路模擬了可編程式控制制器16C550的串列介面功能。事實上,FPGA/CPLD有很大的靈活性。可根據實際需要和系統資源對電路進行適當裁剪,也可把多路復用技術或時分復用技術運用於串列口的模擬。

3 多串列口設計方法的比較研究與選擇原則

以上8種方法,各有利弊。顯然,選用多串口CPU是最為直接有效的方法,但是選用一種新型號的CPU,對於開發者來說,有一定的開發風險,有時還有受到供貨渠道和開發條件的限制。選用專用晶元是一種可靠性最高的串口外部擴展法,有技術成熟、軟體工作量小等諸多優勢。不足之處是硬體成本增加、體積增加,有時還要佔用外部中斷源。選用多路復用器。其好處是可以實現CPU一點對多點的通訊、軟硬體成本低、可靠性高,致命缺點是CPU不能同時接收多路輸入數據。選用FPGA/CPLD既可以設計串列介面本身,又可以用來實現多路串口切換,或管理多個串列介面晶元的中斷源。優點是可靠性高、CPU軟體開銷小,不足是開發成本稍大、硬體成本高。用分立元件實現串列口的轉換,優點是軟體工作量小,不足是電路複雜、可靠性差、要佔用外部中斷源。利用軟體模擬串列介面,其優點不言而喻.既不增加任何硬體,又不佔用外部中斷源。缺點是軟體複雜度高、CPU開銷大、要佔用軟體定時器。

以上八種多串口的設計方法可以歸納為五種設計思想:

①直接從CPU上下手,選擇多串列口單片機;

②挖掘器件本身的資源,在CPU I/O口線上用軟體模擬串列口;

③使用功能電路實現串、並轉換;

④使用功能電路將一路高速串列口分解為多路低速串列口;

⑤通過分時復用實現一路到多路的切換。

針對這幾種不同的設計思想和其具體的實現方法,在應用時該如何選擇,不但要依據以上幾種方法的軟硬體複雜度、CPU時間開銷、實時性和可靠性,還要依據應用系統中所需串列介面的總路數、各個串口之間的獨立性和波特率,以及現有的開發條件和綜合成本指標。選擇時要根據各種因素進行綜合權衡。要在能實現所要求功能的基礎上,充分利用現有資源、降低系統的複雜度、提高可靠性,力求使設計代價最小、總體成本最低。當然,這些方法的選擇應該靈活多樣,不必拘泥於一種方法,也可以因地制宜地選擇幾種方法的組合。

4 應用舉例

在某型無人機飛行控制器設計中,CPU選用的是80C196KC。CPU上原有的一路串口用於遙控遙測。為了測量飛機的航向角。系統中應用了數字羅盤HMR3000。該感測器為串口介面,波特率為19200,輸出數據為NMEAC183格式,每秒20幀,每幀35位元組,為此需要給控制器增加一路全雙工非同步串列介面。

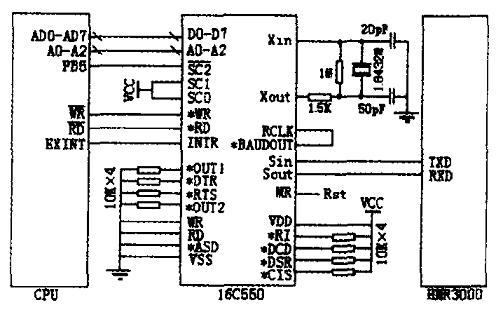

基於對以上8種設計方法的比較與分析,在權衡系統的軟硬體複雜度之後,選用了第四種方法,即利用16C550可編程通訊控制器擴展出一路串列口。專門與該感測器通訊。16C550使用了FIFO功能,在接收14個位元組後向CPU提出一次中斷請求。這樣CPU最多中斷4次就可以全部接收一幀姿態測量數據。控制器的軟體對HMR3000一幀輸出數據的解碼時間僅為1.187ms,CPU的負擔並不大。CPU、16C550和HMR3000的連接電路如圖1所示。

圖1 可編程通訊控制器16C550與單片機系統的介面電路圖

本方法充分利用了16C550的FIFO功能.所選擇的方案無論從可靠性上、體積上、硬體複雜度上還是從成本、CPU的負擔上來說,都明顯優於文獻的方案。

參考文獻

【1】孫涵芳.INTEL16位單片機[M],北京:北京航空航天大學出版社,1995.

[admin via 研發互助社區 ] 單片機系統多串列口設計技術研究已經有2510次圍觀

http://cocdig.com/docs/show-post-42166.html