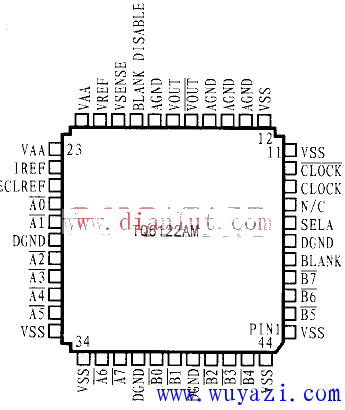

| 數模轉換器TQ6122的引腳排列

TQ6122的引腳功能

TQ6122的引腳排列圖如圖所示。各引腳的說明如下(括弧中的數字為引腳號):

AGND(13、14、15、18):模擬地。

BLANK(5):該端置高且下降延到達時,內部數據位都被置高。

SELA(7):置高時選擇A端數據輸入,置低時選擇B端數據輸入。

A0~A8(26、27等36):數字信號輸入端,A7為數據最高位,A0為數據最低位。

B0、…… B7(38等):數字信號輸入端,B7為數據最高位,B0為數據最低位。

CLOCK、 CLOCK(9、10):差分時鐘輸入端。

VOUT、VOUT(16、17):模擬信號輸出端,為差分信號。

BLANK DISABLE(19):如果需要用BLANK端,則連到VAA端,若不需要,則連到AGND。

IREF(24):輸入參考電流,直接連接到模擬地,是開關陣列的虛擬電流源。

VSENSE(20):輸出判斷電壓,晶元正常工作時有輸出,且VSENSE=-4.2V。

VREF(21):電壓基準輸入端,一般在其VREF=-4V時,輸出的模擬信號峰值為1V。

ECLREF(25):可選的ECL電平參考電壓,當數據和時鐘為ECL電平時,該腳可不接,此時晶元內部產生電壓為-1.3V。 |