| CD4000/74系列是邏輯IC中使用最多的。74系列原來可以說是TTL的代名詞,目前,由於CMOS型的74系列也有很多種類做出,在許多高速的邏輯系統中, 幾乎僅有可能使用CMOS的74系列設計。 74系列的種類與特徵 74系列的各種形式如表1所示 表1 74系列的數字元IC的種類與區別 | TTL型 | IC編號 | VOH | VIH | VOL | VIL | 傳遞延遲 | 功率消耗 | | | 標準型 | 74XX | 2.4V | 2.0V | 0.4V | 0.8V | 9ns | 10mW | | | 低功率型 | 74LXX | 2.4V | 2.0V | 0.3V | 0.8V | 33 ns | 1 mW | | | 高速型 | 74HXX | 2.4V | 2.0V | 0.4V | 0.8V | 6 ns | 23 mW | | | 蕭特基型 | 74SXX | 2.7V | 2.0V | 0.5V | 0.8V | 3 ns | 23 mW | | | 低功率蕭特基型 | 74LSXX | 2.7V | 2.0V | 0.5V | 0.8V | 9.5 ns | 2 mW | | | 高級蕭特基型 | 74ASXX | 3.0V | 2.0V | 0.5V | 0.8V | 1.5 ns | 8 mW | | | 高級低功率蕭特基型 | 74ALSXX | 3.0V | 2.0V | 0.4V | 0.8V | 4 ns | 1.2 mW | | | CMOS型 | | | 早期CMOS | CD40XX CD45XX | | | | | | 0.01 mW | | | 第一個以CMOS設計而接腳與TTL兼容的CMOS 版本 | 74Cxx | | 3.5V | 0.1V | 1.5V | 7 ns | 0.01 mW | 與TTL引腳相容 | | 以高速CMOS做的IC | 74HCxx | 4.9V | 3.5V | 0.1V | 1.5V | 7 ns | 0.01 mW | 與TTL引腳相容 | | 高速CMOS | 74HCTxx | 4.9V | 2.0V | 0.1V | 0.8V | 8 ns | 0.01 mW | 與TTL引腳,電性能兼容 | | 高速CMOS,設計用來與74ALS競爭 | 74ACxx | 4.9V | 3.5V | 0.1V | 1.5V | 6 ns | 0.01 mW | 與TTL引腳,電性能不兼容 | | 高性能CMOS | 74ACTxx | 4.9V | 3.5V | 0.1V | 1.5V | 6 ns | 0.01 mW | 與TTL引腳不兼容,但電性能相同 | 註:XX處一般為2~3位數的數字,各代表同一功能。在CMOS邏輯IC有加入4位數的數字 對MOS/CMOS IC,應注意:

(1) 輸入電壓絕不可超過VDD值,但對4049及4050為例外。

(2) 如可能的話,避免應用慢速之上升及下降時間之輸入信號,此舉將使組件耗用功率增大;上升時間大於15us以上之輸入信號為最佳。

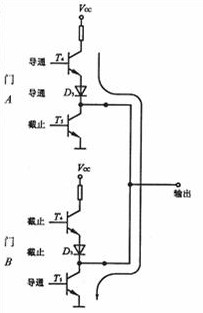

(4) 當組件尚未接入工作電壓時,絕不可將輸入信號接至該CMOS信號輸入引腳上。 靜電問題: 你知道嗎?對電路而言,你的身體好像一個100pF 的電容和一個幾M的電阻。在較乾燥的天氣,靜電可以把你充電到10kV,是的!不要懷疑,一萬伏特的電壓在你身上。空氣的遊離(崩潰)電壓約10kV/cm,有時候手指碰到門把前所產生的火花就是靜電使空氣遊離所導致的。而MOS 閘極的崩潰電壓只有不到100 伏特。 MOS 組件在運送或儲藏時,必須插在導電的泡棉或裝在導電的袋子中。你也必須小心烙鐵和桌上的靜電,常將你自己的身體和處理的電路接地(你和地間最好串接一個1MW的電阻)。有一些MOS 組件會有閘極保護電路的設計,雖然會使得特性表現差一點,但被靜電燒壞的機率卻小很多。有時候,你買到的FET引腳上有保護的金屬線或導電橡皮筋,要到FET 裝在電路后才能拆掉。 使用的問題: 數字系統中,有時需把兩個或兩個以上集成邏輯門的輸出端連接起來,完成一定的邏輯功能。普通TTL門電路的輸出端是不允許直接連接的。圖1示出了兩個TTL門輸出短接的情況,為簡單起見,圖中只畫出了兩個與非門的推拉式輸出級。設門A處於截止狀態,若不短接,輸出應為高電平;設門B處於導通狀態,若不短接,輸出應為低電平。在把門A和門B的輸出端作如圖1所示連接后,從電源Vcc經門A中導通的T4、D3和門B中導通的 T5到地,有了一條通路,其不良後果為:圖1 不正常情況:普通TTL門電路輸出端短接

(1)輸出電平既非高電平,也非低電平,而是兩者之間的某一值,導致邏輯功能混亂。

(2)上述通路導致輸出級電流遠大於正常值(正常情況下T4和T5總有一個截止),導致功耗劇增,發熱增大,可能燒壞器件。

圖1 不正常情況:普通TTL門電路輸出端短接

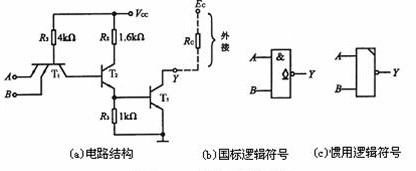

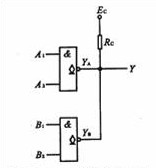

(1) 實現電平轉換圖3 OC門的線與應用

無論是用TTL電路驅動CMOS電路還是用CMOS電路驅動TTL電路,驅動門必須能為負載門提供合乎標準的高、低電平和足夠的驅動電流,即必須同時滿足下列四式:

驅動門 負載門

VOH(min) ≥ VIH(min)

VOL(max) ≤ VIL(max)

IOH(max) ≥ IIH

IOL(max) ≥ IIL

圖3 OC門的線與應用

其中:VOH(min)--門電路輸出高電平VOH的下限值;

VOL(max) --門電路輸出低電平VOL的上限值;

IOH(max)--門電路帶拉電流負載的能力,或稱放電流能力;

IOL(max)—門電路帶灌電流負載的能力,或稱吸電流能力;

VIH(min)--為能保證電路處於導通狀態的最小輸入(高)電平;

VIL(max) --為能保證電路處於截止狀態的最大輸入(低)電平。

IIH — 輸入高電平時流入輸入端的電流;

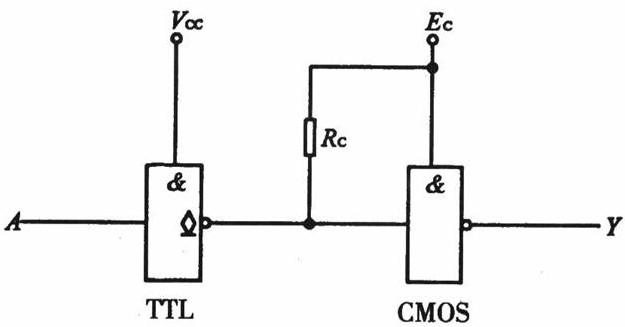

IIL -- 輸入低電平時流出輸入端的電流。 當74系列或74LS系列TTL電路驅動CD4000系列或74HC系列CMOS電路時,不能直接驅動,因為74系列的TTL電路VOH(min) = 2.4V,74LS系列的TTL電路VOH(min)=2.7V,CD4000系列的CMOS電路VIH(min)=3.5V,74HC系列CMOS電路VIH(min)=3.15V,顯然不滿足VOH(min) ≥ VIH(min)

最簡單的解決方法是在TTL電路的輸出端與電源之間接入上拉電阻Rc,如圖4所

圖4 TTL(OC)門驅動CMOS電路的電平轉換 |