| 雙冗餘CAN匯流排模塊設計主要包括硬體與軟體設計兩部分。為實現冗餘功能,硬體上需要有幾個相同可獨立工作的設備支持;軟體上要具備錯誤檢測和動態切換功能,且切換時間要儘可能短。

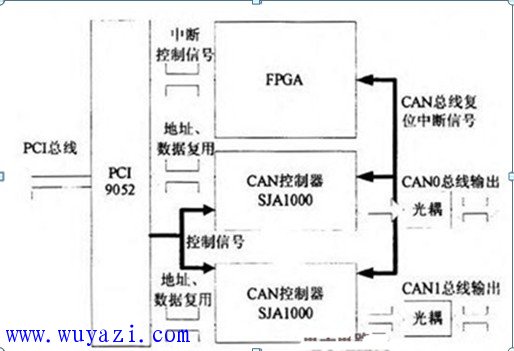

下圖為一款雙冗餘CAN匯流排模塊設計原理電路圖。

匯流排模塊設計原理電路圖

我們選擇PCI9052作為介面晶元,利用功能晶元實現硬體的邏輯和物理實現。CAN控 制器採用PHILIPS的SJAl000,可工作於BasicCAN模式或PeI.CAN模式下,其中PeIiCAN模式支持CAN 2.0B協議,採用8位地址/數據復用匯流排介面。

PC J匯流排雙CAN介面卡由兩片SJAl000提供兩路獨立的CAN介面,每片晶元的8位地址/數據匯流排和讀寫控制信號。鎖存信號直接與PCI9052相連。 SJAl000輸出信號經過光耦到CAN收發器PCA82C250,82C250供電電源為隔離電源,由隔離電源轉換模塊提供。CAN匯流排的複位信號由FPGA提供,CAN控制器SJAl000的中斷信號輸出到FPGA. |