| 1.何謂CPLD

由於信息工業發展訊速,從一般人之日常生活就可見一般;小至每個人手上的行動電督、家家戶戶皆有之洗衣機、停車場的全自動化,大到銀行里的資料庫、飛機上的自動駕駛,無一不是計算機所及的地方,而不論是計算機本身亦或其外圍之,皆為數字電路之產物。

對於大部份學習數字電路設計的人來說,其學習過程大抵從最簡單的組合邏輯電路設計開始,接著便是順序邏輯、簡易之模塊設計、至比較複雜完整之系統設計。

傳統的實驗方式,每做一個實驗就必須重組一個硬體線路,特別是複雜的線路,相當費時耗力且不易進行,因此也就常省略跳過,導致缺乏設計架構稍大且完整的電路的經驗。

為了改進以往數字電路學習方式的缺點,並且縮短開發大型數字電路的時間,所以有了整合式數字電路設計環境的發展,此種環境是以個人計算機為平台,配合電子設計自動化(EDA)軟體的執行,達到從電路設計輸入、模擬エ下載驗證、修改、燒錄一氣呵成,而且也讓自行設計開發邏輯晶元的夢想得以實現。

是何因素促成數字電路學習的方式改變呢?究其原因首推可程序邏輯組件(PLD)的快速發展。邏輯晶元大致上分成標準邏輯晶元(Standard Logic)與應用規格晶元(ASIC)兩類;而PLD為ASIC之一種。

PLD由小而大分為以下幾種:小型/簡單型PLD(Simple PLD)、複雜型CPLD(Complex PLD)、場可規劃型門陣列(FPGA)。

CPLD是較複雜的邏輯組件,它整合了更多的PLD邏輯方塊及相互關係聯機架構,晶元內含多個類似PAL的方塊及可程序化之繞線。

2.CPLD架構區分

分為EEPROM(Flash)架構和SRAM架構:

EEPROM架構密度小,多用於5,000門以下的小規模設計,適合做複雜的組合邏輯,如:編碼器。

SRAM架構的CPLD(FPGA),密度高,緩存器多,多用於10,000閘以上的大型設計,適合做複雜的時序邏輯,如數字信號處理及各種演演算法等。

三、CPLD基本結構

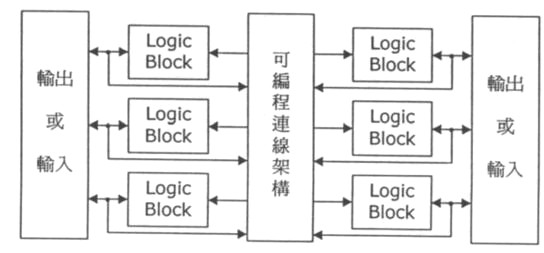

CPLD 是Complex PLD 的簡稱,顧名思義,其系一種較PLD 為複雜的邏輯組件。CPLD 是一種整合性較高的邏輯組件。由於具有高整合性的特點,故其有性能提升,可靠性增加,PCB 面積減少及成本下降等優點。CPLD 組件,基本上是由許多個邏輯方塊(Logic Blocks)所組合而成的。而各個邏輯方塊均相似於一個簡單的PLD 組件(如22V10)。邏輯方塊間的相互關係則由可編程的連線架構,將整個邏輯電路合成而成。CPLD 的架構方塊圖,如下

圖(一)所示。

圖一、CPLD 之架構方塊圖

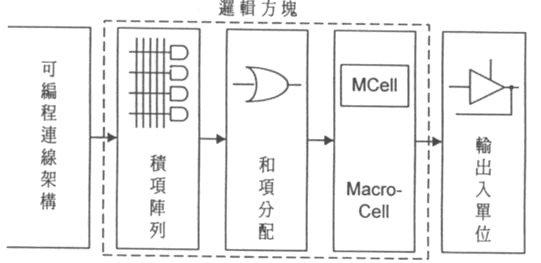

每一個邏輯方塊(Logic Block)內的內部示意圖,則如下圖(二)所示。

圖二、邏輯方塊(Logic Block)內部之架構示意圖

常見的CPLD 組件有Altera 公司的Max 5000 及Max 7000 系列、Cypress 的Max 340 及Flash 370 系列...等,一般來說CPLD 組件的可邏輯門數(gate count)約在1000~7000 Gate之間。

因此目前在CPLD裝置的發展上,通常都是怎麼選用的,是否會覺得:CPLD(Complex Programmable Logic Device;複雜可程序邏輯裝置)在整個PLD領域中,似乎有點像是個演進歷程的步階性產品,比CPLD簡易的有SPLD(Simple Programmable Logic Device;簡易可程序邏輯裝置),而比CPLD複雜的則有FPGA(Field Programmable Gate Array;現場可程序邏輯數組)。在諸多特性表現上CPLD也都是介於SPLD與FPGA間,如邏輯資源密度、功耗用電、封裝大小與引腳數目、以及價格等,因此也認為,CPLD面臨「高不成、低不就的夾心危機」。 |