隨著大規模集成電路技術的進步和製造工藝水平的提高,嵌入式系統的開發變得日益複雜。傳統的嵌入式系統設計方法已經不能適應當前嵌入式系統設計的需要。單個晶元容量的增大、功能的增加、體積的減小使得設計變得更加便利,同時也為嵌入式系統設計開發開闢了新的天地即片上系統(System on Chip,SoC)技術。

1 嵌入式系統的開發過程

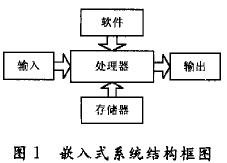

根據IEEE的定義,嵌入式系統是控制、監視或者輔助設備、機器和車間運行的裝置。因此,嵌入式系統是軟體和硬體的綜合體,以應用為中心,以計算機技術為基礎,軟硬體資源可裁剪,適應應用系統對功能、可靠性、成本、體積、功耗等嚴格要求的專用計算機系統。一般而言嵌入式系統的開發主要包括4個部分:處理器、存儲器、輸入/輸出(I/O)和軟體,如圖1所示。

2 Nios II內核嵌入式開發板的實現

嵌入式系統的核心部件是各種類型的嵌入式處理器。因此,我們著眼於嵌入式處理器的SoC開發。本節將對基於Nios II內核的嵌入式SOPC開發板設計進行詳細的介紹。

2.1 Nios II 內核的設計

Nios II系列嵌入式處理器是一款採用流水線技術、單指令流的RISC CPU,廣泛應用於嵌入式系統。Nios II包括3種內核,即快速的F(最高性能的優化)內核、經濟的E(最小邏輯佔用的優化)內核以及標準的S(平衡於性能和尺寸)內核,每種內核根據不同的性能而優化。考慮到性能和成本,通常採用Nios II標準內核設計。

Nios II嵌入式CPU支持32位指令集,32位數據線寬度,32個通用寄存器,32個外部中斷源,2 GB定址空間,包含高達256個用戶自定義的CPU定製指令。其可選的片上JTAG調試模塊是基於別界測試的調試邏輯,支持硬體斷點、數據觸發和片外片內的調試跟蹤。Nios II標準內核設計框圖如圖2所示。

Nios CPU的所有數據、程序都是通過Avalon匯流排傳輸的,系統的FPGA片外PIO(外圍IO)包括一個串列口、顯示、鍵盤、存儲器,片內PIO採用FIFO實現。並通過使用Altera的Quartus II軟體以及SOPC builder工具可以輕鬆地將Nios II內核嵌入到系統里。

2.2 嵌入式S0PC的實現

片上系統SoC是追求產品系統最大包容的集成器件。SoC的出現使集成電路的發展成為集成系統,具有極高的綜合性,在一塊FPGA內部使用硬體編程語言,調用各種通用處理器的標準,然後模擬驗證,下載到FPGA晶元中形成一個完整的SoC系統。

圖2 Nios 1I標準內核設計框圖

SOPC技術是Altera公司提出的一種靈活、高效的片上系統SoC設計方案,其工作環境是Altera的Quartus II中的SOPC builder。與其他SoC設計相比,其優點在於可編程性,利用FPGA的可編程性進行SoC設計。通過採用SOPC builder工具,用戶可以很方便地將處理器、存儲器和其他外設聯接起來,組成一個完整的嵌入式系統。

SOPC從內部的角度來說,主要包含2個部分:圖形用戶界面(GUI)和系統生成程序。圖形用戶界面內每個組件也可以提供自己的配置圖形用戶界面,GUI創建系統PTF文件對系統進行描述;生成程序創建針對目標器件的系統HDL 描述。

在進行SOPC設計時,首先需要通過SOPC Builder選擇合適的IP核,在HDL Language選擇系統組件時選擇VHDL 或Verilog源文件。當完成設計活動之後,將由系統生成一系列設計文件,如HDL文件、DK目錄和模擬工程文件等。在Quartus II中編譯整個系統,若編譯成功,就可以把編譯文件下載到開發板上進行驗證。SOPC開發板設計流程如圖3所示。

3 基於Cyclone II器件的SOPC開發板設計實例

在實際的SOPC開發板設計中,選用Cyclone II器件的EP2C5Q208C。他是一款低成本、低功耗、高性能的FPGA,支持最低12 V輸入電壓,具有4608個可用邏輯單元,可用RAM 最多可達119808 b,13個嵌入式乘法模塊,2個提供時鐘倍頻、相移功能的鎖相環,最大可支持142個I/O腳,I/O腳支持66 MHz 32位PCI標準和高速(311 MHz)LVDS,並支持知識產權(IP)核,包含Altera MegaCore函數和AMPP mega函數。

3.1 開發板的硬體設計

開發板硬體主要包括如下幾個部分:2個同步7段共陽數碼管、8個LED、4×4鍵盤、1個8位撥位開關、1個有源時鐘輸入、1個RS 232通訊介面、PHY 100/10 M 網路介面。CF存儲卡電源插座(輸入+5 V),下載電路等。本設計的基本原理框圖如圖4所示。

3.2 開發板的軟體配置

Nios II內核具體由軟體實現,即實現了Nios II軟核化設計。Nios II軟核主要在FPGA中完成,因此,在開發板的設計中需要對其進行軟體配置電路設計。Cyclone II有3種配置電路來載入器件的配置數據:主動模式(AS),被動模式(PS),JTAG。通過MSEL[1..0]拉高與接地來選擇配置模式,MSEL [1..0]為“00”時為主動串列,“01”為被動串列。而JTAG模式優先順序最高,因此當JTAG配置開始時,其他2種模式都被迫停止。採用低成本的串列配置器件EPCS1或者EPCS4是屬於主動串列模式,在每次系統上電時自動配置Cyclone II器件。通過連接每個器件的配置允許(nCE)和配置允許輸出(nCEO)引腳可以配置多個Cyclone器件。JTAG調試口則支持在線調試(ISP)。

通過如上設計的SOPC開發板,配置上相應的外設,即形成了具有特殊處理功能的專用計算機系統。

4 結語

Nios II處理器的優點和特性使得用戶可以根據他們的需要來調整嵌入式系統的特性、性能以及成本,並使得產品快速推向市場,且易於升級改進。本文提出的基於Nios II內核的嵌入式SOPC開發板的設計給Nios II的應用提供一個有效的硬體平台,具有廣泛的實際應用價值。

[admin via 研發互助社區 ] 基於NIOS II內核的嵌入式SOPC開發板的實現已經有2316次圍觀

http://cocdig.com/docs/show-post-43136.html