1. 引言

隨著FPGA的設計速度和容量的明顯增長,當前流行的FPGA晶元都提供高速匯流排,例如DDR內存匯流排,PCI-X匯流排、SPI匯流排;針對超高速的數據傳輸,FPGA通過集成SerDes提供高速串列IO,支持各種諸如PCI-E、GBE、XAUI等高速串列匯流排協議,為各種不同標準的高速傳輸提供極大的靈活性。典型的高速FPGA器件提供的每一條物理鏈路的速度從200Mbps到高達10Gbps,高速IO的測試和驗證更成為傳統專註於FPGA內部邏輯設計的設計人員面臨的巨大挑戰。這些挑戰使設計人員非常容易會把絕大部分設計周期時間放在調試和檢驗設計上。

為了加速對於FPGA中高速并行和串列匯流排的調試和驗證,它需要使用新的高速信號完整性測試工具和分析方法。本文根據當前FPGA的高速匯流排測試和分析,提供了最新的方法和工具。

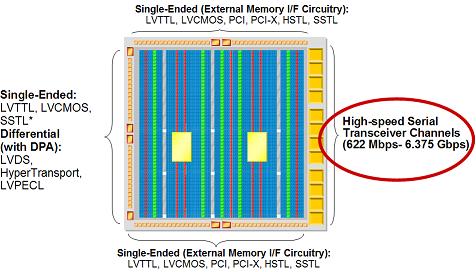

圖1是一個典型FPGA的提供的各種高速介面。對於這些速度從200M到高達10G的高速匯流排,信號完整性的測試和分析是保證設計成功的基礎和關鍵。

圖1 典型FPGA的提供的各種高速介面

2. 高速串列匯流排眼圖測試

對於採用內嵌SERDES電路的FPGA晶元,其高速串列信號進行測試和驗證,最基本的工具是通過示波器進行對其眼圖測試。因為眼圖能夠非常直觀的反映一條被測信號路徑上的整體信號質量問題,包括信號的抖動量大小(眼寬)以及幅度的大小(眼高)等重要信息。圖2是一個高速數據信號的眼圖形成的過程。

圖2 眼圖的形成過程

從眼圖的形成過程可以看出,一個NRZ編碼的高速數據無論傳輸何種碼流,都可以看作一個重複信號,經過一定時間和樣本數的累計,它反映整個傳輸鏈路上的總體信號質量。

3. 選擇合適的眼圖測試工具

3.1 示波器帶寬的要求

示波器是進行高速串列信號眼圖測試的首選工具。無論是用高速實時示波器還是採樣示波器(Sampling Scope)得到眼圖,帶寬是對示波器的基本要求。以一個NRZ編碼的高速串列匯流排為例,它理想的波形是一個方波信號,方波信號是由它的基波(正弦波)和奇次諧波(3次,5次,7次…)組成。根據信號的傳輸速率和上升時間,選擇盡量高帶寬和最快上升時間的示波器,這樣測試結果保留更多的諧波分量,構建高精度的眼圖測試結果。

示波器帶寬反映了對被測信號幅度上的衰減,而示波器上升時間決定了對被測信號上升時間測試的誤差。經典的示波器帶寬和上升時間的關係為:帶寬×上升時間=0.35-0.45,0.35-0.45為常係數。每一個高性能示波器除了提供帶寬的指標外,還會給出上升時間,表徵其對階躍信號的測試能力和精度。示波器測試結果的經驗公式為:

高速串列數據(NRZ編碼)提供一般為數據率,其最高的基頻為比特率的一半。即假設給定一個NRZ編碼的串列信號,碼型為時鐘碼型(即傳輸的數據為1-0-1-0-1),從頻域的角度觀測該信號,它成為一個基波為數據率一半的方波信號,這個時鐘碼型是數據變化最快的情況。以泰克TDS6154C 大於15GHz帶寬的實時示波器為例,它可以測試保留6.25Gb/s (2×XAUI)信號的五次諧波,以及10Gb/s (XFI)信號的三次諧波。下表列出了不同的高速串列匯流排在不同測試精度要求下對示波器帶寬的要求。

當示波器系統不能提供足夠的系統帶寬時,它會衰減對高速信號的高次諧波分量。測試結果除了引入由於示波器帶寬不足導致的碼間干擾(ISI),電壓幅度的異常(過沖和衰減),還會導致抖動量過大,最終眼圖模板測試的錯誤或者測試容限的減小,無法真正反映信號完整性問題。圖3 分別是泰克TDS6154C 15GHz帶寬和傳統DSO 13GHz帶寬實時示波器對一個FPGA器件提供的的6.25Gb/s高速數據進行的眼圖測試結果比較。圖中上半部分顯示的眼圖有很好的對稱性,上升和下降時間更快,信號抖動量很小,真實的反映信號的真實特性。

由於13GHZ的DSO示波器系統帶寬不足,無法捕獲信號的五次諧波分量,圖中下半部分的測試結果反映出眼圖上升時間過慢;同時測試的眼圖還存在明顯的過沖和震鈴,測試儀器導致的抖動也掩蓋的信號的真正抖動大小。

圖3 高速串列數據測試比較(上圖為泰克TDS6154C示波器測試結果)

3.2 示波器高速採集內存的要求

當使用實時示波器對於FPGA信號進行信號完整性測試時,利用一次採集的數據構建眼圖,所以除了示波器硬體帶寬和高速採樣率外,採集的數據量的大小非常關鍵,這樣對示波器的高速採集內存就有了更高的要求。下圖是在高採樣率下,不同高速內存容量下一次捕獲的數據量的大小。

當對FPGA的高速信號進行抖動測試時,高速內存長度不僅決定了一次抖動測試中樣本數的多少,還決定了示波器能夠測試的抖動頻率範圍。針對信號中的各種低頻抖動干擾源,高速採集內存長度是示波器進行低頻抖動測試的關鍵。下表顯示的為20GSa/s高採樣率下,不同內存長度分析抖動頻率範圍的大小。

傳統高性能示波器設計構架採用將高速採集前端(多達80顆ADC)和高速內存在物理上用一顆SOC晶元實現,由於有太多功能在一個晶元內部實現,導致片內高速內存容量的限制(在20GS/s下小於1M),無論是對於高速串列數據的眼圖測試還是對於時鐘信號的抖動測試,都存在很大的限制,並且日後無法對內存擴展升級。

為了彌補這種設計結構的缺陷,這類示波器會採用在晶元外部添加低速存儲器彌補片內高速內存的限制,但外部存儲器不能在高採樣率下工作,一般只能提供2GS/s,樣點間隔500ps,由於絕大多數信號邊沿速度都在皮秒級,2GS/s無法在信號邊沿採集足夠樣點,甚至出現會出現混疊,所以它無法提供有意義的眼圖和抖動測試結果。

泰克TDS6154C高速實時示波器採用硅鍺(SiGe)半導體集成採集前端,並使用獨立的高速存儲器,這樣就不受內存長度的限制,並且它同時支持最大採樣率和存儲長度。

[admin via 研發互助社區 ] 高速FPGA系統的信號完整性測試和分析已經有3077次圍觀

http://cocdig.com/docs/show-post-43125.html