Altera公司的Nios是基於RISC技術的通用嵌入式處理器晶元軟核,它特別為可編程邏輯進行了優化設計,也為可編程單晶元系統(SOPC)設計了一套綜合解決方案。Nios採用改進的哈佛存儲器結構,CPU帶有分離的數據和程序存儲器匯流排控制,並具備高速緩存、中斷處理功能。與其他傳統的CPU相比,Nios指令系統可通過自定義指令和標準CPU選項,利用硬體來明顯提高系統性能,而這一措施的實現對PLD中處理器軟核非常有利。Nios開發者可以在速度和面積間選擇,增加了SOPC設計的靈活性。

基於Nios設計的這一款通用編解碼器,是將多種編解碼模塊和微處理器控制部分集成到單片FPGA內部,大大減少了處理器外圍擴展電路數目、提高了系統集成度、降低了外圍電路布局走線的複雜度、提高了系統的抗干擾能力。由於FPGA的可編程性,使系統的擴展和升級更加容易,通過設置不同的技術指標,可以應用到多種通信系統中。

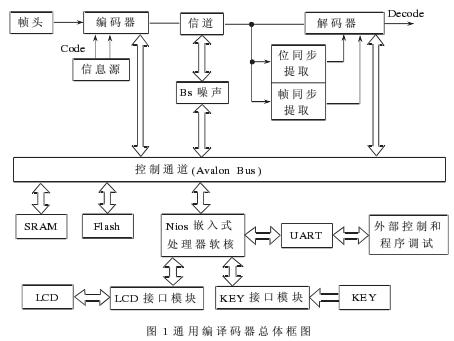

1 總體設計方案

通用編解碼器總體方案框圖如圖1所示。它由信息源、編碼器模塊、通道模擬模塊、同步提取模塊、解碼器模塊、存儲器模塊、LCD和鍵盤模塊組成,整個系統在嵌入式處理器軟核的控制下完成對各種外設的操作,包括設置編解碼類型和信碼速率、LCD顯示等。

該編解碼器可以完成卷積碼、CRC碼、RS碼等多種編解碼方案。整個系統可工作在兩種模式下:(1)調試模式。這種模式主要應用於系統調試及實驗操作。在該模式下,信息源為其他模塊提供信碼,以便調試同步提取模塊、編解碼模塊以及系統連接;通道模擬模塊處於正常工作狀態時,可向傳輸碼元中加入干擾,以檢驗解碼器是否正常工作。(2)應用模式。這種模式主要應用於實際系統。在該模式下,信息源模塊只是把用戶提供的信碼傳輸給編碼器,而通道模擬模塊並不工作,編碼模塊及解碼模塊互不連接,編碼后碼元在特定的通道中傳輸,然後再回到解碼器。

設計過程中使用的軟體平台主要有Quartus II、SOPC Builder和Nios IDE。其中,Quartus II主要用於整個系統的構建、編譯、綜合、適配、時序分析和下載。整個SOPC系統設計完成後,在Quartus II下進行管腳分配和編譯,並生成pof或sof文件下載到專用配置器件或FPGA中;SOPC Builder用於Nios微處理器和外圍模塊的集成設計,Nios微處理器系統設計完成後,通過“System Generation”產生可用於Quartus II綜合的VHDL描述,同時生成Symbol文件供調

用;Nios IDE用於Nios處理器的軟體開發、調試和下載。

2 硬體實現

硬體主要包括定製合適的CPU和外設、編解碼模塊、同步提取模塊、鍵盤顯示、存儲器模塊。

2.1位同步提取模塊設計

在數字通信中,位同步是最基本的同步。它的基本含義是接收端和發送端時鐘信號必須同頻同相,這樣接收端才能正確接收和判決發送端送來的每一個碼元。實現位同步的方法可分為外同步法和自同步法。目前,在數字通信系統中,常常採用數字鎖相法提取位同步,它屬於自同步法。

位同步提取原理圖如圖2所示。它由晶振、分頻器、相位比較器和控制器組成。其中控制器包括圖中所示的扣除門、附加門和或門。若接收碼元的速率為F(波特),則要求位同步脈衝的重複速率也為F。這時,晶振的振蕩頻率應設在NF(赫),由晶振輸出經整形得到重複頻率為NF的窄脈衝,經扣除門、或門並N次分頻后,就可得到頻率為F的信號。如果此信號不能準確反映接收碼元的頻率和相位,就要根據相位比較器輸出的誤差信號,通過控制器對分頻器進行調整。接收碼元的相位可以從基帶信號的過零點提取,將每個碼元的寬度分為兩個區:前半碼元稱為滯後區。若位同步脈衝波形落入此區,分頻器輸出脈衝,使'與門'B有輸出,經過單穩2產生一滯后脈衝。後半碼元稱為超前區,若位同步脈衝落入此區,分頻器的另一端使'與門'A有輸出,經過單穩1產生一超前脈衝。這樣無論位同步脈衝超前或滯后,都會分別送出超前或滯后脈衝對加於分頻器的脈衝進行扣除或附加,達到相位調整的目的。

圖2中的單穩3是為了保證'與門'A先有輸出,以防位同步輸出的脈衝與接收碼元的相位相差180°。對位同步提取電路進行時序模擬,得到的模擬波形如圖3所示。圖3中,codein為輸入碼流,weifen為提取出的碼元起始相位,weitongbu為位同步信號輸出。

2.2 幀同步提取模塊設計

數字通信時,一般總是以一定數目的碼元組成一個“句”進行傳輸。在本設計中,為了方便部分編碼方法的實現,採用了加幀頭的方法。因此在解碼端,相應設計了幀同步信號的提取模塊。實現幀同步的基本方法是在發送端預先規定的時隙插入一組特殊碼形的幀同步碼組,在接收端有幀同步檢測電路檢測該碼組以保證收發幀同步。

本方案中幀同步碼為7位巴克碼,即1110010,集中插入到每幀的第2~8個碼元位置上,其原理框圖如圖4所示。本模塊可分為信號源、巴克碼識別器和同步保護三部分。每幀的具體結構可以通過鍵盤設置,此處以每幀24位為例,其中后16位為信息碼元,則設置分頻器1為24分頻,分頻器2設為3分頻。巴克碼識別器由圖5所示的電路來實現。在移位時鐘信號的作用下,當7位巴克碼全部移進移位寄存器時,圖5中的D0~D6全部為1。L0~L2端為門限控制端,其中L1和L2段已設置為1,而L0由同步保護端控制,只有當D0~D6中1的個數不小於門限值時,qout端才輸出一脈衝,表示一幀的開始。

圖5中,同步保護的作用是減少假同步和漏同步。當無基帶信號輸入或有基帶信號輸出但識別器無輸出時,'與門'1關閉,'與門'2打開,單穩輸出信號通過'與門'2輸入到分頻器2,分頻器2的輸出信號使RS置0,從而關閉'與門'3,同步器無輸出信號;此時Q的反向端高電平把判決門限的電平置為7,打開'與門'1,同步器處於捕捉狀態,只要識別器輸出一個信號',與門'4就可以輸出一個置0脈衝使分頻器1置0。這樣分頻器1就可以輸出與識別器同頻同相的信號。識別器輸出信號通過'與門'1后使狀態觸發器置1,從而打開'與門'3,輸出幀同步信號,同時使判決門限降為6,關閉'或門',使同步器進入維持狀態。在維持狀態下,因為判決門限較低,故識別器的漏識別概率減小,假識別概率增加,但假識別信號與單穩輸出信號不同步,故'與門'1與'與門'4不輸出假識別信號,'與門'3輸出的仍是正確的幀同步信號。在維持狀態下,也可能出現漏識別,但由於漏識別概率比較小,只要識別器不連續出現三次漏識別,則分頻器2就不輸出一個脈衝信號,維持態不變;若超過三次,則維持態變為捕捉態,重新捕獲幀同步碼。若首次捕獲的是信息數據中與幀同步碼完全相同的碼元序列,則系統將進入錯誤的同步維持狀態。如果連續傳輸以一幀為周期的信號,此狀態將維持下去。但在實際傳輸中,連續幾幀都輸出假識別信號的概率極小,所以這種錯誤的同步維持狀態存在的時間很短。

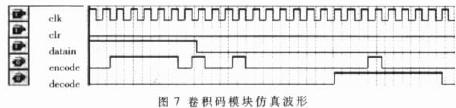

2.3編解碼模塊設計

限於篇幅,本文只簡單介紹漢明碼與卷積編碼模塊的實現。它們已很好地應用在本實驗室的通信系統實驗箱中。

2.3.1漢明碼編解碼模塊

以(7,4)漢明碼為例,校正子與錯碼位置的對應關係如表1所示。

| s1s2s3 | 錯碼位置 | s1s2s3 | 錯碼位置 |

| 001 | a0 | 101 | a4 |

| 010 | a1 | 110 | a5 |

| 100 | a2 | 111 | a6 |

| 011 | a3 | 000 | 無錯 |

3 軟體實現

軟體實現包括系統的初始化,對RAM、ROM進行操作,讀鍵盤和LCD顯示等,主要由Nios SDK shell來完成,通過串列通信口測試Nios的控制程序,控制程序用C語言來實現。

Nios開發套件提供了將程序代碼存儲在Flash存儲器的功能,GERMS監控程序在CPU啟動后自動執行程序代碼。將代碼存儲在片外存儲器有兩種方法,本文採用的方法是使用軟體程序srec2flash將.srec格式的可執行程序代碼轉換為可以寫入Nios系統Flash存儲器的.flash文件,在完成該操作的同時,srec2flash在.Flash文件的開始添加了一段代碼,用於將應用代碼從Flash複製到RAM中並運行。軟核啟動機制如圖8所示。系統上電后,串列配置器件EPCS4配置FPGA;配置完畢后複位Nios並運行片上ROM中的BootLoader;選擇運行模式;在調試模式下,BootLoader啟動GERM監控程序,為開發者提供對系統進行開發調試的條件。在控制模式下,Boot-Loader將Flash存儲的主程序裝載到RAM中,指針指向程序開始地址,開始運行主程序;初始化,並配置系統。

所選用Altera公司Cyclone系列的EP1C12Q240C8為核心的晶元,它內部包含12 060個基本邏輯單元和52個M4K RAM blocks,總共可以提供239 616bit的RAM資源,滿足了系統的需求。

本文利用可編程邏輯的靈活性和Nios的強大處理能力,將多種編解碼模塊和微處理器模塊集成到一片FPGA內部,方便地實現了通用編解碼器的設計。由於採用了VHDL語言,使系統具有可移植性和可擴展性。該設計已通過實際運行且效果良好。

[admin via 研發互助社區 ] 基於Nios的通用編解碼器的設計已經有2745次圍觀

http://cocdig.com/docs/show-post-43066.html