1 引言

目前嵌入式系統已被廣泛地應用到電子產品領域和無線通信、網路通信等高端設備領域。32 位ARM嵌入式處理器具有高性能、低功耗的特性,DSP晶元由於功能強大,加上介面方便、軟體可用資源豐富、編程方便、穩定性好、精度高等優點,應用也越來越廣泛。通常在嵌入式系統的設計中,由ARM嵌入式處理器實現整個系統的協調控制和網路功能,由DSP 晶元來執行複雜計算,因此需要實現ARM處理器和DSP 之間的數據交換。從某種程度上來說,ARM嵌入式處理器和DSP 之間數據交換的速度決定了整個系統的運行速度和性能。

2 ARM CPU CS89712 的特點

CS89712 是Cirrus Logic 公司一款基於ARM7TDMI的SOC 晶元。它一方面具有ARM 處理器的所有優點:低功耗、高性能;同時又具有非常豐富的片上資源,非常適合嵌入式產品的開發。其特點如下:

3 C55X DSP 及其EHPI 介面

3.1 C5510 DSP 的特點

以高速、低功耗為特徵的VC55X 系列DSP 採用先進的改進型哈佛結構,具有分離的數據匯流排和程序匯流排,片內集成了ROM、RAM和多個外設,如通用I/O 口、定時器、時鐘發生器、軟體可編程等待狀態發生器、可編程塊切換邏輯、串列口、直接存儲器存取控制器(DMA) 和與外部處理器通信用的主機介面(HPI) 。

3.2 C55X的增強型主機介面( EHPI)

TI 的C5510 之前的DSP 系列(C54X 系列) 中的主機介面(HPI) 主要有三種:標準8 位HPI8 介面、增強型8 位HPI8 介面和16 位HPI16 介面。其中C542~C549 內含標準型HPI8 ;C5402、C5410 內含增強型HPI8 ;C5410 以上為HPI16 ;C5409、C5416 的HPI 可以由用戶設置為增強型HPI8 或HPI16。C5510 其內部使用的是增強型主機介面,增強型比標準型更優越之處主要在於:增強型允許主機訪問DSP 內部的所有片內RAM,而標準只能訪問RAM 區中指定的2K字。

C55X為主機提供增強型的16 位并行介面( EHPI) 具有以下特點 :

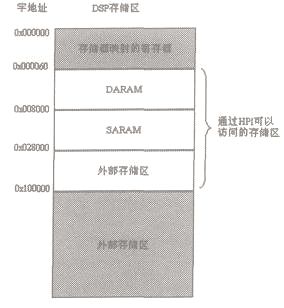

C5510 與外部主機或微處理器的連接具有單獨的16 根數據線HD0 ~ HD15、20 根地址線HA0 ~HA19 和10 根控制線。主機主動通過EHPI 口能夠直接訪問DSP 的存儲區。在圖1 所示的HPI 能訪問的地址範圍內,主機和DSP 可以通過DSP 的內部和外部存儲區來交換信息。除了對主機發中斷(通過置HPIC 寄存器的HINT 位,可以使HINT 線有效)或清除主機發來的中斷(通過清HPIC 寄存器的DSPINT標誌) 需要DSP 干涉外,C5510 幾乎不用進行其他操作。片內的DMA 通道會自動輔助完成RAM區與HPI 數據寄存器的數據傳輸。主機由HCNTL0/1 線來選擇HPI 的某個控制寄存器,如表1 所列。通過對這4 個寄存器的訪問,就可以在所設安全機制的允許範圍下讀/寫DSP 的所有或部分片內RAM。

主機由HCNTL0/1 線來選擇HPI 的某個控制寄存器。在非復用模式下,HCNTL0 決定HPI 是否訪問控制其(HPIC) 寄存器或數據寄存器(HPID) ,如表1 所示(0 —低電平,1 —高電平) ,此時HCNTL1未被使用。

| HCNTL0 | 訪問類型(非復用模式下) |

| 0 | 主機讀/寫HPI 控制寄存器- HPIC |

| 1 | 主機讀/寫HPI 數據寄存器- HPID |

圖1 通過HPI 可以訪問的DSP 存儲區圖

4 CS89712 與C5510 DSP 的介面設計

4.1 硬體連線

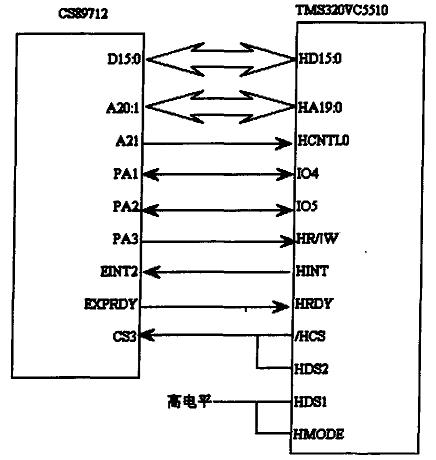

TMS320VC5510 與CS89712 連接的介面電路如圖2 所示。由圖2 可見,C5510 通過EHPI 與主機設備相連時,除了EHPI 數據匯流排及控制信號線外,不需要附加其它的邏輯電路,非常方便。

圖2 EHPI介面非復用模式下的連接圖

從EHPI 寄存器的編址方式可以看出,將HPI16介面安排在CS89712 的BANK3(即地址範圍0X03000000~0X03FFFFFF) ,而且CS89712 具有內部解碼器,直接產生片選信號CS3。

由於C55X HPI16 是一個16 位的并行埠,而C5510 的內部結構為16 位,所以在非復用模式下,只需將數據和地址匯流排分別連接即可。另外,還有幾個關鍵的控制信號需要連接。一個就是HR/W信號,由於CS89712 沒有此信號,使用埠A 的PA3 來代替。當PA3 = 1 時,代表讀操作,反之為寫操作。由於CS89712 和C5510 EHPI 介面的控制邏輯不盡相同,需要使用其它的一些信號線來進行模擬,此時要嚴格遵循EHPI 的讀寫時序。

4.2 軟體設計

在硬體連接設計好的基礎上,我們還需要通過正確的編程才能實現我們預想的時序。因為我們在ARM CS89712 上運行嵌入式操作系統uCOS-II ,所以在寫程序對HPI 介面進行讀/寫操作時將HPI 介面看作一個外部設備,將完成讀/寫操作的程序看成在uCOS-II 下面的一個字元型驅動。這樣軟體的設計就變成了在uCOS-II 下面驅動程序的開發。

考慮到CS89712 不光要將DSP 的數據取過來,而且還要將這些數據處理后再發送出去,這就需要這兩者之間有很好的配合。

CS89712 與DSP5510 之間的EHPI 介面讀/寫程序主要由兩個部分組成: 1.ARM 自身的初始化;2.HPI 介面讀寫程序。

4.2.1 ARM 處理器自身的初始化

ARM處理器首先要完成自身工作模式等一系列的初始化,才能正常進行EHPI 介面的讀/寫,源代碼如下所示。

//為了配合EHPI 口的時序,關掉MMU 頁表中bank3 的Cache

Xcount SETA 0x30000c1e

WHILE Xcount < 0x31000000

DCD Xcount

Xcount SETA Xcount + 0x00100000

WEND

rMEMCFG1 &= 0x00ffffff ; //設置與DSP 連接的nCS3 :16 位匯流排寬度、8 個隨機狀態

rMEMCFG1 | = 0x01000000 ; //3 個順序等待狀態、禁止順序訪問、禁止擴展時鐘上面這段代碼主要是對幾個寄存器進行配置。

在配置好ARM 處理器的工作模式后,對外部I/O 介面BANK3 的對應地址進行讀/寫操作,就可以完成對HPI 介面的相應操作了。

4.2.2 HPI 介面讀寫程序

以下的第一句代碼是宏定義,定義了C5510 的EHPI 介面寄存器的地址。在本設計中,已經將HPI口與外部I/O 介面的BANK3 相接,這樣HPI 口將佔用外部I/O 介面BANK3 的地址。由於是使用PA3來模擬HPI16 介面的HR/W,所以對DSP 進行讀/寫操作時, 應先將該信號置為相應的讀/寫有效狀態。

//ARM向DSP 寫數據時

#define EHPI-BASE 0x3208000

int t;

rPADDR = 0x08 ; //PA3 方向定義為輸出

rPADR = 0x00 ; //PA3 為低電平

t = *(volatile U16 *) ( EHPI-BASE + Add-offset) ;

//ARM從DSP 讀取數據時

rPADDR = 0x08 ; //PA3 方向定義為輸出

rPADR = 0x08 ; //PA3 為高電平

(volatile U16 *) ( EHPI-BASE + Add-offset) = t

5 結束語

以ARM晶元作為主控制器,用DSP 晶元進行運算,然後通過HPI 介面進行通信和交換數據的嵌入式系統設計應用模式的得到越來越廣泛的應用,而這兩者之間能夠高效、快速並且穩定的進行數據交換將是影響系統性能的關鍵部分之一。文中給出的CS89712 和C5510 之間的硬體連接方法和軟體設計經過實踐的驗證,是可行的和滿足要求的。

[admin via 研發互助社區 ] ARM CPU CS89712 與C5510 DSP 的介面設計已經有2469次圍觀

http://cocdig.com/docs/show-post-42165.html