TMS320F2812數字信號處理器是TI公司推出的32位定點DSP控制器晶元,是目前控制領域最先進的處理器之一。其頻率高達150MHz,大大提高了控制系統的控制精度和晶元處理能力。然而,DSP與外界高速通信的實現還處於正在研發階段, 國內各DSP開發版製造商對此也多處於保密狀態。鑒於將USB2.0協議應用於以DSP為核心的各類控制系統,可以大大提高DSP系統與外界的通信能力,從而拓寬DSP的應用範圍。本文給出了DSP系統與計算機的USB2.0介面方案,從而完成了DSP系統與外界的高速數據傳輸。

1 介面設計方案

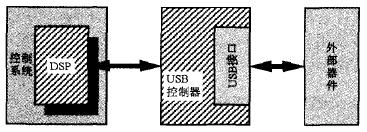

在信號處理系統上實現USB介面擴展的結構框圖如圖1所示。圖中.控制系統將處理結果通過DSP晶元傳輸給USB控制器,接著由後者驅動USB介面以將數據傳給外部器件; 另一方面,USB控制器通過USB介面接收外部器件傳來的信息,然後再把它們轉發給信號處理系統。圖1中的陰影部分表示的是DSP與USB的介面連接.是該文著重介紹的部分。

圖1 信號處理系統的USB介面擴展框圖

2 晶元介紹

在以TMS320F2812 DSP為核心的嵌入式系統中, 由於處理器的速度快(主頻可達150 MHz),處理的數據量大,使用USB1.1及其它內嵌微處理器的匯流排控制器已經不能滿足數據吞吐率的要求。因此,本介面設計選用的是Cypress公司生產的不含微控制器的USB2.0匯流排介面控制晶元CY7C68001。

CY7C68001可用來連接微處理器或DSP的DMA從裝置,該晶元內部不含微處理器,但它集成有USB2.0收發器(物理層)、USB2.0串列介面引擎SIE(鏈路層、實現底層通信協議)、4 kB的FIFO和電壓調節器、鎖相環等,CY7C68001可以支持高速(480 Mb/s)或全速(12 Mb/s)傳輸,採用3.3 V操作電壓和24 MHz外部振蕩頻率,可以選擇8位或16位匯流排方式,具有同步與非同步的FIFO介面。

CY7C68001可以向用戶提供足夠的埠、緩衝區和傳輸速度,並可提供USB2.0協議要求的全部4種傳輸方式(控制傳輸、中斷傳輸、批量傳輸和同步傳輸),可以滿足用戶對各種類型數據傳輸的需求。其片上的串列介面處理器(SIE)能完成大部分USB協議操作.使用戶可以擺脫複雜的協議細節,簡化用戶配置代碼,加快程序開發過程。但是,由於採用的是不帶MCU內核的USB介面晶元. USB的應用層協議應該由TMS320F2812編程實現.USB固件的載入必須靠DSP控制CY7C68001來完成。

3 TMS320F2812與CY7C68001的互連

該設計將CY7C68001配置在TMS320F2812的Zone0空間,並採用CY7C68001的非同步讀寫方式來完成二者之間的數據和命令交換。其介面原理電路如圖2所示。

圖2 TMS320F2812與CY7C68001的介面電路

CY7C68001除了帶有存儲器介面外.還有一個中斷信號/USBINT和4個狀態信號(READY、FLAGA、FLAGB和FLAGC)。中斷信號/USBINT佔用TMS320F2812的外部中斷/XINT1,狀態信號READY、FLAGA、FLAGB和FLAGC則可配置在本系統的狀態寄存器0(sysstat0) 中,並可由TMS320F2812查詢。本介面設計由於採用了CPLD.因而增強了系統的靈活性和可擴充性。

3.1 對CY7C68001寄存器的寫操作

通過TMS320F2812對CY7C68001的寄存器進行寫操作的上體過程如下:

3.2 對CY7C68001寄存器的讀操作

用TMS320F2812對CY7C68001的寄存器進行讀操作的具體過程如下:

4 軟體設計

USB設備開發過程中的軟體設計包括設備端的固件設計和計算機端的USB客戶驅動程序設計。由於本課題研究的重點是DSP的USB2.0介面設計.而主機驅動軟體大部分是公開的,可以直接使用Cypess公司提供的測試軟體,因此這裡不再多加討論。

4.1 固件(FirmWare)設計

由於USB2.0介面器件CY7C68001內部集成的串列介面引擎(SIE)能完成所有USB協議層功能。所以,固件任務其實就是控制CY7C68001來執行USB協議的內容並完成數據傳輸功能。其固件流程如圖3所示。

圖3 固件流程圖

4.2 匯流排枚舉

當一個USB設備接入或拔出時.主機通過枚舉過程可對設備必要的狀態改變進行鑒別和管理。枚舉過程步驟如下:

該系統軟體中的主機程序和設備固件執行到這一步就完成了枚舉過程。從設備的角度看.設備完成了配置過程,等候具體的應用。當設備被拔除時,集線器會重新發給主機一條通知信息。設備的拔除會使相應的埠處於被禁止狀態。根據接收到的設備撤除信息,主機將會更新內建的設備拓撲信息。

5 實驗說明

使用Bus Hound軟體作為調試工具可監控計算機USB匯流排Hub的數據傳輸速度。實際測試時.可使用8 K位元組作為標準測試數據。Bus Hound檢測到的時間約為640 us.有效數據的傳輸速度可達到12.5 Mbps。

6 結束語

利用此設計方案,筆者成功地實現了基於TMS320F2812的等離子切割電源控制系統和PC機等具有主USB功能的設備之間的數據通信。並將控制系統處理后的數據實時地傳輸到設備的USB埠上,然後利用U盤將所需參數傳遞給等離子切割電源控制系統,從而取得了令人滿意的效果。

[admin via 研發互助社區 ] 基於TMS320F2812的USB2.0介面的設計與實現已經有2120次圍觀

http://cocdig.com/docs/show-post-42124.html