適用於12 bit流水線ADC採樣保持電路的設計

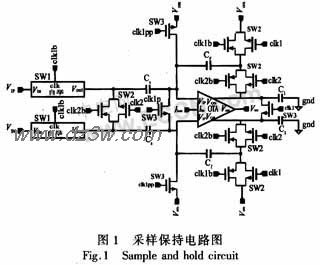

0 引言隨著CMOS技術的迅猛發展,CMOS圖像感測器以其高集成度、低功耗、低成本等優點,已廣泛用於超微型數碼相機、手機等圖像採集的領域。而流水線模數轉換器以其高速、低功耗、中高精度而被廣泛應用於圖像感測器的晶元級和列級A/D轉換器中。當前,流水線A/D轉換器比較成熟的國際水平已達到14 bit 10 MHz。國內已流片成功的大多數是10 bit流水線A/D轉換器,因此10 bit以上的高精度流水線A/D轉換器還需要進一步研究。在A/D轉換器中,採樣保持電路作為其前端最關鍵的模塊,它的性能直接決定了整個ADC的性能。本文採用一種全差分電荷轉移型結構的採樣保持電路,這種結構可以很好地消除與輸入信號無關的電荷注入和時鐘饋通;通過底極板採樣技術,消除與輸入信號相關的電荷注入和時鐘饋通;使用柵壓自舉電路來消除開關的非線性。同時採用摺疊式增益增強運算放大器,減小由於有限增益和不完全建立帶來的誤差。該採樣保持電路在5 V電源電壓,20 MS/s採樣頻率下,在輸入信號為奈奎斯特頻率時,無雜散動態範圍(SFDR)為76 dB,採樣精度達到0.012%,滿足12 bit精度要求。1採樣保持電路圖1為本文設計的採樣保持電路結構,該結構稱為電荷轉移型採樣保持電路。

它的工作時序如圖2所示,clk1和clk2是兩相不交疊時鐘,控制採樣保持電路分別工作於採樣相和保持相;clkb為clkl的反相。當clk1為高電平時,電路進入採樣相,運放兩個輸入端被短路,輸入信號存儲在採樣電容Cs上;clk2為高電平時,電路進入保持相,將差分電荷轉移到反饋電容Cf上。

在從採樣相向保持相轉變的過程中,clklpp,clklp,clkl依次關斷,實現了底極板採樣,以減少開關時鐘饋通和溝道電荷注入的影響;且只有差分電荷轉移到反饋電容Cf上,共模電荷一直保存在採樣電容Cs上。因此,這種結構可以處理共模範圍較大的輸入信號。2採樣電容、開關的選取和設計2.1採樣電容的選取在採樣保持電路中,採樣電容的取值對電路的性能有直接的影響。採樣電容越小,熱雜訊就大,因為熱雜訊主要由電路中的開關導通電阻產生,其方差是開關電容值的函數(σ2thermal≈kT/C,其中k為波爾茲曼常量,T為絕對溫度),則電路的信噪比(SNR)就降低。如果採樣電容較大,會使電路的功耗增大,速度變慢,而此時信噪比主要受量化雜訊的限制,沒有明顯改善。因此在設計時,把雜訊限制在一定範圍之內,得到電容的最小值,再犧牲一些功耗和速度,取稍大電容值即可。本文所設計的ADC具有12 bit解析度,量化範圍為±1 V。如果要求由熱雜訊與量化雜訊所引起的SNR最多能下降1 dB,即需滿足:kT/Cs<△2/46.3,△為1 LSB對應的幅度。根據上式算出,採樣電容Cs>0.8 pF,取Cs=Cf=1 pF。4性能模擬和晶元版圖本電路採用CSMC公司的0.5μm CMOS工藝庫,應用Spectre對運算放大器和採樣保持電路進行模擬驗證,表1為典型條件下(TT(工藝角),27℃)運算放大器的性能參數。從表中可以看出,運算放大器的性能滿足採樣保持電路要求。表中:V為電源電壓;CF為負載電容;G為直流增益;GBW為單位增益帶寬;ϕ為相位裕度;Pdiss抵為功耗。

在採樣保持電路的輸入端加差分電壓1 V,時鐘頻率為20 MHz,模擬結果表明輸出電壓達到LSB/2(0.012%)精度內所需要的時間為14 ns,完全滿足12 bit的精度要求。圖6是在採樣頻率為20 MHz下,對由輸入信號為Nyquist頻率(9.819 3 MHz),Vp-p=2 V的正弦信號,所得到的輸出信號頻譜圖。從圖中可以看出電路的SFDR為76 dB,完全滿足系統要求。

圖7為運算放大器的版圖,面積為288μm×128 μm(包括主電路、輔助放大器、偏置和共模反饋電路)。該運算放大器作為一個核心模塊已流片測試。測試結果表明該放大器性能與模擬值相近,功能正確,可用於該採樣保持電路中。

5 結論本文設計了一個可用於12 bit,20 MS/s流水線ADC中的採樣/保持電路。該電路使用CSMC公司的0.5μm CMOS工藝庫,在20 MS/s採樣頻率下,當輸入信號的頻率為9.8193 MHz時,SFDR為76 dB,精度達0.012%,完全滿足12 bit要求。本文運用增益增強型摺疊式運算放大器,以獲得較高的增益和帶寬。同時採用柵壓自舉開關,並通過對電路中的開關組合優化,極大的提高了電路的線性性能;採用全差分結構、底極板採樣來消除電荷注入和時鐘饋通。該採樣保持電路能夠直接應用於高速高精度模/數轉換器等各種高速模擬系統中。2.2 採樣開關的設計2.2.1 開關類型的選取在採樣保持電路中,開關的性能對電路有著非常重要的影響。因此對於圖1中的開關作了詳細設計。在電路設計時,考慮到性能和功耗的優化,在對性能沒有明顯影響時,儘可能採用簡單電路,否則以性能為主。圖1中SW2和SW3處的開關主要用於連接到共模參考電壓,短接輸入端,短接輸出端,對其性能要求不是很高,故採用簡單的NMOS開關和CMOS互補型開關。在SWl處由於採樣開關線性度對電路採樣相的線性性能影響最大,如果用一個簡單的NMOS開關,當輸入信號電壓變化時,其導通電阻也隨之變化,這在實際工作中會引起較大的誤差。而CMOS開關其導通電阻雖有所減小,但隨輸入信號的變化,其柵-源電壓會隨之改變,因此信號仍有失真,所以本文採用了一種線性度更好的柵壓自舉開關。2.2.2 開關參數設計由於小尺寸的開關會帶來大的導通電阻,嚴重影響電路的速度,而大尺寸的開關則會引入非常大的饋通電容,對前級造成明顯的影響。在本電路中,NMOS開關的W/L為12/1時模擬性能最好;對於CMOS互補型開關,其導通電阻的線性度受p管和n管的寬長比比例影響。所以要對管子的寬長比進行優化。經過模擬發現,在本電路中,當PMOS和NMOS的寬度比為2.8/1時,導通電阻Ron在整個工作範圍內變化最小,線性度最好。柵壓自舉開關的電路結構如圖3所示。它由時鐘倍增電路、傳輸管和柵-源電壓控制電路組成。由於傳輸管M1的柵-源電壓Vgs恆定為VDD,因此自舉開關的導通電阻Ron較小,且基本恆定,線性度較好。圖4為輸入正弦信號時,開關傳輸管M1的Vgs模擬波形,從圖中可以看出,其Vgs基本不變,由於受M1柵上的寄生電容的影響,柵源電壓略小於VDD。

3 運算放大器(OTA)的設計OTA是採樣保持電路的核心,它決定了該採樣保持電路的精度和建立時間。由於該採樣保持電路運用於12 bit 20 MHz流水線ADC,則要求該放大器的輸出在25 ns的建立時間內穩定在最終值0.012%。如果將OTA設為單極點放大器,則可估算出OTA的直流增益最好能達到84 dB以上,單位增益帶寬必須大於72 MHz。為了能達到較好的性能,一般都留有一定的余量,因此實際上設計中要比這些值大很多。考慮到普通一級運放的增益不夠高;兩級運放則速度上又達不到,故本文採用增益增強的摺疊式共源共柵運放。本文採用的放大器為如圖5所示的帶有A1和A2兩個輔助放大器的增益增強型摺疊式共源共柵放大器。從工程設計角度考慮,採用統一模塊化可簡化設計過程,減少設計出錯的可能性。因此輔助放大器也採用摺疊式共源共柵結構,所有偏置電壓都由一個偏置電路產生,並取偏置電流為主運放的1/10,以減小功耗。其中,Al以NMOS管作為輸入端,A2以PMOS管作為輸入端。考慮到這兩個運放的直流輸出是為主運放的M7,M8,M9,M10提供直流偏置,不需要大範圍的波動,因此採用一種簡單實用的共模反饋。另外,輔助放大器的單位增益帶寬至少與主放大器的帶寬相等,稍大則穩定時間會更短一些,因此可在其輸出端接電容來調節帶寬,將其控制在主運放第二極點內的合適位置。主運放則採用連續時間型共模反饋。

[admin via 研發互助社區 ] 適用於12 bit流水線ADC採樣保持電路的設計已經有4854次圍觀

http://cocdig.com/docs/show-post-29403.html