一、儀用放大器的介紹:

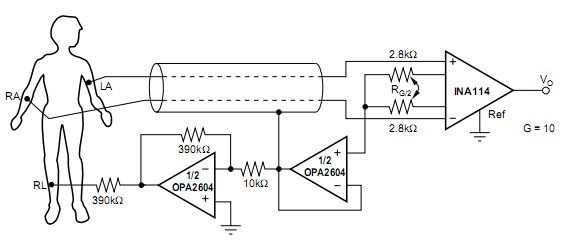

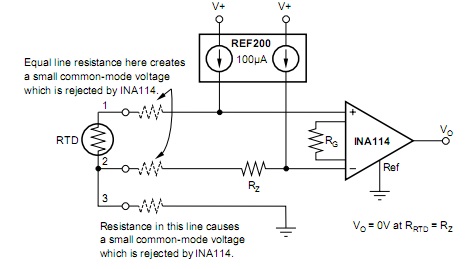

儀用放大器與很多放大電路一樣,都是用來放大信號的用的,但儀用放大電路的特點是,它所測量的信號通常都是在雜訊環境下的微小信號。而雜訊通常都是公共模雜訊,所以在電路設計要求上,電路有很高的共模抑制比,利用共模抑制比將信號從雜訊中分離出來。因此好的儀用放大器測量的信號能達到很高的精度,在醫用設備、數據採集、檢測和控制電子設備等方面都得到了廣泛的應用。例:

在這些應用中,信號源的輸出阻抗常常達幾kΩ或更大,因此,儀錶放大器的輸入阻抗非常大——通常達數GΩ,它工作在DC到約1 MHz之間。在更高頻率處,輸入容抗的問題比輸入阻抗更大。高速應用通常採用差分放大器,差分放大器速度更快,但輸入阻抗要低。

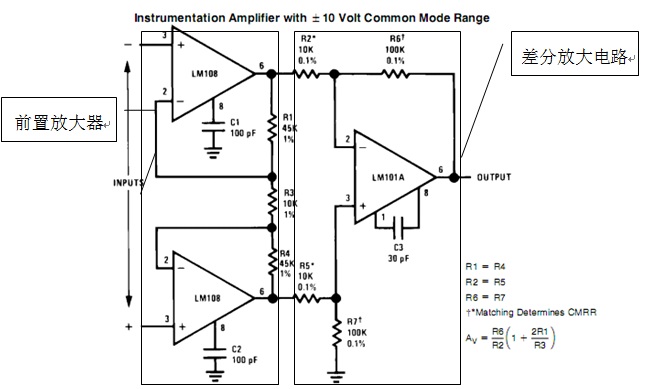

二、儀用放大器的基本電路:

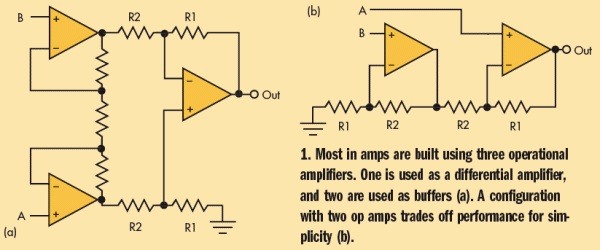

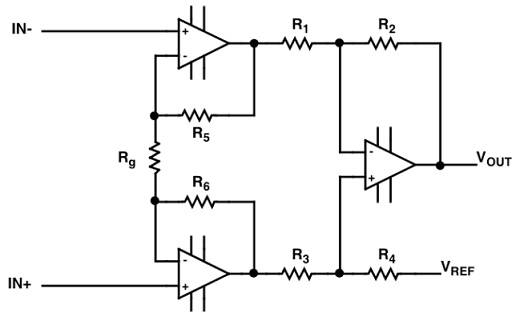

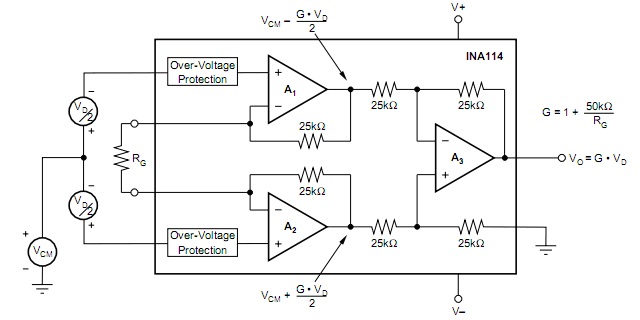

大多數儀用放大器採用3個運算放大器排成兩級:一個由兩運放組成的前置放大器,後面跟一個差分放大器。前置放大器提供高輸入阻抗、低雜訊和增益。差分放大器抑制共模雜訊,還能在需要時提供一定的附加增益。如下圖:

三運放方案是儀錶放大器採用的惟一結構嗎?

可以採用具有兩個運放的較少元器件的結構替代,但有兩個缺點(圖 1b)。首先,不對稱的結構使CMRR較低,特別是高頻時。其次,可用於第一級的增益量有限。輸出級誤差則反饋回輸入端,導致相對入的雜訊和補償誤差更大。

也有單運放組成的儀用放大器,在最基本的拓撲結構中,一個儀用放大器可由一個單一的運算放大器,見附錄.

三、儀用放大器的信號放大原理:

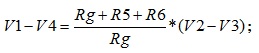

現所設計的儀用放大器是三運放結構,如上圖。它是由運放A1,A2按通向輸入接法組成第一級查分放大電路,運放A3組成第二級差分放大電路。在第一級電路中,Vi1,Vi2分別加到A1和A2的同向端,Rg和R5、R6組成的反饋網路,引入了負反饋。由A1、A2虛短可得

Vi1=V2;Vi2=V3; 3.1

又由A1、A2虛斷可得 3.2

3.2

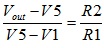

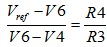

又由A3虛斷可得 ;整理得

;整理得  3.3

3.3  ;整理得

;整理得  3.4

3.4

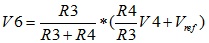

由A3虛短可得

V5=V6; 3.5

則由3.3式、3.4式和3.5式可得

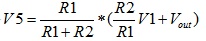

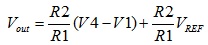

整理后可得 3.6

3.6

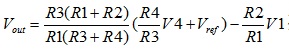

在上式中,如果我們選取電阻滿足 的關係,則輸出電壓可化簡為

的關係,則輸出電壓可化簡為 3.7

3.7

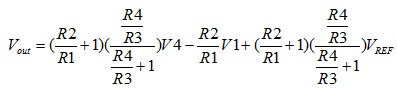

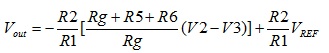

根據式3.2和3.7我們可以得到 3.8

3.8

而我們為了是電路對稱,提高儀用放大器性能,我們選取電阻應滿足R5=R6的關係,且VREF通常接地,當我們對儀用放大器進行電路調零時,我們才會將VREF賦予一定電壓(這在後面進行電路調零時會具體講到),最終我們會得到輸出電壓的關係式為 3.9

3.9

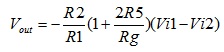

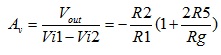

電壓增益則為 3.10

3.10

從該式中我們可直觀的看到,我們可以根據選取R2/R1 和R5/Rg 電阻的比例關係,來達到不同的信號放大比例要求。所以電阻的選取也是儀用放大器設計最重要的環節之一。很多儀用放大器晶元,考慮到電路的穩定和安全,一般都固定R1~R6的阻值,只將Rg設置成可調(在後面會有相應說明)。

在前面我們提到過儀用放大器有很高的共模增益,現在我們根據下面的例子來說明其對共模的抑制作用。

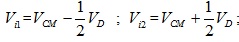

根據上面的圖片可知在輸入端

根據圖所示,最後得 Vo=G•VD

再此Vcm 即為共模信號,而VD 即為差摸信號,而雜訊大多都是共模信號,經過該電路據可以被抑制而濾出我們所要的信號。

[admin via 研發互助社區 ] 儀用放大器的設計和應用已經有3639次圍觀

http://cocdig.com/docs/show-post-44616.html