In SigXplorer, Buffer Delays Specifies how the simulator obtains buffer delays for the simulation. We can select one of the following options from the drop-down list:

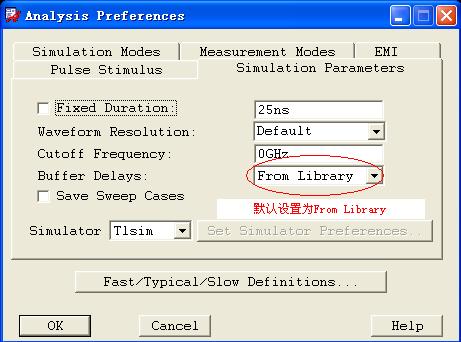

圖1 Buffer Delay默認模式為From Library

那麼,在時序模擬過程中,究竟該怎樣設置這項參數?這兩種模式有什麼區別和聯繫呢?讓我們看看下面的模擬實例。

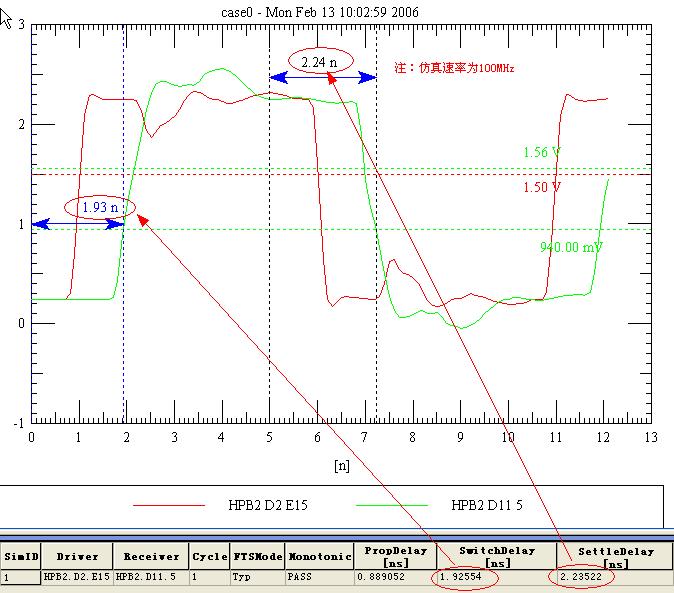

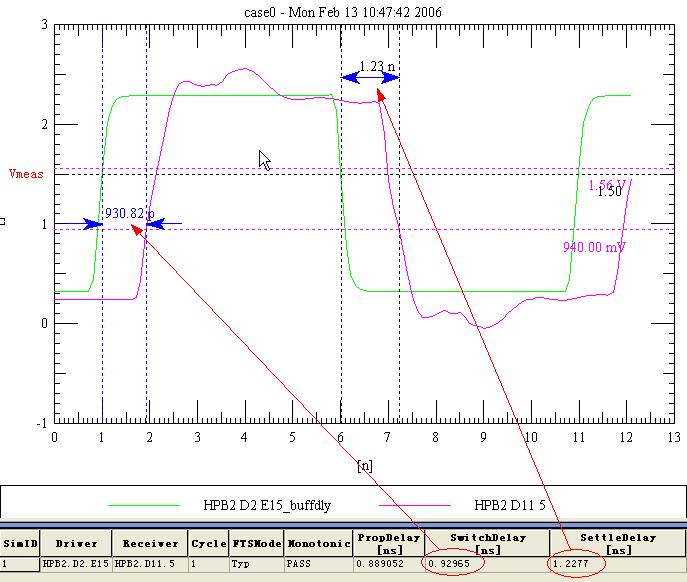

圖2和圖3分別顯示了Buffer Delay模式設為From Library和On-the-fly時Switch Delay和Settle Delay的模擬數值。以Switch Delay為例,從這兩個模擬圖中可以看出二者的數值相差很大,差值為ns級別。通過觀察模擬波形及模擬結果,可看出在From Library模式下,Switch Delay是從驅動器件輸出Buffer上電開始測量的;而在On-the-fly模式下,是從驅動器件輸出Buffer電壓上升到Vmeas開始測量的。後者與我們所熟悉的常規定義相同,我們的時序公式也是基於此種定義推導的。所以在做時序模擬時應該選擇On-the-fly模式。

如果我們將From Library模式下的First Switch Delay和Final Settle Delay分別記為Tswtich_lib和Tsettle_lib,On-the-fly模式下的First Switch Delay和Final Settle Delay分別記為Tswtich_fly和Tsettle_fly,則有Tswtich_lib = Tswtich_fly + Buffer Delay,Tsettle_fly = Tsettle_fly + Buffer Delay。即From Library模式下Switch Delay實際為On-the-fly模式下的Switch Delay + Buffer Delay。

圖2 From Library模式下的Switch Delay和Settle Delay值

圖3 On-the-fly模式下的Switch Delay和Settle Delay值

我們再來看看時序模擬過程中,Buffer Delays選擇From Library模式會出現什麼問題。

對於源同步來說,其理論時序計算公式如下:

Tflight_time_min > Thold-Tva_min +Tflt_clk@fast + Design Margin Fast 式(1-1)

Tflight_time_max < Tvb_min - Tsetup + Tflt_clk@slow -Tjitter - Design Margin Slow 式(1-2)

由前面推導知道,From Library模式下Switch Delay實際為On-the-fly模式下Switch Delay + Buffer Delay。以式(1-1)為例,From Library模式下,則其變化為:

Tflight_time_min + Tbuffer_delay > Thold-Tva_min +Tflt_clk@fast + Tbuffer_delay_clk + Design Margin Fast

可寫為:

Tflight_time_min > Thold-Tva_min +Tflt_clk@fast + ( Tbuffer_delay_clk - Tbuffer_delay ) + Design Margin Fast

由上式得出,如果參考時鐘和待模擬信號的輸出Buffer模型相同,則它們的Buffer Delays相同,從而Tbuffer_delay_clk - Tbuffer_delay 為零,選擇From Library模式對公式並沒有影響,所計算結果也是正確的。所以對源同步來說,只要參考時鐘和待模擬信號的模型相同,設置Buffer Delays為On-the-fly和From Library模式沒有區別。但是如果參考時鐘和待模擬信號的輸出Buffer模型不同,則Tbuffer_delay和Tbuffer_delay_clk不同,這時所計算出的Tflight_time_min就有了誤差,誤差值為兩個Buffer Delay之差值,可能為正也可能為負。雖然這個誤差值不是很大,但是對於時序要求嚴格的網路還是會產生一定的影響。

對於共同時鐘同步來說,由於其時鐘由外部時鐘提供,所以一般情況下公式兩邊的Buffer Delay值不會相同,因此選擇From Library也會產生誤差。

Tflight_time_min > Thold - Tcomin+Tflt_clk@fast(p_in_sd) + Tskew + Design Margin Fast 式(1-3)

Tflight_time_max < Clock Cycle Time - Tsetup - Tco max + Tflt_clk@slow(p_in_sd) - Tjitter - Tskew - Design Margin Slow 式(1-4)

終上所述,在做時序模擬時,應該注意選擇Buffer Delays為On-the-fly模式。From Library模式只有在少數情況下可以應用。

[admin via 研發互助社區 ] SigXplorer中兩種Buffer Delays 模式詳解已經有3378次圍觀

http://cocdig.com/docs/show-post-44234.html