Nios II處理器可以方便的使用DRAM,從而獲得大容量的內存。這比較起許多單片機,實在是一個非常方便的地方。在這裡,我粗略的介紹一下Nios II中DRAM的使用。如果本文能對您有一點點幫助,我都會感到非常高興。

我只挑要點講一下,關於DRAM的詳細使用指南,請您參考Altera提供的隨機help文檔。

1、準備工作:

- 關於創建並使用NiosII系統,請參考我之前寫的文章“Step By Step創建標準(Standard) Nios II系統”。

- 開發板上至少要有一片DRAM。

2、使用DRAM:

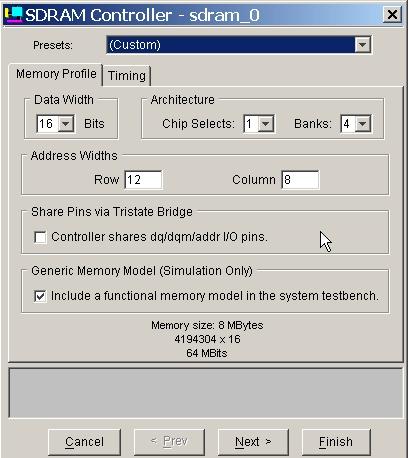

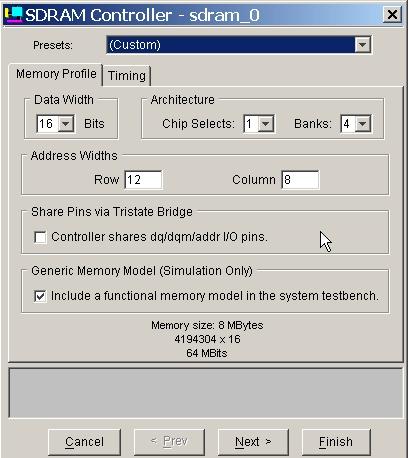

1)在sopc_builder中,雙擊MEMORY下的SDRAM Controller,可以創建SDRAM 控制器。

Data Width:數據位寬,ezNiosDK的用戶請選擇 16 Bits。

Chip Selects:晶元的片選信號,ezNiosDK的用戶請選擇 1。

Banks:設定DRAM晶元的Bank數目。ezNiosDK的用戶請選擇 4。

Row : 設定行地址線的數量。ezNiosDK的用戶請選擇 12。

Column : 設定列地址線的數量。ezNiosDK的用戶請選擇 8。

其餘的請按照上圖中設置。

2)設定DRAM的時序參數

- CAS latency cycles:在CAS發出之後,仍要經過一定的時間才能有數據輸出,從CAS與讀取命令發出到第一筆數據輸出的這段時間,被定義為CL(CAS Latency,CAS潛伏期)。由於CL只在讀取時出現,所以CL又被稱為讀取潛伏期(RL,Read Latency)。CL的單位一般為時鐘周期數,具體耗時由時鐘頻率決定。ezNiosDK的用戶可以選擇2。

- Initialization refresh cycles:初始化過程中所需的刷新周期,ezNiosDK的用戶可以選擇 2。

- Isssue one refresh command every:刷新周期。ezNiosDK的用戶可以選擇 15.625 us。

DRAM之所以稱為DRAM,就是因為它要不斷進行刷新(Refresh)才能保留住數據,因此它是DRAM最重要的操作之一。刷新操作一般是用S-AMP先讀再寫。那麼要隔多長時間重複一次刷新呢?目前公認的標準是,存儲體中電容的數據有效保存期上限是64ms(毫秒,1/1000秒),也就是說每一行刷新的循環周期是64ms。這樣刷新速度就是:行數量/64ms。我們在看內存規格時,經常會看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的標識,這裡的4096與8192就代表這個晶元中每個L-Bank的行數。刷新命令一次對一行有效,發送間隔也是隨總行數而變化,4096行時為15.625μs(微秒,1/1000毫秒),8192行時就為7.8125μs。

刷新操作分為兩種:自動刷新(Auto Refresh,簡稱AR)與自刷新(Self Refresh,簡稱SR)。不論是何種刷新方式,都不需要外部提供行地址信息,因為這是一個內部的自動操作。對於AR, SDRAM內部有一個行地址生成器(也稱刷新計數器)用來自動的依次生成行地址。由於刷新是針對一行中的所有存儲體進行,所以無需列定址,或者說CAS在 RAS之前有效。所以,AR又稱CBR(CAS Before RAS,列提前於行定位)式刷新。由於刷新涉及到所有L-Bank,因此在刷新過程中,所有L-Bank都停止工作,而每次刷新所佔用的時間為9個時鐘周期(PC133標準),之後就可進入正常的工作狀態,也就是說在這9 個時鐘期間內,所有工作指令只能等待而無法執行。64ms之後則再次對同一行進行刷新,如此周而復始進行循環刷新。顯然,刷新操作肯定會對SDRAM的性能造成影響,但這是沒辦法的事情,也是DRAM相對於SRAM(靜態內存,無需刷新仍能保留數據)取得成本優勢的同時所付出的代價。

SR則主要用於休眠模式低功耗狀態下的數據保存,此時不再依靠系統時鐘工作,而是根據內部的時鐘進行刷新操作。在SR期間除了CKE之外的所有外部信號都是無效的(無需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式並進入正常操作狀態。 - Delay after powerup,before initialization:上電后的穩定期。手冊上一般給出的是200us,通常我們選擇 100us即可。

- Duration of refresh command:刷新周期。一般是60或者70ns.ezNiosDK的用戶可以選擇 70ns。

- Duration of prechange command:預充電周期。在發出預充電命令之後,要經過一段時間才能允許發送RAS行有效命令打開新的工作行,這個間隔被稱為tRP (Precharge command Period,預充電有效周期)。tRP的單位一般也是時鐘周期數,具體值視時鐘頻率而定。ezNiosDK的用戶可以選擇 20ns。

實際上,預充電是一種對工作行中所有存儲體進行數據重寫,並對行地址進行複位,同時釋放晶元內部的比較器(重新加入比較電壓,一般是電容電壓的1/2,以幫助判斷讀取數據的邏輯電平),以準備新行的工作。具體而言,就是將放大/驅動比較器中的數據回寫。存儲單元中的電容容量很小,即使是沒有工作過的存儲體也會因行選通而使存儲電容受到干擾,所以也需要進行讀後重寫。 - ACTIVE to READ or WRITE delay:ezNiosDK的用戶可以選擇 20ns。

在發送列讀寫命令時必須要與行有效命令有一個間隔,這個間隔被定義為tRCD,即RAS to CAS Delay(RAS至CAS延遲),也可以理解為行選通周期,這應該是根據晶元存儲陣列電子元件響應時間(從一種狀態到另一種狀態變化的過程)所制定的延遲。tRCD是SDRAM的一個重要時序參數。廣義的tRCD以時鐘周期(tCK,Clock Time)數為單位,比如tRCD=2,就代表延遲周期為兩個時鐘周期,具體到確切的時間,則要根據時鐘頻率而定,對於運行在100M的SDRAM, tRCD=2,代表20ns的延遲,對於PC133則為15ns。 - Access time: 訪問時間。ezNiosDK的用戶可以選擇 5.4ns

從數據I/O匯流排上有數據輸出之前的一個時鐘上升沿開始,數據即已傳向讀出放大器,也就是說此時數據已經被觸發,經過一定的驅動時間最終傳向數據I/O匯流排進行輸出,這段時間我們稱之為tAC(Access Time from CLK,時鐘觸發后的訪問時間)。tAC的單位是ns,對於不同的頻率各有不同的明確規定,但必須要小於一個時鐘周期,否則會因訪問時過長而使效率降低。比如PC133的時鐘周期為7.5ns,tAC則是5.4ns。需要強調的是,每個數據在讀取時都有tAC,包括在連續讀取中,只是在進行第一個數據傳輸的同時就開始了第二個數據的tAC。 - Write recover time:回寫延遲。ezNiosDK的用戶可以選擇 14ns

寫操作雖然是0延遲進行,但每筆數據的真正寫入則需要一個足夠的周期來保證,這段時間就是寫回周期(tWR)。所以預充電不能與寫操作同時進行,必須要在tWR之後才能發出預充電命令,以確保數據的可靠寫入,否則重寫的數據可能是錯的,這就造成了寫回延遲。

3、在Nios IDE中使用DRAM:

在Nios IDE中使用DRAM非常簡單。DRAM可以用作Program memory 或者 Read-only data memory 或者 Read/write data memory,如下圖範例中,在system library properties中,設置Program memory,Read-only data memory , Read/write data memory,均為DRAM的名字:sdram_0 。這樣把所有的數據都放在DRAM中。