摘要:介紹一種以FPGA(Field Programmable Gate Array)為核心,基於硬體描述語言VHDL的數字頻率計設計與實現。在介紹頻率測量的原理和測量方法的基礎上,針對所設計的頻率計需簡單易用的要求,採用FPGA和簡單的外圍電路使系統具有體積小、可靠性高、靈活性強及價格低廉等特點,同時還具有易於升級的特點。

在電子工程,資源勘探,儀器儀錶等相關應用中,頻率計是工程技術人員必不可少的測量工具。頻率測量也是電子測量技術中最基本最常見的測量之一。不少物理量的測量,如轉速、振動頻率等的測量都涉及到或可以轉化為頻率的測量。目前,市場上有各種多功能、高精度、高頻率的數字頻率計,但價格不菲。為適應實際工作的需要,本文在簡述頻率測量的基本原理和方法的基礎上,提供一種基於FPGA的數字頻率計的設計和實現過程,本方案不但切實可行,而且具有成本低廉、小巧輕便、便於攜帶等特點。

1 數字頻率測量原理和方法及本系統硬體框架

數字頻率計是直接用十進位數字來顯示被測信號頻率的一種測量裝置。它不僅可以測量正弦波、方波、三角波和尖脈衝信號的頻率。而且還可以測量它們的周期。數字頻率計在測量其他物理量如轉速、振動頻率等方面也獲得廣泛應用。

1.1 數字頻率的測頻原理和方法

眾所周知,所謂“頻率”就是周期性信號在單位時間(1s)內變化的次數。若在一定時間間隔T內測得這個周期性信號的重複變化次數N,則其頻率可衰示為f=N/T 。

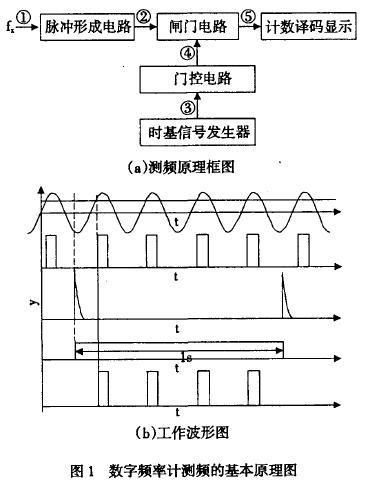

數字頻率計測頻率的原理框圖可示如圖1(a)。其中脈衝形成電路的作用是:將被測信號變成脈衝信號,其重複頻率等於被測頻率fx。時間基準信號發生器提供標準的時間脈衝信號、若其周期為1s。則門控電路的輸出信號持續時間亦準確地等於1s。閘門電路由標準秒信號進行控制,當秒信號來到時,閘門開通.被測脈衝信號通過閘門送到計數解碼顯示電路。秒信號結束時閘門關閉,計數器停止計數,各點的波形如圖1(b)所示。由於計數器計得的脈衝數N是在1秒時間內的累計數 所以被測頻率fx=NHz。

目前,有三種常用的數字頻率測量方法:直接測量法(以下稱M法)、周期測量法(以下稱T法)和綜合測量法(以下稱M/T法)。M法是在給定的閘門時間內測量被測信號的脈衝個數,進行換算得出被測信號的頻率。T法是通過測量被測信號一個周期時間計時信號的脈衝個數,然後換算出被測信號的頻率。這兩種測量法的精度都與被測信號有關,因而它們屬於非等精度測量法。而M/T法設實際閘門時間為t,被測信號周期數為Nx,則它通過測量被測信號數個周期的時間,然後換算得出被測信號的頻率,克服了測量精度對被測信號的依賴性。M/T法的核心思想是通過閘門信號與被測信號同步,將閘門時間t控制為被測信號周期長度的整數倍。測量時,先打開預置閘門,當檢測到被測閘門關閉時,標準信號並不立即停止計數,而是等檢測到的被測信號脈衝到達是才停止,完成被測信號的整數個周期的測量。測量的實際閘門時間與預置閘門時間可能不完全相同,但最大差值不超過被測信號的一個周期。

1.2 系統的硬體框架設計

本系統由脈衝輸入電路、整形電路、核心控制電路(由FPGA構成)和輸出顯示電路組成,如圖2所示。

圖2 系統框圖

控制的核心晶元是FPGA,它由兩大功能模塊組成:(1)頻率計數模塊,包含兩個部分,選通時間控制部分,可改變選通時間;計數部分,根據選通時間的長短對被測信號正脈衝進行計數;(2)掃描顯示模塊,對計數的結果進行掃描顯示,從而完成整個測頻率的過程。外圍的電路相對簡單,只有信號輸入整形電路和數碼管顯示電路。

系統的工作原理是,被測信號經整形生成矩形波輸入到控制核心晶元FPGA的計數模塊,計數模塊根據所提供的矩形波上升沿計數,計數時間則由選通時間控制部分決定,根據頻率所處的範圍來決定檔位;將計數的結果給顯示電路,通過掃描,在數碼管上顯示頻率的大小。

整形電路是將待測信號整形變成計數器所要求的脈衝信號。電路形式採用由555定時器所構成的施密特觸發器。若待測信號為正弦波,輸入整形電路,設置分析為瞬態分析,啟動電路,其輸入、輸出波形如圖1(b)所示。由圖可見輸出為方波,二者頻率相同,頻率計測得方波的頻率即為正弦波的頻率。

2 基於FPGA的系統設計

2.1 EDA技術和VHDL語言的特點

EDA(電子設計自動化)代表了當今電子設計技術的最新發展方向,它的基本特徵是:設計人員按照“自頂向下”(Top Down)的設計方法,對整個系統進行方案設計和功能劃分,系統的關鍵電路用一片或幾片專用集成電路(ASIC)實現,然後採用硬體描述語言(HDL)完成系統行為級設計,最後通過綜合器和適配器生成最終目標器件。FPGA可以通過軟體編程對目標器件的結構和工作方式進行重構,能隨時對設計進行調整,具有集成度高、結構靈活、開發周期短、快速可靠性高等特點,數字設計在其中快速發展,應用這種技術可使設計過程大大簡化。VHDL語言最大的特點是描述能力極強,可以覆蓋邏輯設計的諸多領域和層次,並支持眾多的硬體模型。其特點包括:

(1)設計技術齊全,方法靈活,支持廣泛;

(2)系統硬體描述能力強;

(3)VHDL語言可以與工藝無關地進行編程;

(g)VHDL語言標準、規範,易於共享和重用。

2.2 系統設計

設計採用實驗教學中常用的altera公司的FLEX10K10系列晶元,該晶元的反應時間可達ns級,頻率計的測頻範圍可為1Hz~999MHz。系統在兼顧測量精度和測量反應時間的基礎上,實現了量程的自動轉換,測量可以全自動地進行。其控制和邏輯電路是基於quartus II和VHDL語言進行設計,外部電路相當簡單。圖3是本設計的頂層示意圖。設計主要由分頻模塊、控制模塊、鎖存模塊等共七個模塊組成。脈衝信號由fsin引腳輸入到cntrl模塊,由clr引腳和fdiv輸出信號q共同決定fsin的有效性,並由cntd實現自適應控制,當fsin的頻率高出或低於某個量程,cntrl模塊會根據具體的值選擇相應合適的量程(本設計共有分為1~9999Hz、10~99.99kHz、100~999.9kHz、1M~999M等四個量程)。再經由lock鎖存之後,由dspnum選擇具體的通路,由dspsel和disp實現動態掃描顯示,掃描顯示模塊有dspsel控制七段數碼管的片選信號,間鎖存保存的BCD碼數據動態掃描解碼,以十進位形式顯示。以上的各功能模塊都是在FLEX10K10中,用VHDL予以實現的,較之以往的傳統型電路更為簡單,更易於實現頻率計的小型化、微型化甚至晶元化設計。

頂層示意圖中的各模塊用VHDL語言生成后,再生成圖3所示的示意圖,經編譯鏈接之後就可以下載到系統中。再在外部擴展信號採集和相應的數碼顯示電路,就可以完成一個相對簡單的數字頻率計。圖4是系統的整體框圖。

信號從被測信號輸入處輸入到波形整形電路后,經過FPGA演算法處理,再由數字顯示部分輸出。在數字顯示部分根據不同的檔位,可以把相應的單位加入即可,人一檔時單位為Hz,二檔時為kHz,其餘類推。

此外,在硬體電路設計時,應注意FPGA的介面部分,包括電平轉換、標準CPU介面等等。比如FPGA器件的I/O電壓不能達到TTL電平,則需要添加必要的電平轉換晶元,即通常指的Transceiver。又如,驅動LED等功能的需要是經常遇到的,但FPGA器件的驅動能力不一定能夠滿足需要,因此提供驅動能力也是設計時需要考慮的問題之一。同時,時鐘設計是FPGA設計的核心問題之一,時鐘系統的不穩定和不合理,往往不能發揮器件的全部功能和潛力,嚴重時還會導致系統失敗。對於多時鐘、多速率系統,如何做到全局同步設計、保證時延特性、達到設計速率等,對系統成功都是極為關鍵的。

3 結束語

本文在介紹了頻率計的基本原理的基礎上,闡述了如何基於FPGA設計和實現自適應頻率計的設計,並且給出了完整的設計過程,以及針對設計中應該注意的問題加以說明。其外,如果使用更高頻率的FPGA晶元,頻率計的量程上限可以進一步的提高。

[admin via 研發互助社區 ] 基於FPGA自適應數字頻率計的設計已經有2929次圍觀

http://cocdig.com/docs/show-post-43147.html