Quartus II是Altera 公司單晶元可編程系統(SOPC) 設計的綜合性環境,也是適合SOPC的最全面的設計環境。它擁有現場可編程門陣列(FPGA) 和複雜可編程邏輯器件(CPLD) 設計的所有階段的解決方案。與原來的Max + plus II相比,Quartus II 在界面和功能上都發生了不少變化,除承接了原來Max + plusII的全部設計功能和器件對象外,還增加了許多新功能,如支持Max + plusII界面,支持RTLView 等,還增加了新的FPGA 器件系列,包括一些適用於SOPC開發的大規模器件。

本文以Quartus II 4.0 為設計平台,以FPGA 為核心,設計了一個具體數字系統即帶計時器功能的秒錶系統,使用Quartus II 4.0 的綜合器和模擬器對系統進行了編譯和模擬,得出了正確的模擬結果。

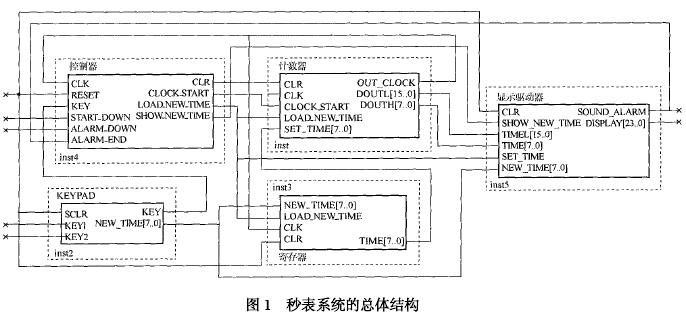

1 秒錶系統總體結構

要設計一個帶計時器功能的秒錶,計時範圍為0.01 s~1 h ,計時器初值以min 為單位,最長計時時間為59 min。總體結構包括以下幾個組成部分:

a) 顯示屏,由6 個七段數碼管組成,用於顯示計時時間。

b) 輸入數字鍵,用於設置計時器的計時時間(以min 為單位,不超過1 h) 。

c) START 鍵,用於啟動秒錶計時。

d) RESET 鍵,用於計時清零(複位) 。

e) ALARM 鍵,用於啟動秒錶的計時器功能。

f) 揚聲器,在計時器計時結束時發聲報警。

設計的總體結構圖如圖1 所示,主要顯示了內部連接關係。

1.1 秒錶系統控制器

控制器外部埠如圖1 所示。各埠的功能如下:

a) CLK為外部時鐘信號,RESET 為複位信號。

b) 當KEY為高電平( KEY= 1) 時,表示用戶按下數字輸入鍵。

c) 當START-DOWN 為高電平時,表示用戶按下“START”鍵。

d) 當ALARM-DOWN 為高電平時,表示用戶按下“ALARM”鍵。

e) ALARM-END 為計數器送來的計時完成信號,為高電平時表示計時結束。

f) CLR 為提供給計數器的複位信號。

g) 當CLOCK-START 輸出為高電平時,控制時鐘計數器開始計時。

h) 當LOAD-NEW-TIME 輸出為高電平時,控制寄存器下載新的計時時間。

i) 當SHOW-NEW-TIME 輸出為高電平時,控制顯示電路顯示新的時間值。

控制器的功能可以通過有限狀態自動機( FSM)的方式來實現。根據設計要求及埠設置,需要4 個狀態來實現:

a) S0 :電路初態即等待狀態。

b) S1 :秒錶工作狀態即正常計時狀態。完成上述埠功能a 的工作,在狀態S1 時用戶按下START 鍵後進入此狀態。

c) S2 :接收鍵盤輸入狀態。在狀態S0 或狀態S1時用戶按下數字輸入鍵後進入此狀態,此時將接收到的鍵盤輸入信息在七段數碼管上顯示。

d) S3 :計時器工作狀態。在狀態S2 時用戶按下ALARM鍵後進入此狀態,當計時完成後返回狀態S0。

相應的狀態轉換及控制如表1 所示。

1.2 秒錶系統時間計數器

根據設計需要,要設計一個計時範圍為0.01s~1 h 的秒錶,命名為CLOCK。首先需要獲得一個比較精確的計時基準信號,這裡是周期為1/100 s 的計時脈衝。其次,除了對每一計數器需設置清零信號CLR輸入外,還需在6 個計數器設置時鐘使能信號,即計時允許信號ENA ,以便作為秒錶的計時啟停控制開關。

另外,為了完成計時器功能,需要一個控制減法計數功能的計時使能信號SET-TIME ,以作為計時器的啟停控制開關。因此,秒錶可由1 個分頻器(用來提供計時基準信號) 、4 個十進位計數器(1/100 s ,1/10 s ,1 s ,1min) 以及2 個六進位計數器(10 s ,10 min) 組成。各部分組裝完成後的時間計數器的外部埠如圖1 所示。

各埠的功能如下:

a) CLR 為複位信號,CLK 為外部輸入的時鐘信號。

b) CLOCK-START 為高電平時,啟動秒錶計時。

c) LOAD-NEW-TIME 為高電平時,表示啟動計時器計時。

d) SET-TIME 為接收到的計時初始時間。

e) OUT-CLOCK為輸出給其他器件的時鐘信號,時鐘周期為1/100 s。

f) DOUTL 為輸出給顯示驅動器的低16 位信號。

g) DOUTH 為輸出給顯示驅動器的高8 位信號。

1.3 接收鍵盤輸入的緩衝器

緩衝器命名為KEYPAD。計時時間的輸入利用兩個按鍵分別代表1 min、10 min ,每按動一次,設置值加1 (相當於一個計數器,其最大值分別為9 、5) 。其外部埠如圖1 所示。各埠的功能如下:

a) SCLR 為複位信號。

b) KEY1 、KEY2 為接收到的鍵盤輸入信號,只有高電平和低電平兩種狀態。當輸入一個上升沿時,計數加1 。

c) KEY為高電平時,表示有按鍵按下。

d) NEW-TIME 為轉換后的計時時間。

1.4 顯示驅動器

本模塊的功能是:當SHOW-NEW-TIME 埠輸入信號有效(高電平) 時,根據NEW-TIME 埠輸入信號(時間數據) 在DISPLAY 埠輸出該信號。當SHOW-NEW-TIME 埠輸入信號無效(低電平) 時,根據TIME 埠的輸入信號判斷輸出。其外部埠如圖1 中所示。各埠的功能如下:

a) CLR 為複位信號。

b) SHOW-NEW-TIME 為顯示控制信號,為高電平時DISPLAY 的高8 位輸出由埠NEW-TIME 引入的信號,為低電平時輸出由TIME 引入的信號。

c) TIMEL 為由時間計數器引入的低16 位信號。

d) SOUND-ALARM 為高電平時,表示在計時器狀態下計時結束。

1.5 計時時間寄存器

本模塊的功能是在時鐘上升沿同步下, 根據LOAD-NEW-TIME 埠的輸入信號控制TIME 埠的輸出,當控制信號有效(高電平) 時,把NEW- TIME埠輸入的信號值輸出。其外部埠如圖1 所示。各埠的功能如下:

a) CLR 為複位信號,對TIME 埠的輸出進行非同步清零複位。

b) LOAD-NEW-TIME 為輸出控制信號,為高電平時,TIME 埠將輸出由埠NEW- TIME 引入的信號(時間數據) 。

c) TIME 為輸出埠,輸出時間數據。

1.6 整體組裝

前面已經完成了秒錶系統各個組成部分的設計,下面把這些部分組裝起來,形成完整的總體設計。命名為TIMES ,其外部埠如圖2 所示。

圖2 秒錶系統的外部埠

各個輸入輸出埠的功能如下:

a) CLK為外部時鐘信號,CLR 為複位信號。

b) START 為高電平時,表示用戶按下START鍵,秒錶計時啟動。

c) ALARM 為高電平時,表示用戶按下ALARM鍵,用於確定新的計時器時間設置。

d) SET-KEY1 和SET-KEY2 ,用於接收用戶輸入的時間數據。

e) DISPLAY 實際上表示了6 個七段數碼顯示管,用於顯示時間。

f) SOUND-ALARM-OUT 為高電平時,驅動揚聲器發聲,表示計時結束。

2 Quartus II4.0 的秒錶系統整體模擬

以上完成了秒錶系統的VHDL 設計。下面使用Quartus II4.0 對本設計進行編譯和模擬。首先創建工程,使用文本編輯器輸入本設計的所有模塊的源程序,把TIMES.VHD 設為頂層文件。把本設計中的所有設計文件添加進工程后,先對每個模塊進行編譯糾錯,然後進行全程編譯,通過之後就可以進行模擬。每一部分的模擬從略,下面只說明系統的整體模擬波形。

系統工作在秒錶功能時的模擬波形如圖3 所示。

圖3 系統秒錶功能的模擬波形

圖中,START 為高電平時,表示用戶按下了START鍵,秒錶開始計時。這裡把輸出的DISPLAY 信號分成了6 組,每組代表秒錶上的1 位。由於DISPLAY0代表的是最低位,也就是百分之一秒,所以顯示不清晰。當接收到一個RESET 信號的高電平后時間清零,RESET 恢復低電平后,由於START 信號仍然為高電平,秒錶重新開始計時。

系統工作在計時器功能時的模擬波形見圖4 。

圖4 系統計時器功能時的模擬波形圖

SET-KEY1 ,SET-KEY2 脈衝代表用戶按下了數字輸入鍵,有幾個正脈衝就顯示數字幾。開始時START先變為高電平,系統開始秒錶計時;圖中所示0.21 s后SET-KEY1 來了正脈衝,秒錶由顯示驅動器驅動顯示正在設置的計時時間。之後,ALARM 鍵變為高電平,計時器開始工作。由圖中可看出,用戶設置的計時時間為43 min ,按下ALARM 鍵后,系統開始倒計時。

3 結束語

我們根據秒錶系統的設計要求,把整個系統分成了幾個模塊來進行設計,並通過VHDL 語言完成了具體程序的編寫,使用Quartus II 4.0 對系統進行了分析、綜合,編譯、模擬等工作,通過整體模擬,可以看出完成後的系統滿足設計要求。整個設計充分利用了Quartus II4.0 的設計優勢,簡潔靈活,便於修改。

[admin via 研發互助社區 ] 基於Quartus II的帶計時器功能的秒錶系統設計已經有6852次圍觀

http://cocdig.com/docs/show-post-43141.html