在系統編程(ISP)器件是在20世紀90年代出現的最先進的可編程器件,它無須編程,可通過PC機經下載電纜直接對安裝在用戶目標版上的ISP器件重複編程,實現系統重構,它給電子產品的設計和產生帶來了革命性的變化。

ISP synario System是Lattice半導體公司的ispLSI系列器件的開發軟體,軟體內除了基本邏輯器件庫外,還有一個較為完善的宏(MACRO)器件庫,每一個宏器件是一組預先編好存放在庫中的邏輯方程,它代表一個邏輯模塊,設計時可作為邏輯器件調用。充分利用宏器件可以使邏輯設計大大簡化。

在進行複雜邏輯系統設計時,可以將整個系統劃分為若干模塊,而每個模塊還可劃分為若干子模塊,設計時可由底層模塊開始向上逐級設計、調試(或模擬),最後進行頂層組裝調試。邏輯系統中的子模塊可以直接用ABEL-HDL語言編輯,也可直接由電路圖編輯而成。以下簡要介紹利用ispLSI1032E器件構成的數字鐘控系統。

1 數字鐘控系統的基本結構

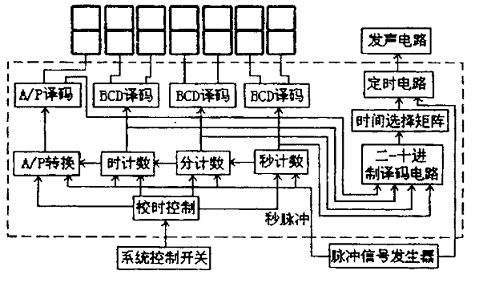

數字鐘控系統結構框圖如圖1所示,數字鐘部分由秒、分、時計數電路,上、下午(A/P)轉換電路,解碼顯示電路以及校時電路等組成。七隻LED數碼管分別顯示上、下午和時、分、秒。鍾控部分由二—十進位譯電路,時間選擇矩陣電路,定時電路以及發聲電路等組成。脈衝信號發生器提供秒脈衝和發聲高頻振蕩源。整個系統除了系統控制開關、脈衝信號發生器、發聲電路以及LED數碼管外,其餘部分(如虛線框內所示)全部在一片ispLSI1032E內實現。

圖1 數字鐘控系統結構框圖

2 數字鐘在ispLSI1032E內的實現

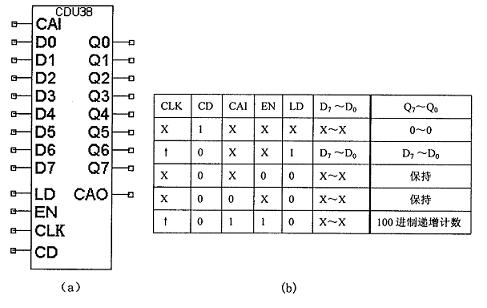

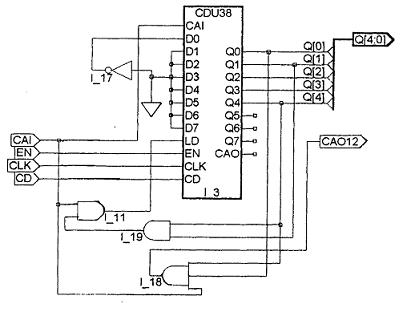

數字鐘內核心部分是時、分、秒計數器,選用宏器件中的兩位十進位遞增計數器CDU38分別構成時、分、秒計數器。CDU38是一個由ABE-HDL語言編輯的兩位十進位遞增計數器,其邏輯符號及功能表如圖2所示。輸出端:Q7~Q0以8421BCD碼形式輸出兩位十進位數,CAO為進位輸出端。輸入端:CLK為脈衝輸入端(上跳沿觸發),CD為清零端,CAI為進位輸入(計數容許)端,EN為選片使能端,LD為同步置數控制端,D7~D0為置數輸入端。可以通過“反饋置數”方式利用宏器件CDU38組成100以內的任意進位計數器。

圖2 宏器件CDU38的邏輯符號(a)和功能表(b)

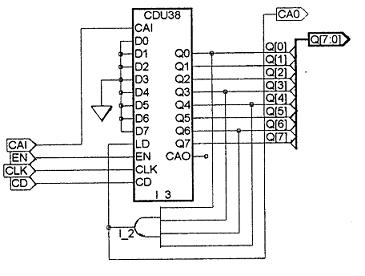

2.1 秒計數模塊

秒計數器為一60進位遞增計數器,將CDU38的輸出端Q6、Q4、Q3、Q0通過與門2控制置數控制端LD,因為置數輸入端D7~D0全部接“地”,所以當計數器從0計數至59時,LD端為高電平,為置數做好準備。同時進位輸出CAO(取自LD端)也為高電平,可用做高位計數器的級連信號。當第60個脈衝到來時,計數器置零,實現60進位計數。秒計數器子電路如圖3所示,圖中輸出端Q7~Q0採用匯流排表示方式,其模塊符號見圖8數字鐘模塊中I-8。

圖3 秒計數器子電路

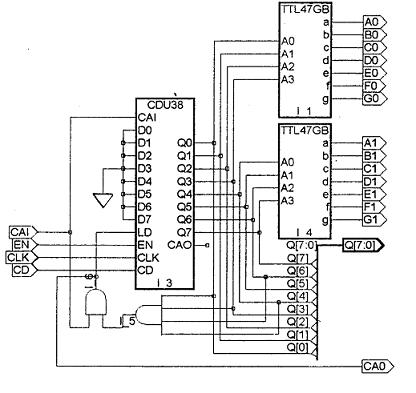

2.2 分計數模塊

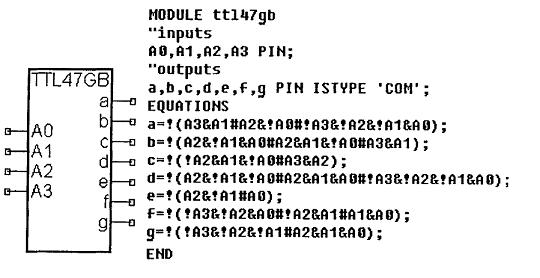

分計數器子電路如圖4所示,其模塊符號見圖8數字鐘模塊中I-7。分計數器也是一個60進位遞增計數器,其構成思路與秒計數器相同,不再贅述。在分計數子電路中為CDU38輸出端配接了兩個輸出高電平有效的BCD7段顯示解碼子模塊(TTL47GB),可直接驅動7段顯示LED數碼管。輸出高電平有效的BCD7段顯示解碼子模塊符號與用ABEL—HDL語言編寫的子程序如圖5所示。

圖4 分計數器子電路

圖5 BCD7段顯示解碼電路模塊符號與子程序

2.3 時計數模塊

時計數器子電路如圖6所示,其模塊符號見圖8數字鐘模塊中I-5。時計數器也是利用CDU38通過“反饋置數”方式構成。採用12小時計時制,Q4、Q1經與門I19和I11接止LD端,計數之間採用同步級連方式,當Q4和Q1為“1”且進位輸入端CAI(接分計數器進位輸出CAO)為高電平,此時對應時間為12時59分59秒,這時CDU38的LD端為高電平,而D7~D1接“地”,D0接高電平,因此在下一個秒脈衝到來之時,時計數器數值為01(分、秒計數器均為00),實現12進位計數。

圖6 時計數器子電路

與門I18的作用是當時間為為11時59分59秒時經CAO12端輸出一高電平,用來控制上下午(A/P)的轉換。

2.4 上下午(A/P)轉換模塊

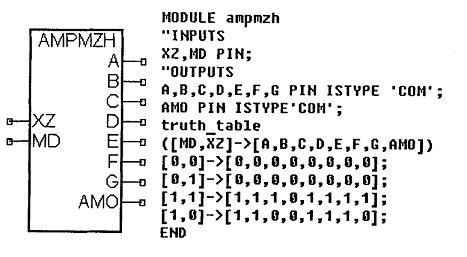

圖7為A/P轉換模塊符號與用ABEL-HDL語言編寫的子程序,模塊輸出端A~G直接與7段顯示LED數碼管相連,用來顯示A或P。數碼管顯示A時輸出端AMO為高電平,顯示P時為低電平,用於時間選擇控制。輸入端XZ控制A、P顯示,輸入高電平顯示A,低電平顯示P。MD為滅燈控制,當計時採用24進位時,MD接低電平,A~G輸出全部為“0”,實現滅燈。模塊輸入輸出邏輯關係如圖7真值表(truth_table)所示。

圖7 A/P轉換電路的模塊符號與子程序

2.5 數字鐘的組裝

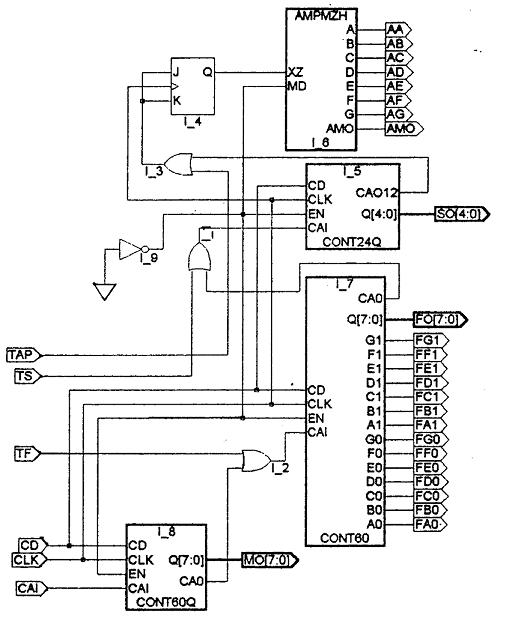

對秒、分、時計數模塊進行組裝后形成的數字鐘子電路如圖8所示,其模塊符號見圖11中I-2。秒、分、時計數器及A/P轉換電路之間採用同步級連方式,秒脈衝同時引入各計數器時鐘輸入端(CLK),利用低位計數器的進位輸出端(CAO)通過或門控制高位計數器計數容許端(CAI)。或門另一輸入端通過加高電平實現校時功能,TF、TS、TAP分別作為分、時、A/P的校對控制端。

圖8 數字鐘子電路

3 時控系統的設計

時控系統由二一十進位解碼電路、時間選擇矩陣組成。

3.1 二—十進位解碼電路

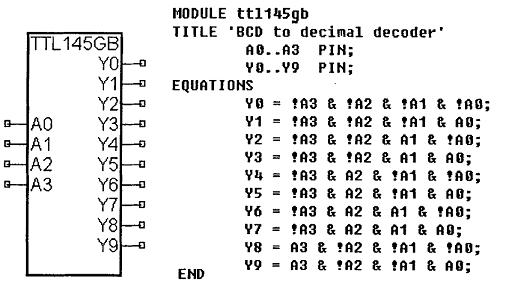

二—十進位解碼電路採用ABEL-HDL語言編寫而成,其輸入端(A0~A3)接計數器輸出的8421BCD碼,輸出端Y0~Y9各對應一組輸入BCD碼,高電平有效,其電路模塊符號與子程序如圖9所示,用來實現時間選擇。

圖9 二—十進位解碼電路的模塊符號與子程序

3.2 時間選擇矩陣

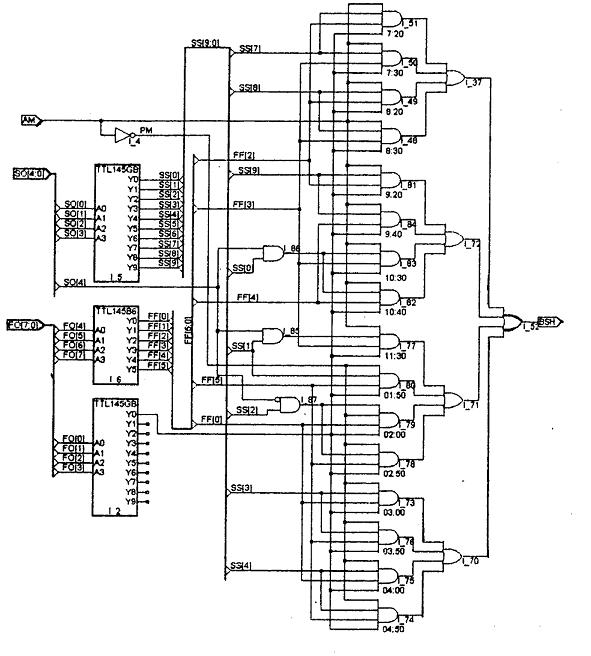

時間選擇矩陣子電路如圖10所示,其模塊符號見圖11鍾控系統中I-1。子電路的輸入端FO[7:0]分別接時鐘分計數器輸出端Q7~Q0,SO[4:0]分別接時計數器輸出Q4~Q0,輸入端AM接A/P轉換電路的輸出端AMO,用“1”和“0”狀態來區別上、下午。利用AM配合時、分解碼器的輸出,經與門進行選擇,可選定24小時內任意時刻(本電路只選擇到分)。圖10中人的時間選擇矩陣是一個學校上下課自動打鈴系統,各與門所選擇的時間如圖所示,與門輸出經或門處理后通過輸出端BSH啟動打鈴系統。

圖10 時間選擇矩陣子電路

圖11 鍾控系統

4 數字鐘控系統構成

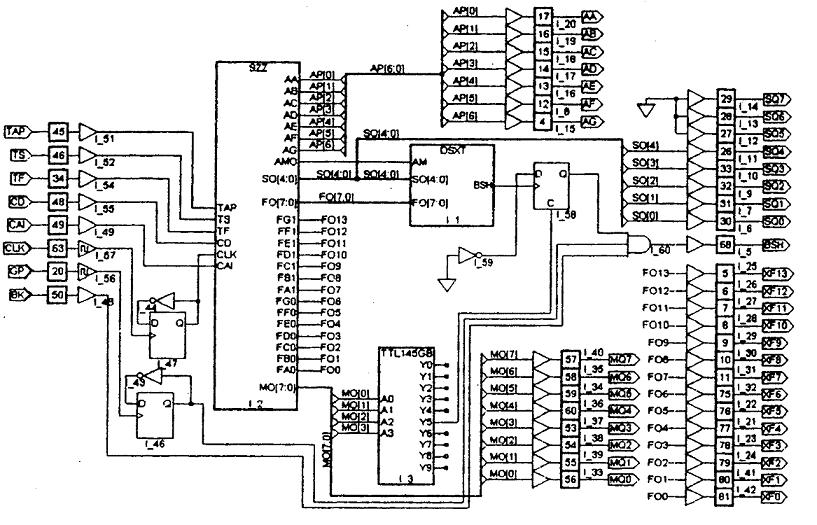

在ISP Synario System原理圖編輯窗口中將數字鐘與時間選擇矩陣連接后構成的鐘控系統如圖11所示。將輸入、輸出端定義完畢,對系統進行編譯並形成JED文件,然後下載到晶元ispLSI1032E-70PLCC84中。

輸入端TAP、TS和TF通過外加高電平實現A/P、時、分校正,CD和CAI通過外加高電平實現清零和計時容許控制。系統由CLK端輸入2Hz脈衝經D觸發器I47分頻,產生秒脈衝供數字計時。由GP端輸入高頻脈衝信號經D觸發器I46分頻在與門I60控制下推動揚聲器發聲。BK端通過輸入高電平選通與門I60實現發聲控制端。輸出端MQ7~MQ0通過兩片74LS48驅動兩隻7段顯示數碼管作秒顯示。XF13~XF0直接驅動兩隻數碼管作分顯示。SQ7~SQ0通過兩片74LS48驅動兩隻數碼管作時顯示。輸出端AA~AG驅動一隻數碼管做A/P顯示。用BSH端定時輸出高頻脈衝經功放電路驅動揚聲器發聲模擬打鈴。

系統上電后,首先將數字鐘校準,BK端輸入高電平,當選定時刻到來時時間選擇矩陣I1輸出端BSH由低電平上跳為高電平,D觸發器I58輸出高電平,選通與門I60,揚聲器發聲。發生持續時間由二—十進位解碼I3設定,本系統設定時間為5秒,當發聲時間持續至5秒時,Y5端輸出低電平,關閉與門I60,發聲停止。

5 結束語

以上介紹了利用CPLD器件ispLSI1032E採用在系統編程技術構成數字鐘控系統的基本過程,本系統在東南大學SE-3型ISP數字實驗機上通過模擬實驗,只要設計出印刷電路板即可使該系統成為實際產品。實踐證明,在系統編程技術與新型可編程邏輯器件的結合,可以將一個複雜的數字系統大部分功能在一片CPLD器件內實現,這不僅簡化了數字系統的設計過程,而且大大減少了系統所用器件的數量,提高了系統的可靠性與性價比。

[admin via 研發互助社區 ] 用CPLD實現的數字鐘控系統已經有3247次圍觀

http://cocdig.com/docs/show-post-43075.html