信號發生器在電子測量和自動控制領域應用十分廣泛,常用的信號發生器大多由模擬電路構成,由於電路複雜、調試麻煩且精度低等缺點,一些複雜模擬電路已被數字電路所代替。隨著計算機軟、硬體的發展,計算機與外設之間的數據通信越來越頻繁,也越來越便利,虛擬儀器應運而生。本文介紹基於SOPC實現的函數信號發生器部分原理。

1 SOPC的簡介

SOPC技術是美國Altrea公司於2000年最早提出的,並同時推出了相應的開發軟體Quartus II。SOPC是基於FPGA解決方案的SOC, SOPC的設計是以IP為基礎的,以硬體描述語言VHDL為主要設計手段,藉助於以計算機為平台的EDA工具進行的。與傳統的專用集成電路設計技術相比, SOPC的設計全程,包括電路系統描述、硬體設計、模擬測試、綜合、調試、系統軟體設計,直至整個系統的完成,都由計算機完成。其設計技術直接面向用戶,使系統級專用集成電路的實現有了更多的途徑,即除傳統的ASIC器件外,還能通過大規模FPGA等可編程器件來實現。

SOPC設計包括以32位Nios軟核處理器為核心的嵌入式系統的硬體配置、硬體設計、硬體模擬、軟體設計、軟體調試等。SOPC系統設計的基本軟體工具主要有: Quartus II,用於完成Nios系統的綜合、硬體優化、適配、編程下載和硬體系統測試; SOPCbuilder是Altera Nios嵌入式處理器開發軟體包,用於實現Nios系統的配置、生成、Nios系統相關的監控和軟體調試平台的生成; ModelSim用於對SOPCBuilder生成的Nios的HDL描述進行系統功能模擬;Matlab/DSP Builder,可藉助於生成Nios系統的硬體加速器,進而為其定製新的指令; GNU Pro用於進行軟體調試。

2 函數信號發生器的設計步驟與實現

(1)設計步驟

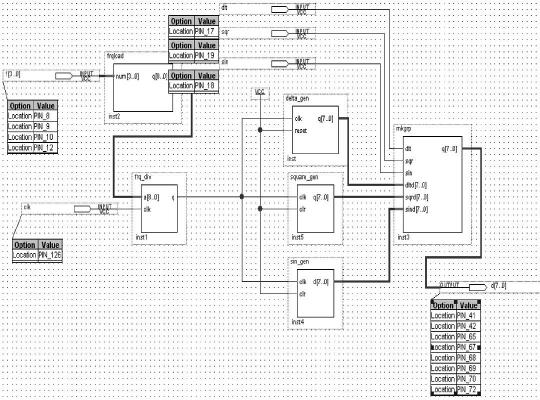

用VHDL語言結合原理圖設計實現一個函數信號發生器,輸出正弦波、方波和三角波三種波形。將頻率控制、分頻、三角波、正弦波、方波發生各個模塊分別用VHDL語言編程為一個子程序,並把每一個模塊轉換成圖形文件,然後在原理圖編輯框調用這些圖形模塊,連接電路如圖1所示。通過按鍵1到按鍵4控制頻率調節f〔3...0〕,用按鍵6、按鍵7、按鍵8控制dlt、sin、sqr波形選通,最後把八位輸出接DAC0832通過D/A轉換,從示波器上就能看到波形輸出。按下不同的按鍵輸出不同的波形及頻率。

(2)原理實現

frqload.vhd:把四位頻率控制字f〔3...0〕轉換為相對應的整數輸出q,用於分頻計數使用;

frq_div.vhd:把輸入的時鐘CLK進行分頻,對分頻計數a逐次減一,當分頻計數a被減到零時,給出一個輸出q;作為三角波模塊(delta_gen)、方波模塊(square_gen)、正弦波模塊(sin_gen)的時鐘clk,實現了對輸入時鐘CLK的a分頻。delta_gen.vhd:設定一個變數num,定義其範圍為“00000111”到“11111000”,每到一個脈衝,分別對它進行+8或-8,然後把改變后的num送到輸出q,生成了三角波信號。

square_gen.vhd:設定一個變數num,每到一個脈衝,檢測它是否小於512,若小於512,則把高電平送到輸出,並對num+1,否則就輸出低電平,並賦值num為0,生成了方波信號。

sin_gen.vhd:通過定義正弦數據表,每到一個脈衝,逐次查找並輸出相應的正弦數據,生成了正弦波形。

mkgrp.vhd:用於控制輸出波形的選通,若只有sin輸入高電平,則輸出正弦波,以此類推,假若同時有dlt和sin都輸出高電平,則輸出波形時三角波和正弦波的疊加,依此類推。

下面是用VHDL語言編程的三角波信號的程序。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity delta_gen is

port (clk, reset: in std_logic;

q: out std_logic_vector (7 downto 0));

end delta_gen;

architecture a of delta_gen is

begin

process (clk, reset)

variable num: std_logic_vector (7 downto 0);

variable ff: std_logic;

begin

if reset='0' then

num: =" 00000000";

elsif clk'event and clk='1' then

if ff='0' then

if num=" 11111000" then

num: =" 11111111";

ff: ='1';

else

num: =num+8;

end if;

else

if num=" 00000111" then

num: =" 00000000";

ff: ='0';

else

num: =num-8;

end if;

end if;

end if;

q<=num;

end process;

end a;

圖1 連接電路

3)具體實現過程

編譯程序,通過編譯進入模擬階段。設CLK為1ns,只有sin為高電平,輸出是用邏輯八位表示的正弦波的波形數據。

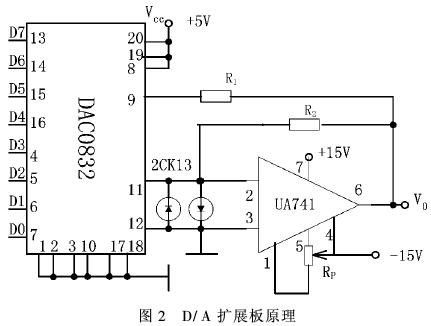

引腳鎖定,選用GW48-SOPC系統,目標晶元為ACEX1K系列EP1K30TC144-3,用模式5,並對八位的邏輯輸出進行D/A轉換,圖2為D/A擴展板原理圖(圖中R1= 10kΩ, R2= 50kΩ, Rp=15kΩ)。

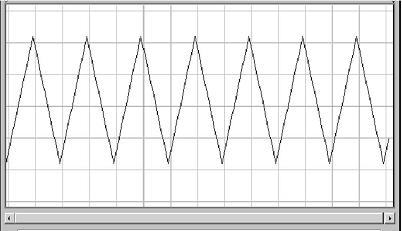

在Quartus II中,通過菜單Assignments Editor項進入引腳鎖定編輯器,主時鐘CLK接Clock0 (第126引腳),用鍵1、鍵2、鍵3、鍵4控制四位頻率,接PIO0-PIO3,相應的引腳為8、9、10、12。用鍵6、鍵7、鍵8控制波形輸出的選通dlt、sin、sqr,對應的引腳為18、19、20。把輸出邏輯八位接系統板上的D/A轉換,即PIO24-PIO31,對應的引腳為41、42、65、67、68、69、70、72。將這些信息輸入引腳編輯器存儲后,必須再編譯一次才能將引腳鎖定信息編譯進編程下載文件中。將編譯產生的SOF格式下載文件配置進FPGA中,下載成功后即可進行硬體測試。通過GW48-SOPC系統上的模式選擇鍵進行模式選擇,連接示波器觀察輸出波形。圖3為函數信號發生器輸出的三角波。

圖3 函數信號發生器輸出的三角波

3 總結

(1)輸出信號頻率的高低由頻率字和參考頻率等決定外,另一個因素是D/A的轉換速度。FPGA的速度與D/A相比要快得多,所以真正決定輸出信號頻率的因素是D/A的速度。

(2)上面提供的程序在GW48—SOPC實驗開發系統中測試通過,產生的信號穩定,頻率連續可調。輸入頻率接實驗板上CLKO的50MHz以上時,波形幾乎沒有失真,且正弦波和三角波所要求的頻率與方波要求的頻率不完全相同,必須通過按鍵控制頻率輸出,為不同的波形提供不同的頻率,使其波形更完美。

[admin via 研發互助社區 ] 基於SOPC的函數信號發生器的設計已經有2644次圍觀

http://cocdig.com/docs/show-post-43071.html